Fターム[5F140AC16]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | その他の特殊動作(パンチスルーTr、磁気) (47)

Fターム[5F140AC16]に分類される特許

1 - 20 / 47

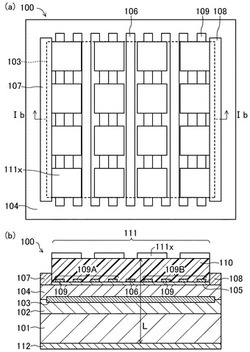

テラヘルツ波素子

【課題】テラヘルツ波を発生又は検出するテラヘルツ波素子において、単色性が良いテラヘルツ波を効率良く出射する。

【解決手段】テラヘルツ波素子は、基板101の上に形成された第1の半導体層102と、第1の半導体層102の上に形成された第2の半導体層104と、第2の半導体層104の上に形成されたゲート電極106と、第2の半導体層104の上にゲート電極106を挟んで対向するように形成されたソース電極107及びドレイン電極108と、第2の半導体層104の上におけるゲート電極106とソース電極107との間及びゲート電極106とドレイン電極108との間に形成され、複数の金属膜109が周期的に配置された周期構造を有する周期金属膜109A,109Bと、ゲート電極106及び複数の金属膜109の上方に配置された第1のミラー111と、基板101の下に形成された第2のミラー112とを備えている。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

トンネルトランジスタの製造方法

【課題】1回のリソグラフィ工程によりセルフアラインでトンネルトランジスタを製造する方法を提供する。

【解決手段】ゲート絶縁膜及びゲート電極が積層された半導体基板上に第1の絶縁膜を形成しリソグラフィにより第1の絶縁膜の端部に第1の絶縁膜とは薬品選択性が異なりゲート電極位置を画定する第2の絶縁膜を形成する工程と、第1及び第2の絶縁膜をマスクにゲート電極の一端を画定する工程と、第1及び第2の絶縁膜をマスクにして第1導電型不純物を半導体基板に導入しソースを形成する工程と、半導体基板全面に第1の絶縁膜とは薬品選択性が異なる第3の絶縁膜を被覆する工程と、該第3の絶縁膜の一部を除去することにより該第1の絶縁膜を選択的に除去する工程と、第2及び第3の絶縁膜をマスクにしてゲート電極を形成した後、第2導電型不純物を半導体基板に導入しドレインを形成する工程を含むトンネルトランジスタの製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】消費電力が低く、かつ、動作時の電流値が高い半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は、第1導電型の基板上のソース領域に形成された第2導電型の第1の不純物拡散層と、前記基板上のポケット領域に形成された第1導電型の第2の不純物拡散層と、前記基板上のドレイン領域に形成された第1導電型の第3の不純物拡散層と、前記第1乃至第3の不純物拡散層の表面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲートと、を含む。前記ポケット領域は前記ソース領域に隣接し、リセスを有するように形成される。前記ゲートは、前記ゲート絶縁膜を介して前記リセスを埋め込むように前記ゲート絶縁膜上に形成される。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

半導体装置

【課題】 従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、高感度のホール素子に発生するホール電圧VHにより検出する。

【解決手段】 アースラインに向かって配線されたソース配線層8の一部をN型層1に形成したトレンチ20内に配設する。これによりトレンチ20内に配設されたソース配線層8a近傍のN型層1に発生する磁束密度Bを高める。この高い磁束密度Bが発生しているトレンチ20内のソース配線層8a近傍のN型層1を横切るホール電流IH成分を増やし、ホール素子Hに発生するホール電圧VHを高くする。このように、高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

バリスティックMOSトランジスタ

【課題】

界面散乱が増加し、バリスティック伝導が生かせなくなる現象を抑制し、大きなドレイン電流を供給できるバリスティックMOSトランジスタを提供する。

【解決手段】

バリスティックMOSトランジスタは、複数のソース側チャンネル領域と、複数のソース側チャンネル領域に連続し、ソース側チャンネル領域のチャンネル幅の和より大きいチャンネル幅を有する1つのドレイン側チャンネル領域と、複数のソース側チャンネル領域に接続されたソース領域と、ドレイン側チャンネル領域に接続されたドレイン領域と、ソース側チャンネル領域、ドレイン側チャンネル領域の表面上に形成されたゲート絶縁膜とその上のゲート電極とを有するMOSゲート電極構造と、を有し、ソース側チャンネル領域と前記ドレイン側チャンネル領域の和の長さが50nm以下であり、バリスティック伝導を生じる。

(もっと読む)

半導体素子

【課題】より大きな電流ノイズを容易に発生させることが可能な半導体素子を提供する。

【解決手段】本発明に係る半導体素子100は、所定の物質により形成されるゲート電極101と、ゲート電極の少なくとも一部を覆うように所定の誘電体を用いて形成されるゲート絶縁膜103と、ゲート絶縁膜上に不純物及び/又は欠陥によるトラップを有する化合物を用いて形成されるチャネル形成領域105と、チャネル形成領域の端部に形成されるソース107/ドレイン109と、を備え、チャネル形成領域の幅は、不純物及び/又は欠陥によるトラップを有する化合物のデバイ長とする。

(もっと読む)

半導体装置およびその製造方法

【課題】所望の位置に不純物領域を精度よく形成することのできる半導体装置およびその製造方法を提供する。

【解決手段】ショットキーバリアダイオードの製造方法は、n型SiC層10を形成する工程と、n型SiC層10の表面にトレンチ30を形成する工程と、トレンチ30を形成する工程の後で、n型SiC層10の表面にケイ素と窒素とを供給した状態でn型SiC層10を熱処理する工程とを備えている。

(もっと読む)

半導体装置

【課題】半導体装置において、面積の増大を招くことなく高い電流能力を得ることができる高耐圧MOSトランジスタの構造を提供する。

【解決手段】例えば高耐圧P型MOSトランジスタ構造では、低濃度N型拡散領域108の上において、ゲートGの右方及び左方に、低濃度P型拡散領域109が形成され、その上に高濃度P型拡散領域106が形成される。前記高濃度P型拡散領域106の内方には、高濃度N型拡散領域104が形成され、このN型拡散領域104は、コンタクト107を介してその上層のソース又はドレイン領域113、114に接続される。前記高濃度P型拡散領域106には、コンタクト107は形成されない。前記ゲートGの近傍には、前記低濃度N型拡散領域108と、前記低濃度及び高濃度N型拡散領域109、106と、高濃度N型拡散領域104とにより寄生バイポーラトランジスタ203、204が形成される。

(もっと読む)

スピントランジスタ及び半導体メモリ

【課題】ソース電極とドレイン電極の磁気抵抗変化率が十分大きなスピントランジスタ及びこのようなスピントランジスタを使用した半導体メモリを提供する。

【解決手段】本発明に係るスピントランジスタ1は、強磁性体からなるソース電極層Sと、強磁性体からなるドレイン電極層Dと、ソース電極層S及びドレイン電極層Dが設けられ、ソース電極層Sにショットキー接触した半導体SUBと、半導体SUB上に直接又はゲート絶縁層GIを介して設けられたゲート電極層GEと、半導体SUB上にソース電極層Sを介して設けられ、ソース電極層Sを構成する強磁性体の磁化方向SMと同方向にスピン偏極した電子emを注入するスピンフィルタ層Fとを備えることを特徴とする。

(もっと読む)

半導体装置及びその駆動方法

【課題】低電源で駆動でき、しかも高利得が得られる半導体装置及びその駆動方法を提供する。

【解決手段】第1半導体領域11及び第2半導体領域10が接合面30a,30bで隣り合い、電位障壁を構成するpn接合体と、前記接合面の近傍で前記第1半導体領域11に絶縁体12を介して接続される第1電極22と、前記第1半導体領域11に接続される第2電極21と、前記第2半導体領域に接続される第3電極20と、を備える。前記第2電極21と前記第3電極20との間に順方向バイアスを印加すると、前記接合面に対応して前記電位障壁が低下する。前記第1電極22と前記第2電極21との間に電位差を与えることにより、前記電位障壁が変化し、前記第1半導体領域11は、前記絶縁体13との境界の表層に、表面近傍領域が、駆動電流を流すチャネル31として形成される。その結果、半導体装置は、トランジスタとして駆動され得る。

(もっと読む)

スピンFET及び磁気抵抗効果素子

【課題】素子抵抗の低抵抗化とMR比の向上とを同時に実現する。

【解決手段】本発明の例に係るスピンFETは、ソース・ドレイン部に、少なくとも半導体基板11/トンネルバリア12/低仕事関数材料13/強磁性体14からなる積層構造を有し、低仕事関数材料13は、未酸化のMg,K,Ca,Scのうちの1つ、又は、その1つを原子数比で50%以上含む合金から構成される。

(もっと読む)

半導体装置

【課題】半導体装置のインパクト・イオン化を利用して導通させる場合の電圧を低下し、しかも良好なスイッチング特性を有する半導体装置を提供する。

【解決手段】ソース101、ドレイン102、ソース101、ドレイン102間に設けられたI領域I、I領域I上にゲート酸化膜104を介して設けられるゲート電極105と備えたSiを基板とする半導体装置において、I領域Iに、少なくともゲルマニウムを含むエピタキシャル成長層103を選択的エピタキシャル成長によって形成する。

(もっと読む)

スピンFET、磁気抵抗効果素子及びスピンメモリ

【課題】スピンFET/スピンメモリの低消費電力と高信頼性を実現する。

【解決手段】本発明の例に係るスピンFETは、第1ソース/ドレイン領域11a-1上に配置され、磁化方向が膜面に対して垂直方向となる上方向又は下方向に固定される第1強磁性膜12と、第2ソース/ドレイン領域11a-2上に配置され、磁化方向が上方向又は下方向に変化する第2強磁性膜13と、第2強磁性膜13上に配置される反強磁性強誘電膜15と、第1ソース/ドレイン領域11a-1と第1強磁性膜12との間及び第2ソース/ドレイン領域11a-2と第2強磁性膜13との間の少なくとも1つに配置されるトンネルバリア膜20,21とを備える。反強磁性強誘電膜15の抵抗は、第1及び第2ソース/ドレイン領域11a-1, 11a-2がチャネル領域11cを介して導通したときのオン抵抗よりも大きい。

(もっと読む)

接点装置およびスイッチ装置

【課題】アーク生成物や接点金属粉の飛散等が無く、性能を長期に維持することができる接点装置を提供すること。

【解決手段】本接点装置2は、共に同じ導電型の半導体領域からなる一対の接点領域10,10と、両接点領域10,10間に介在する半導体領域から構成された制御領域12と、上記制御領域12に向けてプラスマイナスの電界を選択的に発生可能に配置された電界発生体6と、を備える。

(もっと読む)

縦型スピントランジスタ及びその製造方法

【課題】トランジスタ及びその製造方法に関して、新たな構造のスピントランジスタ及びその製造方法を提案すること。

【解決手段】磁性体で形成された層を含んでいる第1のソースドレイン層と;前記第1のソースドレイン層上に形成されており、半導体で形成された層を含んでいる、チャネル層と、前記チャネル層上に形成されており、磁性体で形成された層を含んでいる、第2のソースドレイン層と、を含む突起構造と;前記チャネル層の側面に形成されたゲート絶縁膜と;前記ゲート絶縁膜の表面に形成されたゲート電極と;を具備することを特徴とする縦型スピントランジスタ。

(もっと読む)

1 - 20 / 47

[ Back to top ]