Fターム[5F140BA02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | SiC (638)

Fターム[5F140BA02]に分類される特許

621 - 638 / 638

半導体装置の製造方法

【課題】 III族窒化物半導体層を用いた半導体装置において、熱的安定性に優れ、且つリーク電流が少ない高抵抗領域を容易に形成する。

【解決手段】 III族窒化物半導体層における素子形成領域を分離させる絶縁酸化膜を形成する半導体装置の製造方法は、III族窒化物半導体層よりなる堆積層11における素子形成領域を区画するように、堆積層11にIII族窒化物半導体層の改質領域13を形成する工程と、改質領域13を酸化することにより、酸化領域14を形成する工程とを備える。

(もっと読む)

移動度を半導体素子において増加させる方法及び装置

トランジスタのチャネル領域における移動度の増大を実現する方法及び装置が提示される。一の実施形態では、チャネル領域(18)は2軸応力が発生する基板の上に形成される。ソース領域(30)及びドレイン領域(32)は基板の上に形成される。ソース領域及びドレイン領域は1軸応力を2軸応力発生チャネル領域に追加する形で発生させるように作用する。1軸応力及び2軸応力はPチャネルトランジスタに関しては共に圧縮応力であり、そしてNチャネルトランジスタに関しては共に引っ張り応力である。その結果、キャリア移動度が短チャネルトランジスタ及び長チャネルトランジスタの両方に関して増加する。両方のタイプのトランジスタを同じ集積回路に搭載することができる。  (もっと読む)

(もっと読む)

非対称半導体装置の性能を向上させる方法及び装置

半導体デバイスの性能が向上する方法及び装置が提供される。一実施形態において、第1の電流領域(64、76、23)、チャンネル領域及び第2の電流領域(75、33、66)が互いに隣接している。第2の電流領域(75、33、66)は、第1の電流領域(64、76、23)における第1の元素の含有量より大きい合金の第1の元素の含有量を有し、第2の電流領域(75、33、66)は、チャンネル領域における第1の元素の含有量より大きい第1の元素の含有量を有している。さらに、合金は第2の元素を含み、第1の元素は第1の価電子数を有し、第2の元素は第2の価電子数を有している。さらに、第1の価電子数及び第2の価電子数の合計は8である。  (もっと読む)

(もっと読む)

非対称なヘテロドープされた高電圧のMOSFET(AH2MOS)

非対称なヘテロドープされた金属酸化物(AH2MOS)半導体デバイスは基板と、前記基板の頂部にあってソース領域とドレイン領域との間に配置された絶縁ゲートと、からなる。ゲートの一方の側面には、ヘテロドープされたタブ及びソース領域が形成されている。タブ領域は第2極性のドーパントを有している。ソース領域が各タブ領域内に配置されており、第2極性と反対の第1極性のドーパントを有している。ゲートの他方の側面には、ヘテロドープされたバッファ及びドリフト領域が形成されている。バッファ領域は第2極性のドーパントからなる。ドリフト領域がバッファ領域内に配置され、第1極性のドーパントによってドーピングされている。ドレインn+タップ領域がドリフト領域内に配置されている。  (もっと読む)

(もっと読む)

ウェハ接合によって製造される半導体−誘電体−半導体デバイス構造体

【課題】 デバイス性能を犠牲にすることなく様々なゲート材料の使用を可能にする、半導体基板上に少なくとも部分的にゲート・スタックを作るための技術を提供する。

【解決手段】 高k誘電材料を含む少なくとも1つの構造体のウェハ接合を利用して、半導体電子デバイスのためのゲート・スタックを形成する方法が提供される。本発明の方法は、まず、それぞれが主面を有する第1及び第2の構造体を選択するステップを含む。本発明によれば、第1及び第2の構造体の少なくとも一方又は両方は、少なくとも高k誘電材料を含む。次に、第1及び第2の構造体の主面同士を接合して、ゲート・スタックの高k誘電材料を少なくとも含む接合構造体を形成する。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

メモリデバイス、トランジスタ、メモリセル並びにそれらの製造方法

メモリデバイスはメモリセルのアレイと周辺デバイスを含んでいる。少なくとも一部の個別メモリセルはSiCを含む炭酸化部分を含んでいる。少なくとも一部の周辺デバイスは炭酸化部分を含まない。トランジスタは第1ソース/ドレーン、第2ソース/ドレーン、第1ソース/ドレーンと第2ソース/ドレーンとの間にSiCを含む半導体基板の炭酸化部分を含んだチャンネル、及びチャンネルの両側と作動式に関係するゲートを含んでいる。 (もっと読む)

半導体装置及びその製造方法

【課題】炭化珪素層に対する良好なコンタクトを確保しつつ、炭化珪素層に接続された電極の剥離を抑制する。

【解決手段】炭化珪素層11を有する半導体装置の製造方法であって、(A)炭化珪素層11の上に導電層21を形成する工程と、(B)導電層21と炭化珪素層11を反応させて、炭化珪素層11に接する反応層12およびシリサイド層23からなる合金層を形成する工程と、(C)シリサイド層23の少なくとも一部を除去することにより、反応層12の表面の少なくとも一部を露出させる工程と、露出させた反応層12の表面上に電極層13を形成する工程とを含む。

(もっと読む)

改良した歪みシリコンCMOSデバイスおよび方法

【課題】 デバイス・チャネルに一軸性歪みを生成してキャリア移動度を向上させた半導体デバイスを提供する。

【解決手段】 本発明は、半導体デバイスのデバイス・チャネルに一軸性歪みを生成する半導体デバイスおよびその形成方法を提供する。一軸性歪みは、引張り性または圧縮性とすることができ、デバイス・チャネルに平行な方向である。一軸性歪みは、歪み誘発ライナ、歪み誘発ウェル、またはそれらの組み合わせによって、二軸性歪み基板表面において生成することができる。一軸性歪みは、歪み誘発ウェルおよび歪み誘発ライナの組み合わせによって、緩和基板において生成することも可能である。また、本発明は、歪み誘発分離領域によって二軸性歪みを増大させるための手段も提供する。更に、本発明が提供するCMOSデバイスにおいては、CMOS基板のデバイス領域を別個に処理して、圧縮性または引張り性の一軸性歪み半導体表面を提供する。

(もっと読む)

シリコン−ゲルマニウム合金及びシリコン−カーボン合金を用いるヘテロ接合電界効果トランジスタ

シリコン−ゲルマニウムバッファ層及びシリコン−カーボンチャネル層構造を用いて製造された半導体素子、例えばヘテロ接合電界効果トランジスタ。本発明は、例えば合金のSi格子中に実質的に組み入れられた約1.5原子%よりも少ないCを含むシリコン−カーボン合金の歪シリコンチャネル層を形成することによって、上部に歪シリコンチャネル層が形成されたSiGe緩和バッファ層における減少されたゲルマニウム含有量を介して貫通欠陥密度を減少させる方法を提供する。  (もっと読む)

(もっと読む)

改善されたしきい電圧およびフラットバンド電圧の安定性を有する相補型金属酸化膜半導体(CMOS)構造およびそれを形成する方法(高k誘電体によるCMOSデバイス形成におけるしきい電圧制御を達成するためのバリア層の選択的実装)

【課題】 改善されたしきい電圧およびフラットバンド電圧の安定性を有するCMOS構造を形成する方法およびそれにより生産されたデバイスを提供することにある。

【解決手段】 発明の方法は、nFET領域とpFET領域とを有する半導体基板を設けるステップと、高k誘電体の上に絶縁中間層を含む誘電体スタックを半導体基板の上に形成するステップと、pFET領域から絶縁中間層を除去せずに、nFET領域から絶縁中間層を除去するステップと、pFET領域内に少なくとも1つのゲート・スタックを設け、nFET領域内に少なくとも1つのゲート・スタックを設けるステップとを含む。絶縁中間層はAlNまたはAlOxNyにすることができる。高k誘電体は、HfO2、ハフニウム・シリケート、またはハフニウム酸窒化シリコンにすることができる。絶縁中間層は、HCl/H2O2過酸化水素溶液を含むウェット・エッチングによりnFET領域から除去することができる。

(もっと読む)

高誘電率誘電材料への酸窒化シリコン層の形成

本発明の実施形態は、基板上に配置された誘電層上にキャッピング層を堆積するための方法を提供する。一例では、プロセスは、基板を堆積プロセスに曝して、この上に誘電層を形成するステップと、該基板をシリコン前駆体および酸化ガスの順次パルスに曝して、堆積プロセス中にシリコン含有層を該誘電層上に形成するステップと、該基板を窒化プロセスに曝して、この上にキャッピング層を形成するステップと、所定の時間該基板をアニーリングプロセスに曝すステップとを含む。該キャッピング層は約5Å以下の厚さを有していてもよい。一例では、該酸化ガスが、触媒を含有する水蒸気生成器によって処理された水素源ガスおよび酸素源ガスから生じた水蒸気を含有する。別の例では、該堆積、窒化およびアニーリングプロセスが同じプロセスチャンバで生じる。 (もっと読む)

半導体装置およびその製造方法

炭化シリコン半導体基板を用いた二重拡散MOS構造の半導体装置。この半導体装置は、炭化シリコン半導体基板の表面に積層されて、炭化シリコン半導体基板と同じ第1導電型を有する炭化シリコン半導体エピタキシャル層と、この炭化シリコン半導体エピタキシャル層の表層部に第2導電型不純物をドーピングすることによって形成されて、その表面付近における第2導電型不純物濃度が相対的に薄く、深部における第2導電型不純物濃度が相対的に濃くされたプロファイルを有する不純物領域とを備えている。 (もっと読む)

ドープされたゲート誘電体を有するトランジスタ

トランジスタおよびその製造方法。ゲート誘電体材料を堆積する前に半導体基材をドープする。別個のアニール工程、または、トランジスタを製造するために使用される後続のアニール工程の間を用いて、ドーパント種を、基材のドープされた領域から、ゲート誘電体内に出力拡散して、ドープされたゲート誘電体を生成する。ドーパント種は、ゲート誘電体の原子構造における各空孔を埋め、その結果、トランジスタの動作速度が上昇し、電力消費が低減され、電圧安定性が改善される。  (もっと読む)

(もっと読む)

トンネル層に量子ドットを有するトランジスタ

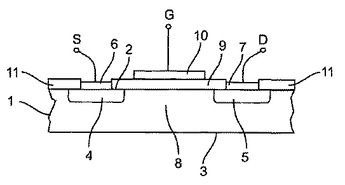

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

LDMOSトランジスタを有する電子装置

本発明のLDMOSトランジスタは、段付きシールド構造及び/又は第1及び第2ドレイン延長領域を具備し、前記第1ドレイン延長領域は、前記第2ドレイン延長領域よりも高いドーパント濃度を有し、前記シールドによって被われている。

(もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

SiC基板1と、SiC基板1表面に形成されたソース3a及びドレイン3bと、SiC表面に接して形成され厚さが1分子層以上のAlN層5と、その上に形成されたSiO2層とを有する絶縁構造と、この絶縁構造上に形成されたゲート電極15とを有しており、SiCとの間の界面状態を良好に保ちつつ、リーク電流を抑制することができる。 (もっと読む)

SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

(もっと読む)

621 - 638 / 638

[ Back to top ]