Fターム[5F140BA02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | SiC (638)

Fターム[5F140BA02]に分類される特許

101 - 120 / 638

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体装置に形成される絶縁膜の付着力を高め歩留りを向上させる。

【解決手段】基板10の上方に形成された半導体層20〜23と、前記半導体層20〜23上に形成された絶縁膜31,32と、前記絶縁膜上31,32に形成された電極41と、を有し、前記絶縁膜31,32は、前記電極41の側における膜応力よりも、前記半導体層20〜23の側における膜応力が低いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリ・オフ動作に適したMIS型を採用するも、電流コラプス特性を大幅に向上させて、デバイス効率及び耐圧に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成されたゲート絶縁膜6と、ゲート電極7とを含み、ゲート電極7は、ゲート絶縁膜6上に形成されたゲート基部7aと、ゲート基部7a上に形成されたゲート傘部7bとを有しており、ゲート傘部7bの下面が化合物半導体積層構造2とショットキー接触する。

(もっと読む)

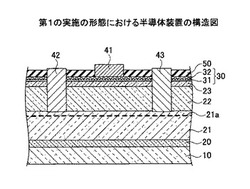

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体層とゲート電極との間に絶縁膜が形成された半導体装置の信頼性を高める。

【解決手段】基板の上方に形成された半導体層と、前記半導体層上に形成された絶縁膜と、前記絶縁膜上に形成された電極と、を有し、前記絶縁膜は炭素を主成分とするアモルファス膜を含むものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

半導体装置の製造方法

【課題】半導体の表面の酸化物を含む不純物を、エッチングあるいは、他の層を積層する前に除去する。

【解決手段】第1の半導体層110の少なくとも一部に接し、第1の半導体層110に含まれる不純物の固溶度が、第1の半導体層110より高い第1の犠牲層を形成する第1犠牲層形成工程と、第1の犠牲層および第1の半導体層をアニールするアニール工程と、第1の犠牲層をウェットプロセスで除去する除去工程と、第1の半導体層の少なくとも一部を覆う絶縁層120を形成する工程および第1の半導体層の一部をエッチングする工程の少なくとも一の工程と、第1の半導体層に電気的に接続された電極層126を形成する電極形成工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】特性バラツキを低減することができるような半導体装置及びその製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置は、ゲート絶縁膜を介して基板の表面を第1導電型チャネル領域から酸化膜の一部までを覆い、且つ、第1導電型チャネル領域と酸化膜との間に開口部を有するゲート電極と、この開口部下の基板に形成された第2導電型ドリフト領域の第2の部分とを有する。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】特性の安定化を達成できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第3半導体層5、第4半導体層6、第1電極10、第2電極8及び第3電極9を備える。第1半導体層3、第2半導体層4、第3半導体層5及び第4半導体層6は、窒化物半導体を含む。第2半導体層4は、第1半導体層3の禁制帯幅以上の禁制帯幅を有する。第3半導体層5は、GaNである。第4半導体層6は、第3半導体層5の上において一部に隙間を有して設けられ、第2半導体層4の禁制帯幅以上の禁制帯幅を有する。第1電極10は、第3半導体層5の上において第4半導体層6が設けられていない部分に設けられる。第2電極8及び第3電極9は、第4半導体層6の上において、第1電極10の一方側及び他方側にそれぞれ設けられ、第4半導体層6とオーミック接合している。

(もっと読む)

炭化珪素半導体基板、炭化珪素半導体装置、炭化珪素半導体基板の製造方法および炭化珪素半導体装置の製造方法

【課題】高品質な単結晶SiC基板の使用量を減らすことが可能であり、信頼性を向上させることができるSiC半導体装置の製造方法を提供することを目的とする。

【解決手段】支持基板1として、単結晶SiCと異なる材料を用いて構成され、かつ活性層3を形成する工程および半導体素子の構成要素4〜10、14〜17を形成する工程における温度以上の耐熱性を有するものを用い、接合工程では、半導体素子の動作温度以下の温度で直接接合する。このような製造方法では、支持基板1と単結晶SiC基板11とを半導体素子の動作温度以下の温度で接合しているため、支持基板1と単結晶SiC基板11との接合界面で発生する応力を小さくすることができ、SiC半導体装置が使用される際に半導体素子に印加される応力を小さくすることができる。すなわち、SiC半導体装置の信頼性が低下することを抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFET特性を改善することができる半導体装置及びその製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置は、基板と、基板の上方に形成されたゲート電極と、ゲート電極の下に形成されたゲート絶縁膜と、ゲート絶縁膜の下に、シリコン基板の材料に比して広いバンドギャップを持つチャネル層材料により形成されたチャネル層と、チャネル方向に沿ってチャネル層を挟むように基板に形成されたソース領域とドレイン領域と、チャネル層とソース領域との間のシリコン基板に、チャネル層のソース側端部とオーバーラップするように形成され、且つ、チャネル層とともにキャリアがトンネルするヘテロ界面を成すソースエクステンション層とを有する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高いゲート絶縁膜を備えたSiC半導体装置を提供する。

【解決手段】8度以下のオフ角度を有する炭化珪素基板(1)と、この基板上に形成された第1導電型の第1炭化珪素領域(2)と、この領域の表面に形成された第2導電型の第2炭化珪素領域(3)と、この領域の表面に形成され、不純物濃度が第2の炭化珪素領域と同程度に調整された第1導電型の第3炭化珪素領域(4)と、この領域の表面に選択的に形成された第1導電型の第4炭化珪素領域(5)と、第2炭化珪素領域の表面に形成された第2導電型の第5炭化珪素領域(6)と、第1炭化珪素領域から第3炭化珪素領域の少なくとも端部までを覆うように形成されたゲート絶縁膜(7)と、この上に形成されたゲート電極(8)とを具備し、第3炭化珪素領域の表面における、第3と第4炭化珪素領域の境界面は、オフ角度方向と90°以外の角度で交差するように形成されている。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有し、第1導電型のバックゲートコンタクト領域を有さない第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

シリコンカーバイドから半導体構造体を製造する方法並びにシリコンカーバイド半導体

【課題】正確、均一かつ再現可能な構造化を可能にする、シリコンカーバイドから半導体構造を製造する方法を提供すること

【解決手段】上記の課題は、ポリシリコン層を基板上に被着するステップと、マスキングの構造を、前記ポリシリコン層内に移し、トレンチとインプランテーション領域との間に、ポリシリコンから成るスペーサーを設け、マスキングを除去し、基板を熱によって酸化させ、SIO2HTO層を析出し、インプランテーション領域をインプランテーションし、酸化物層を開放し、スペーサーを除去し、残余酸化物カバー並びに完全な酸化物を除去することを特徴とする方法

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】半導体装置において、セルフターンオンが発生しないようにし、安定した動作を実現する。

【解決手段】半導体装置を、基板1と、基板の上方に設けられ、電子走行層6及び電子供給層7を含む半導体積層構造2と、半導体積層構造の上方に設けられたゲート電極3、ソース電極4及びドレイン電極5と、ゲート電極、ソース電極及びドレイン電極の上方に設けられ、ゲート電極、ソース電極及びドレイン電極のそれぞれに接続されたゲートパッド10、ソースパッド11及びドレインパッド12と、ゲートパッド、ソースパッド及びドレインパッドの下方に設けられた導電層1とを備えるものとし、ゲートパッドとソースパッドとの間の距離を、ゲートパッドとドレインパッドとの間の距離よりも小さくする。

(もっと読む)

101 - 120 / 638

[ Back to top ]