Fターム[5F140BA03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | Ge (420)

Fターム[5F140BA03]に分類される特許

401 - 420 / 420

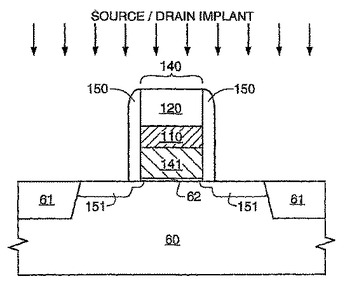

半導体デバイス製造のためのゲート材料

電子デバイスを形成する際、半導体層を予めドープして、ドーパント分布アニールをゲート画定前に行う。場合によっては、ゲートは金属から形成されている。したがって、続いて形成される浅いソースおよびドレインは、ゲートアニールステップの影響を受けない。  (もっと読む)

(もっと読む)

ゲルマニウム基板タイプ材料およびその手法

ゲルマニウム回路タイプの構造が促進される。一実施形態例では、多段階の成長およびアニール・プロセスを実施して、ヘテロエピタキシャルル・ゲルマニウムなどのゲルマニウム(Ge)含有材料を、シリコン(Si)またはシリコン含有材料を含む基板上に成長させる。いくつかの応用例では、ゲルマニウム含有材料の上面に向かって貫通する欠陥が全体的に抑制されて、欠陥が全体的にシリコン/ゲルマニウム境界面付近に閉じ込められる。これらの手法は、ゲルマニウムMOSコンデンサ、pMOSFET、およびオプトエレクトロニック・デバイスを含む、さまざまなデバイスに適用できる。  (もっと読む)

(もっと読む)

スピントランジスタ、プログラマブル論理回路および磁気メモリ

【課題】増幅機能を有するスピントランジスタを提供すること。

【解決手段】スピントランジスタ100は、半導体基板10と、半導体基板10上において第1方向に磁化された強磁性体で形成される第1導電層12と、半導体基板10上において第1方向とその第1方向に対して反平行の第2方向とのいずれか一方に磁化される強磁性体で形成された第2導電層14と、第1導電層12と第2導電層14の間に位置し、第1導電層12と第2導電層14との間で電子スピンを導くチャネル部と、チャネル部の上方に位置するゲート電極40と、第1導電層12および第2導電層14の少なくとも一方とチャネル部との間に位置するトンネルバリア膜11a,11bと、を備える。

(もっと読む)

MOS電界効果トランジスタ型量子ドット発光素子および受光素子、これらを利用した光電子集積チップおよびデータ処理装置

【課題】 MOS電界効果トランジスタ型量子ドット発光素子および受光素子の提供、MOS電界効果トランジスタ型量子ドット発光素子の製造方法の提供、かかる受発光素子を利用した光電子集積チップ、データ処理装置を提供することを目的とする。

【解決手段】 MOS電界効果トランジスタ型量子ドット発光素子は、半導体基板と、該半導体基板上に形成されたトンネルSiO2層と、該トンネルSiO2層上に形成されたSi殻内にGe核を内包した量子ドットと、該量子ドット上及び前記トンネルSiO2層上に形成されたコントロールSiO2層と、該コントロールSiO2層上に形成されたゲート電極層と、を有する。MOS電界効果トランジスタ型量子ドット発光素子は、半導体基板と、該半導体基板上に形成されたゲートSiO2層と、該ゲートSiO2層上に形成されたドープSi層、Ge層及びドープSi層を順次積層してなる積層ゲート電極層と、を有する。

(もっと読む)

平滑基板上への高K誘電体層の形成

平坦シリコン基板上に、バッファ層と高K金属酸化物誘電体が形成される。基板の平坦度は、高K金属酸化物ゲート誘電体が柱状成長することにより低下する。基板表面は、成膜の前に、水酸基終端で飽和化される。  (もっと読む)

(もっと読む)

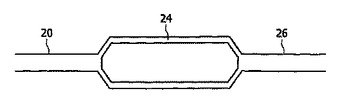

ナノスケールFET

トランジスタデバイスは、ソース領域、ドレイン領域、およびソース領域とドレイン領域の間のチャネル領域を有する連続リニアナノ構造体で形成される。ソース領域(20)とドレイン領域(26)はナノワイヤで形成され、チャネル領域(24)はナノチューブの形である。ソース領域とドレイン領域の間のチャネル領域における伝導を制御するためにチャネル領域(24)に隣接する絶縁ゲート(32)が提供される。  (もっと読む)

(もっと読む)

改良した歪みシリコンCMOSデバイスおよび方法

【課題】 デバイス・チャネルに一軸性歪みを生成してキャリア移動度を向上させた半導体デバイスを提供する。

【解決手段】 本発明は、半導体デバイスのデバイス・チャネルに一軸性歪みを生成する半導体デバイスおよびその形成方法を提供する。一軸性歪みは、引張り性または圧縮性とすることができ、デバイス・チャネルに平行な方向である。一軸性歪みは、歪み誘発ライナ、歪み誘発ウェル、またはそれらの組み合わせによって、二軸性歪み基板表面において生成することができる。一軸性歪みは、歪み誘発ウェルおよび歪み誘発ライナの組み合わせによって、緩和基板において生成することも可能である。また、本発明は、歪み誘発分離領域によって二軸性歪みを増大させるための手段も提供する。更に、本発明が提供するCMOSデバイスにおいては、CMOS基板のデバイス領域を別個に処理して、圧縮性または引張り性の一軸性歪み半導体表面を提供する。

(もっと読む)

圧縮歪Ge層内にPMOSデバイスを作製する構造および方法(先端CMOS技術への歪Geの統合)

【課題】 圧縮歪Ge層内にPMOSデバイスを作製する構造および方法を開示する。

【解決手段】 このようなデバイスの作製方法は、標準的なCMOS技術に適合し、完全にスケーリング可能である。該処理は、50%を超えるGe含有量のバッファ層、純粋Ge層、およびSiGe最上層の選択的なエピタキシャル堆積を含む。圧縮歪Ge層にホスティングされるように作製された埋め込みチャネル型PMOSは、同様のSiデバイスに対して優位のデバイス特性を示す。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】 高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタおよびその製造方法を実現する。

【解決手段】 シリコン基板1上に、フィン形状に突出して形成されたフィン部3、5を設ける。フィン部3、5のチャネル領域部を被覆したゲート誘電体8を設ける。ゲート誘電体8によってチャネル領域部から絶縁されて、上記チャネル領域部上に形成されたゲート電極4を設ける。シリコン基板1上を覆う絶縁体層2を設ける。フィン部3、5は、シリコン基板1から絶縁体層2を貫通して絶縁体層2の表面より突出して延びるように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 閾値の変動を回避するとともに、電気的ストレスに対する信頼性の高いMOSトランジスタを備えた半導体装置を提供する。

【解決手段】 素子領域を画定する素子分離領域(12)が設けられた半導体基板(11)と、前記半導体基板の前記素子領域に離間して設けられたソース/ドレイン領域(25)と、前記半導体基板の前記素子領域上に設けられたゲート絶縁膜(13,14)と、前記ゲート絶縁膜上に設けられ、半導体を含むゲート電極(15)とを具備する半導体装置である。前記ゲート絶縁膜は、金属および酸素を含有する第1の絶縁膜(13)と、この第1の絶縁膜上に形成され、シリコンおよび酸素を含有する第2の絶縁膜(14)とを含み、前記第2の絶縁膜は、前記ゲート電極との界面における前記金属の含有量が6.6atomic.%未満であることを特徴とする。

(もっと読む)

改善されたしきい電圧およびフラットバンド電圧の安定性を有する相補型金属酸化膜半導体(CMOS)構造およびそれを形成する方法(高k誘電体によるCMOSデバイス形成におけるしきい電圧制御を達成するためのバリア層の選択的実装)

【課題】 改善されたしきい電圧およびフラットバンド電圧の安定性を有するCMOS構造を形成する方法およびそれにより生産されたデバイスを提供することにある。

【解決手段】 発明の方法は、nFET領域とpFET領域とを有する半導体基板を設けるステップと、高k誘電体の上に絶縁中間層を含む誘電体スタックを半導体基板の上に形成するステップと、pFET領域から絶縁中間層を除去せずに、nFET領域から絶縁中間層を除去するステップと、pFET領域内に少なくとも1つのゲート・スタックを設け、nFET領域内に少なくとも1つのゲート・スタックを設けるステップとを含む。絶縁中間層はAlNまたはAlOxNyにすることができる。高k誘電体は、HfO2、ハフニウム・シリケート、またはハフニウム酸窒化シリコンにすることができる。絶縁中間層は、HCl/H2O2過酸化水素溶液を含むウェット・エッチングによりnFET領域から除去することができる。

(もっと読む)

高誘電率誘電材料への酸窒化シリコン層の形成

本発明の実施形態は、基板上に配置された誘電層上にキャッピング層を堆積するための方法を提供する。一例では、プロセスは、基板を堆積プロセスに曝して、この上に誘電層を形成するステップと、該基板をシリコン前駆体および酸化ガスの順次パルスに曝して、堆積プロセス中にシリコン含有層を該誘電層上に形成するステップと、該基板を窒化プロセスに曝して、この上にキャッピング層を形成するステップと、所定の時間該基板をアニーリングプロセスに曝すステップとを含む。該キャッピング層は約5Å以下の厚さを有していてもよい。一例では、該酸化ガスが、触媒を含有する水蒸気生成器によって処理された水素源ガスおよび酸素源ガスから生じた水蒸気を含有する。別の例では、該堆積、窒化およびアニーリングプロセスが同じプロセスチャンバで生じる。 (もっと読む)

トライゲートトランジスタ及びその製造方法

本発明の実施形態は、均一なシリコンボディ高さをもたらすSOIトランジスタの製造方法を提供する。一実施形態では、犠牲酸化物層が半導体基板上に配置される。酸化物層はトレンチを形成するようにエッチングされ、トレンチは半導体材料で充填される。そして、半導体材料は酸化物層の残部を用いて平坦化され、その後、酸化物層の残部は除去される。こうして露出された半導体フィンは仕様の許容範囲内で均一な高さを有する。  (もっと読む)

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

横型高電圧接合デバイス

MOS回路の過電圧保護のための横型高電圧接合デバイスは、基板領域によって第2接合領域から分離された第1接合領域を有する基板を含む。MOSゲート電極は基板領域の上に重なり、ゲート誘電体層によってそこから分離される。MOSゲート電極の対向辺に隣接してサイドウォールスペーサが存在し、基板領域の上に重なる。基板領域は、第1および第2接合領域の間の無接合半導体領域によって画定される。入力保護回路は横型高電圧接合デバイスを使用して、電圧過渡を接地ノードに転送する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

シリコン基板(101)上に、RTO法によりシリコン酸化物からなる下地層(103)を形成する。このとき、下地層(103)の膜厚を1.5nm以上とする。次に、下地層(103)上に、CVD法によりハフニウム窒化物を0.5乃至1.0nmの厚さに堆積させ、金属化合物層(104)とする。次に、水素雰囲気中において熱処理を施し、金属化合物層(104)から下地層(103)中にハフニウム元素を拡散させてシリケート化させ、ゲート絶縁膜(106)を形成する。その後、酸化雰囲気中において熱処理を行う。このとき、シリコン基板(101)とゲート絶縁膜(106)との界面には、ハフニウム元素が到達しないようにする。  (もっと読む)

(もっと読む)

Geベース材料上のゲルマニウム酸窒化物層の生成

【課題】 Geベース材料上にゲルマニウム酸窒化物層を生成すること。

【解決手段】 ゲート誘電体として用いるために、6nmより薄い等価酸化物厚をもつ薄いゲルマニウム酸窒化物層をGeベース材料上に生成する方法が開示される。この方法は二ステップのプロセスを含む。第一に、窒素がGeベース材料の表面層に組込まれる。第二に、窒素組込みステップ後に酸化ステップが続く。本方法は、MOSトランジスタなどのGeベース電界効果デバイスのための高品質ゲート誘電体の厚さに対する優れた制御をもたらす。薄いゲルマニウム酸窒化物ゲート誘電体を有するデバイスの構造及びこのようなデバイスから作られるプロセッサも同様に開示される。

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

半導体デバイス並びに量子井戸構造体を製造する方法及び量子井戸構造体を有する半導体デバイス

量子井戸構造体(4)を備える多重層構造体(3)を基板(2)上に得るための半導体デバイス(1)及び方法が開示されている。量子井戸構造体(4)は、絶縁物質(6、6’)によって挟まれる半導体層(5)を有し、絶縁物質(6、6’)の物質は好ましくは、高誘電率を有する。FETにおいて、量子井戸(4、9)はチャネルとして機能し、より高い駆動電流及びより低いオフ電流が可能になる。短チャネル効果が低減される。多重チャネルFETは、サブ35nmゲート長に対してさえも動作するのに適している。本方法において、量子井戸は、好ましくはMBEを用いて、半導体物質及び高誘電率物質のエピタキシャル成長によって互いの上に交互に形成される。

(もっと読む)

(もっと読む)

401 - 420 / 420

[ Back to top ]