Fターム[5F140BA03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | Ge (420)

Fターム[5F140BA03]に分類される特許

201 - 220 / 420

トランジスタ、集積回路および集積回路形成方法

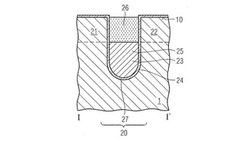

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

チップレス・エピタキシャルソース/ドレイン領域を有する半導体デバイス

チップエクステンション部のないチップレス・エピタキシャルソース/ドレイン領域を有する半導体デバイス、及びその製造方法が提供される。一実施形態において、当該半導体デバイスは基板上にゲートスタックを有する。該ゲートスタックは、ゲート誘電体層上にゲート電極を有し、基板内のチャネル領域上に位置する。当該半導体デバイスはまた、基板内のチャネル領域のそれぞれの側に一対のソース/ドレイン領域を有する。該一対のソース/ドレイン領域はゲート誘電体層に直に接触し、且つ該一対のソース/ドレイン領域の格子定数はチャネル領域の格子定数と異なる。一実施形態において、当該半導体デバイスは、誘電体のゲートスタックプレースホルダーを用いて形成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】素子特性のばらつきが抑制されたMOS型素子を含む半導体装置を提供すること。

【解決手段】基板の半導体領域に埋め込まれた素子分離絶縁膜と、前記素子分離絶縁膜によって素子分離され、上部が前記素子分離絶縁膜の表面よりも上に突出し、前記半導体領域の半導体層と、この半導体層にソース・ドレイン領域、ゲート絶縁膜およびゲート電極が形成され、かつ、前記ゲート電極がチャネル幅方向に平行な面の断面において前記素子分離絶縁膜上に形成されてなるMOS型素子とを具備してなり、前記ゲート電極下の前記半導体層の上面位置が、前記ゲート電極下の前記素子分離絶縁膜の上面位置よりも、20nm以上高いことを特徴とする。

(もっと読む)

歪みシリコン窒化物膜及び該膜を含むデバイスの作製方法

歪みSiN膜及び該歪みSiN膜を含む半導体デバイスの作製方法。当該方法は、シリコン先駆体を含む気体に前記基板を曝露する工程、第1レベルのプラズマ出力のプラズマ源によって励起されて前記シリコン先駆体と第1反応特性で反応する窒素先駆体を含む気体に前記基板を曝露する工程、及び、前記第1レベルとは異なる第2レベルのプラズマ出力のプラズマ源によって励起されて前記シリコン先駆体と第2反応特性で反応する窒素先駆体を含む気体に前記基板を曝露することで、前記の基板上に作製されたシリコン窒化物膜の特性が前記歪みSiN膜を供するように変化する、工程を有する。  (もっと読む)

(もっと読む)

自己整合エピタキシャルソース及びドレイン張り出し部を有する半導体デバイス

ゲート誘電層に近接する自己整合ソース及びドレイン張り出し部を有するトランジスタの作製方法は、基板上にゲート積層体を作製する工程、前記ゲート積層体に隣接する前記基板の領域へドーパントを注入する工程であって、前記ドーパントは前記基板のエッチング速度を増大させ、かつ前記ソース及びドレイン張り出し部の位置を画定する工程、前記基板のドーパントが注入された領域上に設けられた前記ゲート積層体の横方向で対向する面に一対のスペーサを形成する工程、前記基板のドーパントが注入された領域及び該領域の下に位置する前記基板の一部をエッチングする工程であって、前記ドーパントが注入された領域のエッチング速度は該領域の下に位置する前記基板の一部のエッチング速度よりも速い工程、並びに、前記の基板のエッチングされた部分中にシリコンベースの材料を堆積する工程、を有する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】製造方法の煩雑化を抑制し、ばらつきを抑え、適切なしきい値およびゲート電極の空乏化の抑制を実現可能にする。

【解決手段】p型半導体基板2と、p型半導体基板に離間して形成された第1ソース領域6aおよび第1ドレイン領域6bと、第1ソース領域および第1ドレイン領域との間のp型半導体基板上に形成された第1ゲート絶縁膜11と、第1ゲート絶縁膜上に形成され、母相が多結晶シリコン15aであり、その結晶粒界と第1ゲート絶縁膜との界面の少なくとも第1原子層15cに真空仕事関数がシリコンのミッドギャップより小さい金属状態の第1金属元素を含有する第1ゲート電極15と、を有するnチャネルMISFETと、を備えている。

(もっと読む)

縦型スピントランジスタ及びその製造方法

【課題】トランジスタ及びその製造方法に関して、新たな構造のスピントランジスタ及びその製造方法を提案すること。

【解決手段】磁性体で形成された層を含んでいる第1のソースドレイン層と;前記第1のソースドレイン層上に形成されており、半導体で形成された層を含んでいる、チャネル層と、前記チャネル層上に形成されており、磁性体で形成された層を含んでいる、第2のソースドレイン層と、を含む突起構造と;前記チャネル層の側面に形成されたゲート絶縁膜と;前記ゲート絶縁膜の表面に形成されたゲート電極と;を具備することを特徴とする縦型スピントランジスタ。

(もっと読む)

ゲート・フィン間の重なりセンシティビティが低減されたFinFET

【課題】 均一な幅の短いフィンを有するFinFETを形成する改善された方法を提供すること。

【解決手段】 本発明の実施形態は、フィン型電界効果トランジスタ(FinFET)における比較的均一な幅のフィン、並びに、これを形成するための装置及び方法を提供するものである。フィン構造体は、該フィン構造体の側壁部分の表面が、第1の結晶方向に対して垂直になるように形成することができる。フィン構造体の端部のテーパ状領域は、第2の結晶方向に対して垂直であり得る。フィン構造体に結晶依存エッチングを行うことができる。結晶依存エッチングは、第2の結晶方向に対して垂直なフィンの部分から、相対的により速く材料を除去することができ、これにより、比較的均一な幅のフィン構造体がもたらされる。

(もっと読む)

2つの仕事関数を備えたCMOSデバイスの製造方法

【課題】本発明は、2つの仕事関数の半導体デバイスの製造方法を提供する。

【解決手段】製造方法は、基板の第1領域及び第2領域上にデバイスを設けることを備える。これは、基板の第1領域及び第2領域上に誘電性層を設けること、及び第1及び第2領域の両方の誘電性層の上部にゲート電極を設けることによってなされる。第1領域上のゲート電極及び第2領域上のゲート電極の両方は仕事関数を有する。上記方法は、さらに、誘電性層とゲート電極との間で第1領域上にキャッピング層を設けることで第1領域上のゲート電極の仕事関数を変更し、及び第2領域における誘電性層とゲート電極との間の界面でスピーシーズを導入するようにスピーシーズを埋め込むことにより第2領域上のゲート電極の仕事関数を変更することを備える。

(もっと読む)

マルチフィンガートランジスタ

【課題】寄生キャパシタンスを小さくしゲート抵抗を小さくする。

【解決手段】マルチフィンガートランジスタ400は、アクティブ領域420、マルチフィンガーゲート450、ソース領域460、及びドレイン領域470を含む。アクティブ領域は、基板の単位セル内に定義され、二つに形成される。マルチフィンガーゲートは、アクティブ領域内に形成された複数のゲートフィンガー452、及びゲートフィンガーを互いに接続して二つのアクティブ領域の間に形成されたゲート接続部454を含む。ソース領域は、ゲートフィンガーに隣接するアクティブ領域の一部に形成される。ドレイン領域は、ゲートフィンガーに隣接するアクティブ領域の一部に複数形成される。マルチフィンガートランジスタは、小さい面積を有しかつ、低い抵抗及び寄生キャパシタンスを有する。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

ゲートの誘電性スタックの制御された形成方法

【課題】ゲートの誘電性スタックの制御された形成方法を提供する。

【解決手段】半導体基板に誘電性材料層を形成し、上記誘電性材料層上に希土類酸化物層を堆積し、上記希土類酸化物層上に金属ゲート電極材料を堆積した後、焼き鈍しを行い希土類ケイ酸塩層を形成する。ここで、金属ゲート電極材料を堆積する前に、焼き鈍し工程は行わない。

(もっと読む)

半導体装置

【課題】ピンチオフを抑制する構造を有することによって、駆動電流を向上させることのできる電界効果トランジスタを含む半導体装置を提供する。

【解決手段】ソース領域111およびドレイン領域121と、このソース領域111とドレイン領域121との間に存在し、相対する主面を有するチャネル領域101と、主面にゲート絶縁膜103、104を介して設けられた一対のゲート電極107、108を具備し、相対する主面の間隔が、ドレイン領域121側においてソース領域111側よりも大きい電界効果トランジスタを含むことを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】チャネル領域に歪みを有するMIS型電界効果トランジスタに関し、低抵抗な接合界面を実現する半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板100上にゲート絶縁膜101を介してゲート電極102を形成するステップと、ゲート電極102の両側の、半導体基板中または基板上に、不純物濃度が5×1019atoms/cm3以上1021atoms/cm3以下のp型の高濃度不純物層108を形成するステップと、高濃度不純物層108に圧縮歪みがかかっている状態で、高濃度不純物層108を金属と反応させシリサイド化するステップを有することを特徴とする半導体装置の製造方法およびその製造方法によって形成される半導体装置。

(もっと読む)

垂直方向のチャンネルを有するアクセス素子、これを含む半導体装置、及びアクセス素子の形成方法

【課題】垂直方向のチャンネルを有するアクセス素子、これを含む半導体装置、及びアクセス素子の形成方法が開示される。

【解決手段】アクセス素子及びこれを形成する方法において、アクセス素子は、下部ソース/ドレイン領域と上部ソース/ドレイン領域を分離する垂直方向のチャンネル、チャンネル上に具備されるゲート絶縁膜、ゲート絶縁膜を横切って前記チャンネルを連結する一体型ゲート電極/連結ラインを含み、一体型ゲート電極/連結ラインはゲート絶縁膜と隣接するように具備され、下部ソース/ドレインの一部と少なくともオーバーレイされるディセンディングリップ領域を含むことができる。

(もっと読む)

ディープサブミクロントランジスタ技術用のhigh−k/金属ゲートスタックをパッシベートするためのFベースのゲートエッチングの使用

【課題】プレーナ装置またはマルチゲート装置(MuGFET)のHfベースの誘電体ゲートスタックに、フッ素を導入し、負バイアス温度安定性および正バイアス温度安定性(NBTIおよびPBTI)を大幅に改良する、新規で、効果的で、費用対効果の高い方法を提供する。

【解決手段】新規な方法は、フッ素を導入するためにSF6ベースの金属エッチング化学反応を用い、これにより標準プロセスフローの熱量の後に、界面の優秀なHパッシベーションが得られる。この方法の優位点は、この方法がFを導入するための金属ゲートエッチングを用いて、追加の注入や処理が不要であることである。新たな方法を用いた大幅なBTIの改良に加えて、MuGFET装置において、より良いVthの制御性と増加した駆動電流を得ることができる。

(もっと読む)

電子デバイスおよびその製造プロセス

【課題】金属酸化物半導体電界効果トランジスタのような金属絶縁体デバイスおよび/または金属絶縁体金属キャパシタを提供する。

【解決手段】装置は、

炭化タンタル、炭窒化タンタル、炭化ハフニウム、および炭窒化ハフニウムからなる組から選択される金属化合物を含む電極と、

窒素とシリコンを含む酸化ハフニウムからなるhigh−k誘電体層であって、少なくとも4.0のk値を有するhigh−k誘電体層と、

電極とhigh−k誘電体層との間に配置された窒素および/またはシリコンおよび/または炭素のバリア層とを含み、

窒素および/またはシリコンおよび/または炭素のバリア層は、1またはそれ以上の金属酸化物を含み、金属酸化物の金属はランタニド、アルミニウム、およびハフニウムからなる組から選択される。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】半導体基板、半導体柱及びコンタクトプラグを備える半導体素子において、活性領域として機能する少なくとも一対のフィンを備える半導体基板と、一対のフィンの一部分の間に該フィンを連結するように介在される半導体柱と、一対のフィンの上面に電気的に連結されるように半導体柱上に形成されるコンタクトプラグとを備える半導体素子である。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース・ドレイン領域とチャネル領域との境界付近における欠陥発生を抑制して、トランジスタ特性を向上させること。

【解決手段】シリコン基板1に形成された電界効果型トランジスタを有する半導体装置において、電界効果型トランジスタのチャネル部分を含む領域におけるシリコン基板1、実質的に(100)面または(100)面と結晶学的に等価な面を底面とし、かつ、実質的に(111)面または(111)面と結晶学的に等価な面を側面とする溝9が形成されており、溝9にシリコンとは異なる半導体材料10が埋め込まれている。半導体材料10は、シリコンよりもキャリアの移動度の高い半導体材料であり、エピタキシャル成長させたシリコンゲルマニウムまたはゲルマニウムを用いることができる。

(もっと読む)

電界効果トランジスタ素子およびその製造方法

【課題】改善した能力を備えた、MOSFETやHEMTなどの半導体トランジスタ素子を提供する。

【解決手段】本発明に係る半導体トランジスタ素子は、トランジスタがオンしたとき、電流をトランジスタに通すために、キャリアが移動できるチャネル層を含むチャネルエリア(1)と、チャネル層に対して電流を供給するために、チャネル層と接触したソースエリア(4)およびドレインエリア(5)と、ゲート電極(3)とを備え、好ましくは、ゲート電極とチャネル層との間にゲート誘電体(2)が設けられ、前記チャネル層はIII−V族材料からなり、前記ソースエリアおよびドレインエリアはSiGe(SixGe1−x、xは0と100%の間)を含み、ヘテロ接合(30,31)がIII−V族材料とSiGeの間に存在し、前記ヘテロ接合は、前記電流が前記ヘテロ接合を通過するように配置されており、前記ヘテロ接合(30,31)は、前記ゲート誘電体(2)または前記ゲート電極と交差するように配向している。

(もっと読む)

201 - 220 / 420

[ Back to top ]