Fターム[5F140BA03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | Ge (420)

Fターム[5F140BA03]に分類される特許

121 - 140 / 420

半導体装置

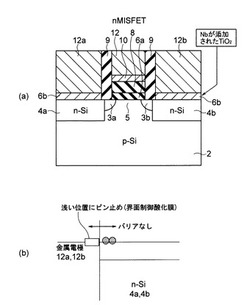

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

ゲート・ダイオード構造及びゲート・ダイオード構造の製造方法

【課題】改善された特性と強化された機能とを備えたダイオード構造とその製造方法が望まれている。

【解決手段】ゲート・ダイオード構造及びSOI基板(SOI)等の上にゲート・ダイオード構造を製造する方法であって、緩和下地層(34‘)を用いる。緩和下地層は歪下地層(34)から形成される。歪下地層(34)は典型的にはゲート・ダイオード構造と同時に形成される電界効果型トランジスタに用いられる。緩和下地層は歪下地層(34)のイオン注入処理のような処理により形成される。反応性イオンエッチング方法を用いてゲート・ダイオード構造から歪下地層を除去するときのゲート・ダイオードの損傷がないので、歪下地層に比較して、緩和下地層はゲート・ダイオード構造の理想値を改善する。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

半導体素子及び半導体装置

【課題】高い電流駆動力を有するn型半導体素子を提供する。

【解決手段】第1の主面を有し、III族の不純物を含み、1.2<N<10を満たすNを用いて(11N)面と表される、ないしはそれと結晶学的に等価な第1の面方位のみを前記第1の主面に有する、シリコンとゲルマニウムとの混晶層と、前記第1の主面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記混晶層の[110]方向ないしそれと結晶学的に等価な方向に、前記ゲート電極を挟む様に形成され、V族の不純物を含む半導体よりなるソース・ドレイン領域と、を有し、前記混晶層は面内方向に圧縮歪みが印加されていることを特徴とする。

(もっと読む)

半導体装置

【課題】電気的性質が良好なhigh−k膜/Geゲートスタック構造を有する半導体装置を提供する。

【解決手段】Geを主成分とする半導体領域(10)と、前記半導体領域上に形成された絶縁膜(11)と、前記絶縁膜上に形成された金属膜(12)とを具備する半導体装置である。前記絶縁膜は、少なくとも1種の希土類元素(MR)と、TiおよびZrから選択される少なくとも1種のIV族元素(MIV)と、酸素とを含むことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】横方向の寸法の増大を抑制しつつ、横型二重拡散電界効果トランジスタのソースとドレインとの間の電界を緩和する。

【解決手段】N型ドリフト層17には、埋込絶縁層14下に配置されたP−ダンパ層19を形成するとともに、P−ダンパ層19を取り囲むように配置されたN−ダンパ層18を形成し、N−ダンパ層18およびP−ダンパ層19にて埋込絶縁層14下が空乏化されるように不純物濃度を設定する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】柱状部の密度が疎な領域でも基板の主面をエッチングすることなく、ゲート電極の加工を行って、トランジスタ特性を安定に保つ半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】主面1aを有し、半導体材料からなる基板1と、基板1の主面1aに設けられ、主面1aに対して略垂直方向に伸長した形状を有する、前記半導体材料からなる柱状部2と、柱状部2の側面2cに形成された第1の絶縁膜6と、前記基板1の主面1aに形成され、第1の絶縁膜6の膜厚より少なくとも膜厚が厚い厚膜部を有する第2の絶縁膜16と、第1の絶縁膜6および第2の絶縁膜16の上に設けられ、前記柱状部2の側面2cから基板1の主面1aにかけて形成された導電層15と、を備える半導体装置を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の高集積化と供に、メモリ装置のキパシタで容量値の確保のために、酸素欠損のない高誘電率膜を形成する装置の製造方法を提供する。

【解決手段】誘電体膜を形成する工程と、酸化性ガスを供給して誘電体膜に対して酸化処理を行う工程を複数回、断続的に繰り返す熱処理工程と、を有する誘電体膜を備えた半導体装置の製造方法。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

シミュレーション装置、シミュレーション方法、およびシミュレーション用プログラムを記録した記録媒体。

【課題】電界効果トランジスタの電気的特性を短時間で計算する。

【解決手段】シミュレーション装置1は、構造モデル設定部11、量子化状態算出部12および状態混合部13を含む。構造モデル設定部11は、FETのヘテロ構造がチャネル領域を形成する閉じ込めポテンシャルを有するとともに単一の半導体層からなると仮定して仮想構造モデルを設定する。量子化状態算出部12は、仮想構造モデルそれぞれの仮想的な量子化電子状態を仮想電子状態として算出する。状態混合部13は、仮想電子状態の物性量を混合してチャネル領域の量子化電子状態の物性量を算出する。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

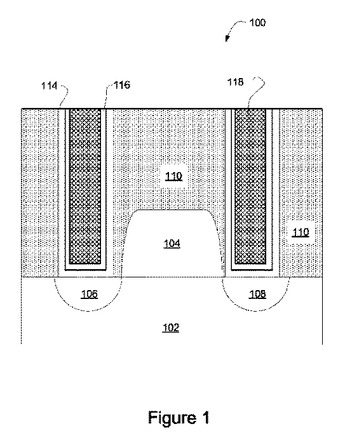

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】低閾値電圧動作が可能な電界効果トランジスタを提供する。

【解決手段】n型半導体基板2と、半導体基板に離間して形成されたソースおよびドレイン領域12a、12bと、ソース領域とドレイン領域との間の半導体基板上に形成され、Hf、Zr、Tiから選ばれた少なくとも1つの物質と酸素を含む第1絶縁膜4と、第1絶縁膜上に形成され、シリコンと酸素を含む第2絶縁膜8と、第2絶縁膜上に形成されたゲート電極10と、を備え、V、Cr、Te、P、As、S、Seの群から選ばれた少なくとも一つの第1物質と、窒素とが第1絶縁膜と第2絶縁膜との界面を含む界面領域7に含まれ、第1物質の面密度が界面領域内の第2絶縁膜側において第1ピークを有し、窒素の面密度が界面領域内に第2ピークを有し、第2ピークの位置が、第1ピークの位置よりも半導体基板側にある。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

ホウ素ドープ半導体ナノワイヤ及びその製造方法

【課題】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤは、次の工程を含む製造方法により製造できる。

工程(1):半導体原料ガスを用いて、基板上にIV族半導体ナノワイヤを成長させる;

工程(2):ジボランガスのみを導入することにより、前記半導体ナノワイヤの表面にホウ素膜を堆積させる;

工程(3):表面にホウ素膜を堆積させた前記ホウ素膜付き半導体ナノワイヤを、半導体ナノワイヤ(本体)の融点以下の温度で熱アニールする。

(もっと読む)

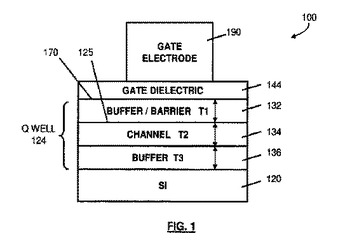

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

チャネル領域の下方にデルタドープ層を有するIII−V族デバイス

III−V族材料のデバイスは、チャネル領域の下方にデルタドープ領域を有する。これは、ゲートとチャネル領域との間の距離を短縮することによって、デバイスの性能を向上させ得る。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】Siおよびこれと同族元素であるGe,Cなどの組合せを用いて、低消費電力で高速なMOSFETを有する半導体装置の製造方法を提供する。

【解決手段】Si層1と、その上に形成されたMOSFETのゲート電極16と、Si層1に形成されたソース領域14及びドレイン領域15と、それらの間の領域に形成されるチャネル領域とを有する半導体装置の製造方法において、ソース領域14またはドレイン領域15が形成される領域のSi層1を選択的にエッチングし、形成された溝内にSiGeを選択成長させる。

(もっと読む)

121 - 140 / 420

[ Back to top ]