Fターム[5F140BA03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | Ge (420)

Fターム[5F140BA03]に分類される特許

141 - 160 / 420

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのホールリークが防止された横型のFETを提供することを課題とする。

【解決手段】基板の表面上に形成された第1導電型のチャネル層と、前記チャネル層上に形成されたソース電極、ドレイン電極及びゲート電極とを備え、前記ソース電極及びドレイン電極を前記チャネル層とオーミックコンタクトさせて電界効果型トランジスタを構成し、前記ドレイン電極の下部の前記チャネル層に第1導電型の拡散領域を備え、前記拡散領域が、式(1)Ns≧ε×Vmax/(q×t)(式中、εは前記チャネル層の誘電率[F/m]、Vmaxは前記電界効果型トランジスタの仕様最大電圧[V]、qは電荷量(1.609×10-19)[C]、tは前記基板の表面から前記拡散領域の底面までの距離[m]である)で表されるシート不純物濃度Ns[cm-2]を有していることを特徴とする電界効果型トランジスタにより上記課題を解決する。

(もっと読む)

コンタクト形成方法、半導体装置の製造方法、および半導体装置

【課題】 低抵抗率のコンタクトを実現した半導体装置の製造方法を提供する。

【解決手段】半導体と接した第1の金属層を酸化防止用の第2の金属層で覆った状態で、第1の金属層のみをシリサイド化し、酸素混入のないシリサイド層を形成する。第1の金属層の材料として、半導体との仕事関数の差が所定の値となるような金属が用いられ、第2の金属層の材料として、アニール温度で第1の金属層と反応しない金属が用いられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

酸化ゲルマニウムの製造方法およびそれを用いた半導体デバイスの製造方法

【課題】熱的および化学的に安定な酸化ゲルマニウムの製造方法を提供する。

【解決手段】p型Geからなる基板1は、純水および0.1%HFによって洗浄され、その後、超純水によってリンスされる(工程(a)参照)。その後、基板1は、33%の過酸化水素水3に、60秒間、浸漬される(工程(b)参照)。これによって、酸化ゲルマニウム膜4が基板1の一主面に形成される。

(もっと読む)

絶縁膜、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合でもSBDやSILCが生じ難く、高い絶縁破壊耐性(SILC、TZDB、TDDBの改善)が得られる絶縁膜、それを用いた半導体素子、信頼性の高い電子デバイスおよび電子機器を提供すること。

【解決手段】主として半導体材料で構成された半導体基板2に接触して設けられ、シリコン、酸素原子、および、これらの原子以外の少なくとも1種の原子Xを含有する絶縁性無機材料を主材料として構成され、水素原子を含むゲート絶縁膜3であって、その厚さ方向の少なくとも一部において、前記原子Xの総濃度をAとし、前記水素原子の濃度をBとしたとき、B/Aが10以下なる関係を満足する領域を有している。これにより、薄膜化した場合でもSBDやSILCが生じ難く、高い絶縁破壊耐性を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、良好な移動度を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 第一の発明の半導体装置は、基板と、基板表面に形成され、Geを主成分とする半導体領域と、半導体領域上に形成された非金属Ge化合物層と、非金属Ge化合物層上に形成された絶縁膜と、絶縁膜上に形成された電極と、前記電極を挟む前記基板表面に形成されたソース・ドレイン領域とを備えることを特徴とする。非金属Ge化合物層は、例えばSrとGeの化合物、BaとGeの化合物もしくはBaとSiとGeの化合物を有する。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】閾値電圧が異なるトランジスタ毎に閾値電圧を調整する技術を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、を含む閾値電圧が異なる複数種類の電界効果型トランジスタを備え、電界効果型トランジスタの少なくとも1種類は、ゲート絶縁膜に少なくとも1種類の金属が存在する。

(もっと読む)

アルミニウムがドープされた金属炭窒化物ゲート電極の作製方法

半導体デバイス用のアルミニウムがドープされた金属(タンタル又はチタン)炭窒化物ゲート電極の作製方法が記載されている。当該方法は、上に誘電層を有する基板を供する工程、及びプラズマが存在しない状態で前記誘電層上に前記ゲート電極を作製する工程を有する。前記ゲート電極は、金属炭窒化物を堆積する堆積工程、及び前記金属炭窒化物上にアルミニウム前駆体の原子層を吸着させる吸着工程によって作製される。前記堆積工程及び前記吸着工程は、前記アルミニウムがドープされた金属炭窒化物ゲート電極が所望の厚さを有するまで、必要な回数だけ繰り返されて良い。  (もっと読む)

(もっと読む)

半導体素子およびその製造方法

【課題】本発明はトレンチの上部縁部位でゲート絶縁膜が薄くなる現象を防止し、均一な厚さを有するゲート絶縁膜を形成することができる半導体素子、およびその製造方法を提供する。

【解決手段】本発明の半導体素子は、活性領域を画定するトレンチが形成された基板と、該トレンチに埋め込まれた素子分離膜と、前記活性領域上にゲート絶縁膜の成長時に前記トレンチの上部縁部位での酸化を促進するために前記トレンチの上部縁部位に形成された酸化促進領域と、ゲート絶縁膜上に形成されたゲート導電膜と、を備える。

(もっと読む)

前駆体造成物、薄膜形成方法、これを利用したゲート構造物の製造方法、及びキャパシタの製造方法

【課題】 前駆体造成物、薄膜形成方法、これを利用したゲート構造物の製造方法、及びキャパシタの製造方法を提供する。

【解決手段】 半導体装置の製造に利用されることができる薄膜形成用造成物、薄膜形成方法、ゲート構造物の製造方法、及びキャパシタの製造方法において、薄膜造成方法は、前駆体と電子供与化合物を接触させて安定化された前駆体を基板上に提供した後(S20)、前駆体と結合を形成できる反応物質を基板上に導入して、薄膜を形成する(S30)。電子供与化合物によって安定化された前駆体は、熱的安定性が優秀で、ステップカバレッジが優秀な薄膜を形成することができる。半導体製造工程の安全性、効率性及び信頼性を向上させることができる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

半導体装置の製造方法

【課題】Geを含有する半導体基板に効果的な洗浄方法が適用された半導体装置の製造方法を提供する。

【解決手段】Geを含有する半導体基板を、HClガス、HBrガスまたはHIガスの少なくとも一種を含むハロゲン化ガスで洗浄処理を行うことを特徴とする半導体装置の製造方法。Geを含有する半導体基板を、75℃以上110℃以下のHCl溶液で洗浄処理を行うことを特徴とする半導体装置の製造方法。例えば、MISFETのゲート絶縁膜の前処理、ソース・ドレイン電極形成の前処理、コンタクトの金属プラグ形成の前処理に適用される。

(もっと読む)

窪み付きゲート構造を有するメモリデバイス及びその製造方法

【課題】本発明は、IC(integrated circuit)の集積度が向上し、しかもショートチャネル効果を防止することができるMOS半導体デバイスを形成する方法を提供する。

【解決手段】DRAMアクセストランジスタのようなメモリデバイスであって、窪み付きゲート構造を有するメモリデバイスを形成する方法が開示されている。まず、絶縁用のフィールド酸化物領域(21)が半導体基板上に形成され、ついで、窒化シリコン層(18)にパターン形成が行われ、エッチングによりトランジスタトレンチ(22)が得られる。その後にデポジットされたポリシリコンであって、ゲート構造形成のためのポリシリコンを、隣接し隆起した窒化シリコン構造に対して研磨できるようにするため、このトランジスタトレンチに隣接するフィールド酸化物領域に窪みが設けられる。

(もっと読む)

金属酸化物薄膜の成膜方法

【課題】界面準位密度が低い金属酸化物薄膜を成膜することができる金属酸化物薄膜の成膜方法を提供する。

【解決手段】半導体基板上に有機金属化合物を付着させ、重水を含む水よりなる酸化剤によって有機金属化合物を酸化させて金属酸化物薄膜を生成させる金属酸化物薄膜の成膜方法において、該水の金属不純物濃度が1wtppb以下であることを特徴とする金属酸化物薄膜の成膜方法。この水は、浄化装置15において、UV及び混床イオン交換樹脂によって浄化処理される。

(もっと読む)

金属製のソースとドレインを有するトランジスタを製造するための方法

【課題】ソース・ドレイン領域のシリサイド化後に選択的エッチングを不要とする電界効果トランジスタ製造方法を提供する。

【解決手段】a)チャネル、ゲート及びハード・マスク118を含んでなる構造物を基板,誘電体層108の上に作るステップと、b)前記構造物とトランジスタの周囲領域を完全に覆う誘電体を形成するステップと、c)上記誘電体部分に、チャネルの側壁を露出させる二つの穴を形成するステップと、d)上記各穴の各壁部の上に第1の金属層132を蒸着するステップと、e)前記側壁をシリサイド化するステップと、f)前もってシリサイド化した部分に接してトランジスタのソース電極136とドレイン電極138を形成するように、第1の金属層の上に第2の金属層を蒸着するステップと、g)ハード・マスクに対しては阻止される、第2の金属層の化学機械研磨を行なうステップと、を有する製造方法。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

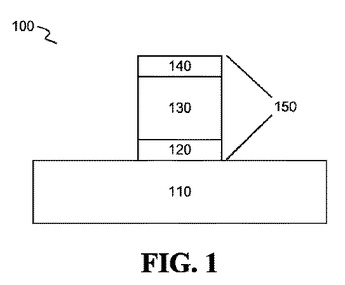

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

141 - 160 / 420

[ Back to top ]