Fターム[5F140BA17]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | エピタキシャル基板 (980) | Si基板上に化合物半導体成長 (318)

Fターム[5F140BA17]に分類される特許

161 - 180 / 318

窒化物半導体素子

【課題】本発明は、低オン抵抗でノーマリーオフ型の窒化物半導体素子を提供する。

【解決手段】本発明の一態様によれば、p型窒化物半導体の第1の半導体層と、第1の半導体層上に設けられたアンドープ窒化物半導体の第2の半導体層と、第2の半導体層上に選択的に設けられたアンドープまたはn型窒化物半導体の第3の半導体層と、第3の半導体層上に設けられた第1の主電極と、第3の半導体層上に設けられた第2の主電極と、第2の半導体層上に設けられた絶縁膜と、絶縁膜上に設けられた制御電極と、を備え、第3の半導体層のバンドギャップは、第2の半導体層のバンドギャップよりも大きく、制御電極は、第1の主電極と第2の主電極との間に位置することを特徴とする窒化物半導体素子が提供される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜におけるリーク電流を抑制し、安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上10にGaN系半導体層15を形成する工程と、GaN系半導体層上15に、TMAと、O2またはO3とを用い、酸化アルミニウムからなるゲート絶縁膜18をALD法により形成する工程と、ゲート絶縁膜18の上にゲート電極24を形成する工程と、を含む。本半導体装置の製造方法によれば、ゲート絶縁膜中のリーク電流を抑制し、安定なFET特性を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上にGaN系半導体層を形成する工程と、ALD装置内で、ゲート絶縁膜の成長温度に比べ高い温度で熱処理を実施し、前記GaN系半導体層の表面のフッ素を除去する工程S20と、前記フッ素を除去する工程S20の後、前記ALD装置内で、前記GaN系半導体層の表面に前記ゲート絶縁膜を形成する工程S16と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

半導体電子デバイスおよび半導体電子デバイスの製造方法

【課題】耐圧性が高く反りが小さくオン抵抗が低い半導体電子デバイスおよびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された、該基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、前記バッファ層上に形成された、窒化物系化合物半導体からなる半導体動作層と、窒化物系化合物半導体からなり、前記バッファ層直下から前記電子走行層内部までのいずれかの位置に形成され、凹凸形状の境界面を有する下層領域と上層領域とを有し、該下層領域から該上層領域へ延伸する貫通転位が該境界面において屈曲している転位低減層と、を備える。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】放熱効率を向上し且つ歩留りや信頼性の低下を防止することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】裏面に凹部DP1が形成されたシリコン基板101と、シリコン基板101における裏面と反対側の上面上に成長されたp型半導体層103と、p型半導体層103の上方または側方に互いに離間して形成されたソース電極108sおよびドレイン電極108dと、を含むMOSFETと、を備える。p型半導体層103は、シリコン基板101に対して格子定数および熱膨張係数のうち少なくとも1つが異なる。凹部DP1は、シリコン基板101の厚み方向から見て少なくともソース電極108sおよびドレイン電極108dで挟まれた領域を内包する領域に形成されている。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、基板上に形成されたi型または所定の導電型を有する半導体層と、エピタキシャル成長によって半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によってドレイン電極側のコンタクト層と半導体層との間にゲート電極と重畳するように形成された、所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、エピタキシャル成長によって半導体層上の電界緩和層に隣接する領域に形成された、i型または所定の導電型を有する媒介層と、媒介層上に形成したゲート絶縁膜と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物濃度のプロファイルを有するソース領域およびドレイン領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板の表面近傍に不純物を注入して不純物注入領域を形成する工程と、前記半導体基板にエッチングを施すことにより前記不純物注入領域の底部よりも深い溝を形成し、前記不純物注入領域を分断してソース領域およびドレイン領域を形成する工程と、前記溝の内部にSi系単結晶をエピタキシャル成長させてエピタキシャル結晶層を形成する工程と、前記エピタキシャル結晶層の上部にゲート絶縁膜およびゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】MIS−HEMTにおいて、閾値電圧の低下を抑制する。

【解決手段】半導体装置は、基板19と、この基板上に形成されており、電子走行層13及び電子供給層15が順次積層されて形成された積層構造体17とを含む下地11を具えている。この下地の下地面には、互いに離間し、かつ対向して第1及び第2主電極が形成されている。そして、下地面11aの、これら第1主電極41a及び第2主電極41b間に挟まれた領域内に、ゲート形成用凹部27が形成されている。更に、半導体装置はゲート絶縁膜29を具えている。そして、このゲート絶縁膜は、最小でも2.9g/cm3の結晶密度で形成されている。また、半導体装置は、ゲート絶縁膜が形成された前記ゲート形成用凹部を埋め込むゲート電極43を具えている。

(もっと読む)

半導体デバイス

【課題】エンハンスメントモードトランジスタを作製する方法を提供する。

【解決手段】基板1上の第1活性層3と、第1活性層3の上に、該第1活性層3に比較して高いバンドギャップを有する第2活性層4配設し、実質的にGaを含まないで少なくともAlを含む第2活性層4と、第2活性層4の少なくとも一部の上のゲート絶縁層5であって、第2活性層4の少なくとも一部を熱酸化して形成されたゲート絶縁層5と、ゲート絶縁層5の少なくとも一部の上のゲート電極6と、第2活性層4の上のソース電極7およびドレイン電極8とを含み、前記半導体デバイス10は、更に、動作時でゲート電極6とソース電極7が同電圧の場合、第1活性層3と第2活性層4の間で、ゲート電極6の外側でゲート電極6の位置以外に、2次元電子ガス2DEG層を含む。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成された所定の導電型を有する半導体層と、エピタキシャル成長によって前記半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、前記所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によって前記ドレイン電極側のコンタクト層と前記半導体層との間にゲート絶縁膜を介してゲート電極と重畳するように形成された、前記所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、を備える。

(もっと読む)

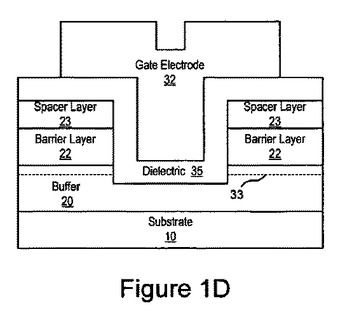

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

トランジスタとその製造方法

【課題】 p型窒化物半導体層の表層部にn型のソース領域とn型のドレイン領域が設けられているトランジスタにおいて、しきい値が低く、p型窒化物半導体層内にホールが蓄積されない技術を提供する。

【解決手段】 トランジスタ10は、p型窒化物半導体層6の表層部にn型のソース領域18とn型のドレイン領域12を備えている。トランジスタ10は、p型不純物の供給量を経時的に変更することによって、表層部よりも深部にp型不純物の濃度が濃い高濃度領域4を有するp型窒化物半導体層6を基板2上に結晶成長させる結晶成長工程と、基準電位に接続する基準電極22を高濃度領域4に接するように形成する電極形成工程を経て製造される。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】電子移動度が高く、リーク電流が小さく、オン抵抗が低い電界効果トランジスタおよび電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有する電界効果トランジスタであって、基板上に形成したp型窒化化合物半導体層と、ソース電極およびドレイン電極下部に位置し、イオン注入により形成されたn型コンタクト領域と、前記p型窒化化合物半導体層上にエピタキシャル成長によって積層されるとともに、一端部がドレイン電極側のn型コンタクト領域に隣接し、他の一端部がゲート電極の前記ドレイン電極側にオーバーラップするように形成され、前記n型コンタクト領域よりもキャリア濃度が低いn型窒化化合物半導体からなる電界緩和層と、を備える。

(もっと読む)

電界効果型トランジスタ

【課題】ヘテロ構造を含む電界効果型トランジスタでありながらノーマリオフタイプのトランジスタを提供する。

【解決手段】ヘテロ構造を含む電界効果型トランジスタは、基板(1)上に順次積層されたバッファ層(2)、第1の窒化物半導体層(3)、および第2の窒化物半導体層(4)を含み、第1の窒化物半導体層の格子定数a1と第2の窒化物半導体層の格子定数a2とがa1>a2の関係にあり、第2の窒化物半導体層上にソース電極(5)とドレイン電極(5)とが形成されかつそれらの電極間の少なくとも一部にペロブスカイト構造の酸化物からなる厚さ500nm以上1μm以下のピエゾ効果膜(6)が形成されており、そのピエゾ効果膜は第1と第2の窒化物半導体層の格子定数差(a1−a2)に起因して第2の窒化物半導体層に加わる引っ張り応力に比べて同等以上の大きさの圧縮応力を及ぼす。

(もっと読む)

導電性コンタクトの組み込みのための構造体及びプロセス

【課題】 キーホール・シームの形成を排除した信頼性が高い高アスペクト比のコンタクト構造体を含む半導体構造を提供する。

【解決手段】 キーホール・シームの形成は、本発明においては、誘電体材料内部に存在する高アスペクト比のコンタクト開口部内に高密度化貴金属含有ライナを設けることによって排除される。高密度化貴金属含有ライナは拡散バリアの上に配置され、これら両方の要素は、本発明のコンタクト構造体の導電性材料を、下層の半導体構造体の導電性材料から分離する。本発明の高密度化貴金属含有ライナは、第1の抵抗率を有する貴金属含有材料の堆積、及び、堆積した貴金属含有材料の抵抗率をより低い抵抗率に減少させる高密度化処理プロセス(熱又はプラズマ)を、堆積した貴金属含有材料に施すことによって形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル移動度の低下を防止して、パンチスルーストッパを形成する。

【解決手段】半導体基板100と、前記半導体基板上に形成され、長手方向と短手方向とを有し、順に積層されたボロンを含むシリコン炭化膜とシリコン膜とを有する半導体層110と、少なくとも前記半導体層の前記短手方向の側面に形成されたゲート電極150と、前記半導体層に形成され、前記ゲート電極の前記長手方向に隣接して形成されたソース・ドレイン領域111、112と、前記半導体層の側面であって、前記ゲート電極と前記半導体基板との間に形成された素子分離絶縁膜130と、を備える。

(もっと読む)

半導体基板、半導体基板の製造方法および半導体装置

【課題】半導体−絶縁体界面の界面準位が低減した半導体基板とその製造方法および半導体装置を提供する。

【解決手段】砒素を含む3−5族化合物の半導体層と、酸化物、窒化物または酸窒化物の絶縁層と、を備え、前記半導体層と前記絶縁層との間に砒素の酸化物が検出されない半導体基板が提供される。当該第1の形態において半導体基板は、前記半導体層と前記絶縁層との間に存在する元素を対象としたX線光電子分光法による光電子強度の分光観察において、砒素に起因する元素ピークの高結合エネルギー側に、酸化された砒素に起因する酸化物ピークが検出されないものであってよい。

(もっと読む)

半導体装置及びその製造方法

【課題】MIS構造のHEMTにおいて電流コラプスを抑制するために下地との離間距離が好適に調節されたフィールドプレートを設ける。

【解決手段】下地11の上側に互いに離間しかつ対向して形成された第1及び第2主電極29a,29bを具える。第1及び第2主電極から露出した下地の上側表面にはゲート絶縁膜13が形成されておりゲート絶縁膜の上側にはゲート電極31が設けられている。ゲート電極及びゲート絶縁膜を含む下地の全面を一体的に覆うようにゲート電極の厚みよりも小さい膜厚でサブ絶縁膜33が形成されておりサブ絶縁膜はゲート電極の上側表面を覆う第1サブ絶縁膜35、ゲート電極の第1及び第2主電極とそれぞれ対向する両側側面を覆う第2サブ絶縁膜37、及びゲート電極から露出したゲート絶縁膜を覆う第3サブ絶縁膜39を含む。第1サブ絶縁膜から一方の側の第2サブ絶縁膜、及びこの一方の側の第3サブ絶縁膜に渡って一体的に覆うようにフィールドプレート43が形成されている。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】GaN系化合物半導体による電界効果トランジスタにおいて、ゲート電極及びソース電極間及び/又はゲート電極及びドレイン電極間に、外部負荷からの逆起電力等のサージ電圧や静電気からトランジスタを有効に保護するためのダイオードを内蔵させる。

【解決手段】基板上に少なくともバッファ層を含む下部半導体層104と、電子走行層及び電子供給層により形成された半導体動作層105と、当該半導体動作層105の上に形成されたソース電極13、ドレイン電極12及びゲート電極14を有する窒化ガリウム系化合物半導体からなる電界効果トランジスタにおいて、ゲート電極14及びソース電極13間と、ゲート電極14及びドレイン電極12間と、の何れか一方又は両方に並列接続されるダイオードが、前記の各電極間であって半導体動作層105から下部半導体層104に至る溝により形成される。

(もっと読む)

161 - 180 / 318

[ Back to top ]