Fターム[5F140BA17]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | エピタキシャル基板 (980) | Si基板上に化合物半導体成長 (318)

Fターム[5F140BA17]に分類される特許

101 - 120 / 318

CMOS用歪トランジスタの集積化

【課題】n型MOSデバイス(NMOS)の電子の移動度の向上、およびp型MOSデバイス(PMOS)のホールの移動度の向上した半導体装置および製造方法の提供。

【解決手段】(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

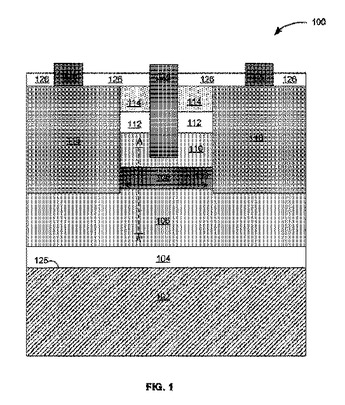

集積回路デバイスに歪みを与える技術及び構成

本開示の実施形態により、例えば横型電界効果トランジスタなどの集積回路デバイスに歪みを与える技術及び構成が提供される。集積回路デバイスは、半導体基板と、該半導体基板と結合された第1のバリア層と、第1のバリア層に結合された、第1の格子定数を持つ第1の材料を有する量子井戸チャネルと、量子井戸チャネルに結合されたソース構造とを含む。ソース構造は、第1の格子定数とは異なる第2の格子定数を持つ第2の材料を有し、量子井戸チャネルに歪みを与える。その他の実施形態も開示される。  (もっと読む)

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

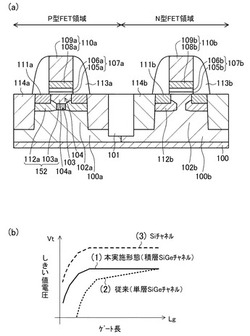

【課題】Geを含む半導体で構成されるチャネル領域を有するP型FETにおいて、逆短チャネル特性の発生を抑制しつつ、短チャネル特性を改善する。

【解決手段】半導体装置は、半導体基板100上に形成されたP型FETを備えている。P型FETは、半導体基板100上に形成され、Geを含有する第1の半導体層103と、第1の半導体層103上に形成され、第1の半導体層103よりも低濃度のGeを含有する第2の半導体層104と、第2の半導体層104上にゲート絶縁膜107aを間に挟んで形成されたゲート電極110aと、第2の半導体層104のうちゲート電極110aの両側方に位置する部分に形成されたp型エクステンション領域111aと、第1の半導体層103内に設けられ、且つp型エクステンション領域111aの下に形成されたn型不純物領域152とを有している。

(もっと読む)

GaN系MOS型電界効果トランジスタ

【課題】ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOSFETを提供する。

【解決手段】p−GaNからなる電子走行層13とゲート電極18との間にゲート絶縁膜15が形成されたGaN系MOSFET10である。ゲート電極18は、AlGaInP混晶からなる。ゲート電極18は、p型AlGaInP混晶からなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20と、この上に形成された金属層(AuGe/Au電極)21とを有する。AlGaInP混晶の混晶比を変化させることにより、しきい値電圧を制御することが出来る。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

量子井戸型半導体装置

量子井戸型半導体装置、および量子井戸型半導体装置を形成する方法について示した。本方法は、基板の上部に配置され、量子井戸チャネル領域を有するヘテロ構造を提供するステップを有する。また、この方法は、ソースおよびドレイン材料領域を形成するステップを有する。また、この方法は、ソースおよびドレイン材料領域に溝を形成するステップを有し、ドレイン領域から分離されたソース領域が提供される。また、この方法は、溝内のソース領域とドレイン領域の間に、ゲート誘電体層を形成するステップと、溝内のゲート誘電体層の上部に、ゲート電極を形成するステップとを有する。  (もっと読む)

(もっと読む)

III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス、及びその製造方法

【課題】III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス及びその製造方法を提供する。

【解決手段】III−V族材料のエネルギーレベルの密度とドーピング濃度をIII−V族材料とIV族材料のヘテロエピタキシと素子の構造設計によって高める。本発明の方法は、基板100上にダミーゲート材料層を堆積し、フォトリソグラフィでダミーゲート材料層にダミーゲートを区画することと、ダミーゲートをマスクとして使用し、セルフアライン型イオン注入によってドーピングを行い、高温で活性化を行い、ソース−ドレイン108を形成することと、ダミーゲートを除去することと、ソース−ドレインのペアの間の基板にエッチングで凹陥部を形成することと、凹陥部にエピタキシャル法によりチャネル含有スタック素子112を形成することと、チャネル含有スタック素子上にゲート120を形成することと、を含む。

(もっと読む)

半導体素子及びトランジスタ

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができる半導体素子及びトランジスタを提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができる半導体素子及びトランジスタを提供すること、を目的とする。

【解決手段】半導体基板上に形成されて第1半導体パターンを含む3次元直線状の第1構造物と、第一構造物の中心部を貫通するように配置され、第1半導体パターンと異なる結晶構造を有する第2半導体パターンを含む第2構造物と、第1構造物に対して直交する方向に延長して3面で第2構造物の一部を囲むゲートを含むトランジスタとする。

(もっと読む)

高移動度チャネル(High−MobilityChannels)を有する装置のソース/ドレイン工学

【課題】高移動度チャネルを有する装置のソース/ドレイン工学を提供する。

【解決手段】集積回路構造は、基板及び基板の上方のチャネルを備える。チャネルは、III族元素とV族元素から構成される第一III-V族化合物半導体材料からなる。ゲート構造はチャネルの上方に設置される。ソース/ドレイン領域はチャネルに隣接し、本質的に、シリコン、ゲルマニウム、及び、それらの組み合わせからなる群から選択されるドープされたIV族半導体材料から形成されるIV族領域を含む。

(もっと読む)

トランジスタの製造方法

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができるトランジスタの製造方法を提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができるトランジスタの製造方法を提供すること、を目的とする。

【解決手段】半導体基板上に第1半導体層及び第1半導体層と異なる格子定数と結晶構造を有する第2半導体層を順次形成する段階と、第2半導体層及び第1半導体層をエッチングして格子定数の差によって第1半導体層の結晶構造が変形された変形結晶構造を有し、直線状の第1半導体パターンを形成する段階と、第1半導体パターン上に第1半導体層と同一な結晶構造を有する第3半導体層を形成する段階とを含む。

(もっと読む)

ハニカムヘテロエピタキシーを含む半導体装置

【課題】ハニカムヘテロエピタキシーを含む半導体装置を提供する。

【解決手段】ハニカムヘテロエピタキシーを含む半導体装置とその製造方法が開示される。一実施例は、貫通する複数のナノサイズの開口を有するマスクをシリコン基板上に定義するステップと、定義ステップ後、マスク開口を介して露出したシリコン基板表面の一部に、本質的に無欠陥の非シリコン半導体ナノアイランドを作成するステップと、作成ステップ後、ナノアイランド上に、高kゲート誘電体を蒸着するステップと、蒸着ステップ後、ナノアイランド上に、トランジスタを構成するステップとを備える方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】駆動電流の増大を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に線状に形成された第2部分12bと、を有する第2半導体層12と、前記第2半導体層の前記第2部分の周囲に絶縁膜17を介して形成されたゲート電極18と、を具備し、前記第2半導体層の前記第2部分の膜厚は、前記第2半導体層の前記第1部分の膜厚より小さい。

(もっと読む)

蓄積型FINFET、回路、及びその製造方法

【課題】FinFET、集積回路、およびFinFETの形成方法を提供する。

【解決手段】基板120、前記基板上にあり、ソース106とドレイン110との間のチャネル108を含み、前記ソース106、前記ドレイン110、および前記チャネル108は、第1型ドーパントを有し、前記チャネル108は、ゲルマニウム、シリコンゲルマニウム、またはIII−V族半導体の少なくとも1つを含むフィン構造、前記チャネル108上のゲート誘電体層114、および前記ゲート誘電体層114上のゲート116を含むFinFET。

(もっと読む)

高ゲルマニウム濃度のSiGeストレッサの形成方法

【課題】SiGeストレッサの形成方法と集積回路のトランジスタ構造を提供する。

【解決手段】SiGeストレッサを形成する方法であって、前記方法は、ソース領域とドレイン領域間にチャネルを有する半導体基板上のソース領域とドレイン領域の少なくとも1つに第1SiGe層を堆積するステップ、及び前記第1SiGe層の上部を酸化層に変換し、前記第1SiGe層の底部を第2SiGe層に変換するステップを含み、前記第2SiGe層は、前記第1SiGe層より高いGe濃度を有する方法。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いたノーマリオフ型のトランジスタを備えた半導体装置において、駆動時のゲート電流を低減しつつ、トランジスタの過渡応答特性を安定させる。

【解決手段】半導体装置は、基板101と、基板101の上に積層された複数の窒化物半導体層からなり、且つチャネル領域を含む第1の窒化物半導体層104Sと、第1の窒化物半導体層104Sの上に形成され、且つチャネル領域と逆導電型の第2の半導体層105と、第2の半導体層105に接するように形成され、金属層107からなる導電層と、導電層の上に形成された絶縁体層110と、絶縁体層110の上に形成されたゲート電極111と、第2の半導体層105の両側方に形成されたソース電極108及びドレイン電極109とを備えている。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高品質な特性を有する電界効果トランジスタ及びその方法を提供する。

【解決手段】素子分離領域106間のソース/ドレイン領域114、及びポケット領域116を含んでいる半導体基板102と、素子分離領域間の半導体基板の上面のトレンチ110内にあって、(100)面を有する底面及び上面と、2つ以上の平面を有する側面とを有するシリコンゲルマニウム層112と、ゲート絶縁層120、ゲート電極122、及びサイドスペーサ128を含むシリコンゲルマニウム層上のゲート構造と、ゲート構造によって覆われていないシリコンゲルマニウム層及び半導体基板の上部分上のメタルシリサイド124とを備え、シリコンゲルマニウム層は、チャネル長方向において、ゲート構造の下で側面を有していない。

(もっと読む)

窒化物系半導体電界効果トランジスタ

【課題】ノーマリオフ動作を達成し、十分なチャネル電流が得られ、かつ、しきい値電圧制御が容易な窒化物系半導体ヘテロ接合電界効果トランジスタを提供する。

【解決手段】GaN層10とAlGaN層11のヘテロ接合界面をチャネルとする電界効果トランジスタにおいて、負の電荷を有する第三の層40をゲート電極34下のゲート絶縁膜31中に設けるとともに、ヘテロ接合を形成する窒化物半導体内にフッ素イオンF−等の負のイオン41を注入する。第三の層40はCl−等の負のイオンが注入される。ゲート絶縁膜31中およびAlGaN層11中に適量の負のイオンを注入することにより、しきい値電圧が上がりノーマリオフ動作を確実に達成するとともに、十分なチャネル電流が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

101 - 120 / 318

[ Back to top ]