Fターム[5F140BA17]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | エピタキシャル基板 (980) | Si基板上に化合物半導体成長 (318)

Fターム[5F140BA17]に分類される特許

121 - 140 / 318

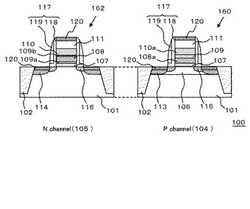

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタ特性を向上させる。

【解決手段】STI109と、STI109によって互いに分離されたp型ウェル102及びn型ウェル103と、p型ウェル102及びn型ウェル103上に形成されたSiGe膜108とを有するSi基板101を用意する工程と、n型ウェル103上に位置するSiGe膜108をSiO2膜116で被覆する工程と、SiO2膜116をマスクとして酸化処理を行うことによりp型ウェル102上に形成されたSiGe膜108を酸化し、SixGeyOz膜117を形成する工程((c))と、SixGeyOz膜117を除去する工程((d))と、を行い、半導体装置を製造する。

(もっと読む)

半導体装置

【課題】チャネル領域に歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】第一半導体からなる半導体基板1と、半導体基板1上に形成されたゲート絶縁膜2と、ゲート絶縁膜2上に形成されたゲート電極3と、ゲート絶縁膜2を介したゲート電極3下のチャネル領域4と、チャネル領域4に隣接する不純物原子が注入されたソース/ドレイン拡散層領域5,6と、を有し、ソース/ドレイン拡散層領域5,6に第一半導体と格子定数の異なる第二半導体の結晶からなる一軸歪み誘発層7を含み、一軸歪み誘発層7の底部と半導体基板1との界面で格子不整合が起こっており、一軸歪み誘発層7を形成した際に生じる半導体基板1との格子整合に起因する歪みが緩和している。

(もっと読む)

傾斜三元または四元マルチゲートトランジスタ

【課題】 フィン電界効果トランジスタ(FinFET)とその形成方法を提供する。

【解決手段】 半導体基板、前記半導体基板上の絶縁領域、及び前記半導体基板上に位置し、前記絶縁領域間の間隙に少なくとも一部を有し、第1III-V族化合物半導体材料を含むエピタキシー領域を含み、前記エピタキシー領域は、そこと前記半導体基板が第1格子不整合を有する下部分、及び前記下部分上に位置し、そこと前記半導体基板が前記第1格子不整合と異なる第2格子不整合を有する上部分を更に含む集積回路構造。

(もっと読む)

半導体素子

【課題】構造が複雑なフィールドプレート構造を用いずに、ゲート電極端での電界集中を緩和することができる半導体素子を提供する。

【解決手段】MOSFET10は、基板上にバッファ層を介して形成されたp−GaN層14と、ゲート絶縁膜15と、ゲート電極20と、ソース電極と、ドレイン電極17とを有する。ゲート電極20は、ゲート電圧を印加するための電極で、ドーパントが高濃度にドーピングされたポリシリコンを用いた第1の領域(ゲート電極1)21と、高抵抗のポリシリコンを用いた第2の領域(ゲート電極2)22とを有する。両ゲート電極21、22間に抵抗勾配部23がある。第2の領域22では緩やかに電位が変化する電位勾配30ができる。これにより、ゲート電極端31において、電圧の微分である電界がピーク32で示すように小さくなり、ゲート電極端31での電界集中を緩和することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含むチャネル形成領域を有する電界効果トランジスタにおいて、基板リーク電流を低減する。

【解決手段】半導体装置150は、Geを含む第1導電型の第1の半導体領域101と、第1の半導体領域101上にゲート絶縁膜121を介して形成されたゲート電極122と、第1の半導体領域101におけるゲート電極122の両側方に形成された第2導電型の拡散領域107と、第1の半導体領域101と拡散領域107との間に形成された第1導電型の第2の半導体領域108とを備える。第2の半導体領域108は、第1の半導体領域101におけるゲート電極122下方のチャネル形成領域よりも高い濃度のSiを含有する。

(もっと読む)

改善されたオン/オフ電流比の高移動度多重ゲートトランジスタ

【課題】 金属酸化物半導体(MOS)トランジスタとその形成方法を提供する。

【解決手段】 多重ゲートトランジスタは、基板、第1半導体材料で形成された中央フィン、及び中央フィンの対向側壁上の第1部分と第2部分を含み、第1半導体材料とは異なる第2半導体材料を包含する半導体層を含む基板上の半導体フィン、この半導体フィンの側壁の周囲を包むゲート電極、及び半導体フィンの対向端のソース領域とドレイン領域を含み、中央フィンと半導体層の各々は、ソース領域からドレイン領域に延伸する。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板と、前記基板上に形成されたバッファ層と、前記バッファ層上に形成された高抵抗層又は下地層と、前記高抵抗層又は下地層上に形成された、炭素を含有するキャリア濃度制御層と、前記キャリア濃度制御層上に形成されたキャリア走行層と、前記キャリア走行層上に形成された、前記キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層と、前記キャリア供給層から所定の深さに到るまで形成されたリセス部と、前記キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記キャリア供給層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備える。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法

【課題】低いオン抵抗と高い耐圧性とを有する電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法を提供する。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板101と、前記基板上に形成された高抵抗層103と、前記高抵抗層上に形成された、炭素濃度が1×1018cm−3以下であり層厚が10nmより厚く、100nm以下であるチャネル層104を含む半導体動作層106と、前記半導体動作層に前記チャネル層の内部に到る深さまで形成されたリセス部107と、前記半導体動作層上に前記リセス部を挟んで形成されたソース電極108およびドレイン電極109と、前記半導体動作層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜110と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極111と、を備える。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

電界効果トランジスタ

【課題】大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層13の表面領域に形成されたソース18s及びドレイン18dと、半導体活性層13上にゲート酸化膜14を介して形成されたゲート電極15と、ゲート電極15とドレイン18dの間の半導体活性層13上に形成されたパッシべーション膜20とを備える。電界効果トランジスタ10では、パッシベーション膜20を構成する二酸化シリコンの膜質が、ゲート酸化膜14を構成する二酸化シリコンの膜質よりも密度が粗である。

(もっと読む)

電界効果トランジスタ

【課題】耐電圧を高めて、大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層11の表面領域に形成されたソース16s及びドレイン16dと、半導体活性層11上にゲート酸化膜12を介して形成されたゲート電極13とを備える。電界効果トランジスタ10は、ゲート電極13とドレイン16dとの間の半導体活性層11内に形成された電界緩和層20を有する。電界緩和層20は、正の電荷が生じる第1の層21と負の電荷が生じる第2の層22とが、膜厚方向に交互に配置される積層構造を有する。

(もっと読む)

補償型ゲートMISFET及びその製造方法

低いゲートリークを有する例えばGaNトランジスタなどのMISFETが提供される。一実施形態において、ゲートコンタクトの下且つバリア層の上に、補償型のGaN層を有することで、ゲートリークが低減される。他の一実施形態において、ゲートコンタクトの下且つバリア層の上に半絶縁性の層を用いることによって、ゲートリークが低減される。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】 ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタの下面または上面にボディ電極8を設ける。下面にボディ電極8を設ける場合、p型Si基板2上にAlN層31およびGaN層32の繰り返しによるバッファ層3を介してp−GaN層4を設け、バッファ層3の最上層のAlN層31を薄くし、p型Si基板の下面にボディ電極8を形成する。上面にボディ電極8を設ける場合、サファイア基板21上にp−GaN層4を設け、ソース電極5およびドレイン電極6下の部分にAlGaN層13を設け、AlGaN層13上にボディ電極8を設ける。アバランシェにより生じる正孔20をボディ電極8より引き抜く。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コスト増や大型化を招くことなく、耐圧特性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体層13と、半導体層13上のゲート電極15、ソース電極16sおよびドレイン領域16dと、を備えたMOSFET1は、半導体層13中であってこの半導体層13の上面および下面それぞれから離間する中間領域に所定の導電性を備えたドーパント(例えばシリコン(Si))を含む縦方向電界緩和領域19を備えている。

(もっと読む)

半導体装置

【課題】SiGeのチャネルを有する半導体装置の高性能化及び高信頼化をはかる。

【解決手段】シリコンを主成分とする半導体基板101の一主面に設けられ、素子分離絶縁膜102によって区画された素子形成領域103と、チャネル領域となるSi及びGeを主成分とし素子形成領域103上に設けられた半導体膜104と、半導体膜104上にゲート絶縁膜105を介して設けられたゲート電極106と、チャネル領域を挟んで半導体膜104及び基板101に形成されS/D領域110と、ゲート電極106の両側面に設けられた側壁絶縁膜109と、S/D領域110上の側壁絶縁膜109で区画されたS/Dコンタクト領域上に半導体膜104と金属との反応により形成され、且つS/Dコンタクト領域以外の半導体膜104よりも薄い膜厚に形成された金属化合物膜111とを備えた。

(もっと読む)

GaN系電界効果トランジスタ

【課題】低オン抵抗・高耐圧で動作可能なGaN系化合物半導体デバイスを提供する。

【解決手段】基板上に形成されたバッファ層、チャネル層と、前記チャネル層上に形成され、ドリフト層と、前記ドリフト層上に配置されたソース電極およびドレイン電極と、ドリフト層に形成されたリセス部の内表面および前記ドリフト層の表面に形成された絶縁膜と、前記絶縁膜上に形成されたフィールドプレート部を有するゲート電極とを備えたGaN系電界効果トランジスタにおいて、前記ドリフト層は、前記リセス部と前記ドレイン電極との間に、シートキャリア密度が5×1013cm−2以上、1×1014cm−2以下のn型GaN系化合物半導体からなる電界緩和領域を有し、前記ドリフト層の前記電界緩和領域上に形成された前記絶縁膜の厚さが300nm以上であることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

半導体素子及び半導体装置

【課題】高い電流駆動力を有するn型半導体素子を提供する。

【解決手段】第1の主面を有し、III族の不純物を含み、1.2<N<10を満たすNを用いて(11N)面と表される、ないしはそれと結晶学的に等価な第1の面方位のみを前記第1の主面に有する、シリコンとゲルマニウムとの混晶層と、前記第1の主面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記混晶層の[110]方向ないしそれと結晶学的に等価な方向に、前記ゲート電極を挟む様に形成され、V族の不純物を含む半導体よりなるソース・ドレイン領域と、を有し、前記混晶層は面内方向に圧縮歪みが印加されていることを特徴とする。

(もっと読む)

121 - 140 / 318

[ Back to top ]