Fターム[5F140BB05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSHC(垂直表面水平電流) (437)

Fターム[5F140BB05]に分類される特許

101 - 120 / 437

半導体装置及び半導体装置の製造方法

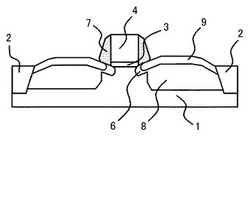

【課題】微細化が進んだトランジスタにおいて、他の問題を生じさせずに抵抗を低減する。

【解決手段】シリサイド層9は、ソース・ドレイン領域8の表層及びソース・ドレイン拡張領域6に形成されている。シリサイド層9は、半導体基板1に垂直かつゲート幅方向に対して平行な断面でみたときに、ソース・ドレイン領域8の中央部からチャネル領域に近づくにつれて半導体基板1の内側(図中下側)に近づいており、かつチャネル領域側の端部がソース・ドレイン拡張領域6に延在している。

(もっと読む)

半導体装置

【課題】パワーデバイスとCMOSデバイスとを混載することができ、パワーデバイスのアバランシェ耐量及びESD耐量が高い半導体装置を提供する。

【解決手段】半導体基板11の上部にP型のウェル12を形成し、ウェル12にSTI13を選択的に設け、STI13の開口部14内にSTI13の側面13aに接するようにN+型のソース層17及びドレイン層18を相互に離隔して形成する。また、ソース層17とドレイン層18との間に、P+型のコンタクト層19を形成する。コンタクト層19はソース層17に接し、STI13からは離隔するように形成する。更に、ソース電極21をソース層17及びコンタクト層19に接続し、ドレイン電極22をドレイン層18に接続し、STI13上に側面13aに沿ってゲート電極23を設ける。

(もっと読む)

バルクFinFET中のSiフィンのフィン下部近くのSTI形状

【課題】半導体フィンとフィン型電界効果トランジスタの構造、及び、製造方法を提供する。

【解決手段】集積回路構造の形成方法は、頂面を有する半導体基板を提供するステップと、半導体基板中に、第1絶縁領域と第2絶縁領域を形成するステップと、第1絶縁領域と第2絶縁領域を陥凹するステップと、からなる。第1絶縁領域と第2絶縁領域の残り部分の頂面は平らな表面であるか、或いは、窪み表面である。第1絶縁領域と第2絶縁領域の除去部分間の半導体基板の部分、及び、隣接する部分は、フィンを形成する。

(もっと読む)

異なる誘電材料を用いたインター装置STI領域とイントラ装置STI領域の形成

【課題】異なる誘電材料を用いたインター装置STI領域とイントラ装置STI領域の形成を提供する。

【解決手段】集積回路構造は、第1装置領域に第1部分、第2装置領域に第2部分を有する基板と、第1装置領域中で、且つ、基板上に位置する2つの絶縁領域と、からなる。2つの絶縁領域は、第1k値を有する第1誘電材料を含む。半導体ストリップは、2つの絶縁領域間に位置し、且つ、2つの絶縁領域に隣接し、2つの絶縁領域の頂面上に、半導体フィンを形成する半導体ストリップの上部分を有する。追加の絶縁領域が、第2装置領域中で、且つ、基板上に位置する。追加の絶縁領域は、第1k値より大きい第2k値を有する第2誘電材料を含む。

(もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

金属ゲートとストレッサーを有するゲルマニウムフィンFET

【課題】金属ゲートとストレッサーを有するゲルマニウムフィンFETを提供する。

【解決手段】集積回路構造は、n型フィン電界効果トランジスタ(fin field effect transistor、FinFET)とp型FinFETからなる。n型FinFETは、基板上の第一ゲルマニウムフィン、第一ゲルマニウムフィンの上面と側壁上の第一ゲート誘電体、及び、第一ゲート誘電体上の第一ゲート電極からなる。p型FinFETは、基板上の第二ゲルマニウムフィン、第二ゲルマニウムフィンの上面と側壁上の第二ゲート誘電体、及び、第二ゲート誘電体上の第二ゲート電極からなる。第一ゲート電極と第二ゲート電極は、ゲルマニウムの固有エネルギーレベルに近い仕事関数を有する同一材料で形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】複数のトレンチを含むトレンチゲート構造のトランジスタにおける特性ばらつきを低減する。

【解決手段】トレンチゲート構造を有するトランジスタを含む半導体装置100において、ゲート幅方向において、複数のトレンチ162は、両側方に形成された素子分離絶縁膜110とそれぞれ接して形成されたトレンチ162aおよびトレンチ162bを含み、トレンチ162aおよびトレンチ162bのゲート幅方向の幅が、これらの間に形成された他のトレンチ162cのゲート幅方向の幅以上となるように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの耐圧を高く保ちつつ、素子分離能力の低下を防ぐ。

【解決手段】基板102の一面のチャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162内部を埋め込むように形成されたゲート電極122を含むトランジスタにおいて、ソース領域112およびドレイン領域113の下方には、それぞれ第1のオフセット領域106および第2のオフセット領域107が形成される。ここで、第1のオフセット領域106および第2のオフセット領域107は、それぞれ、素子分離絶縁膜110と接する領域における下端が素子分離絶縁膜110の下端よりも上方に位置するように形成されるとともに、トレンチ162端部の下方にも形成されている。

(もっと読む)

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタを提供する。

【解決手段】本発明は、フィン型電界効果トランジスタの分離構造に関する。フィン型電界効果トランジスタの例は、主表面からなる基板と、基板の主表面から突出する複数のフィン構造と、フィン構造の間に位置する複数の分離構造と、からなる。各フィン構造は、変化位置により分けられる上部分と下部分からなり、この変化位置は、フィン構造の側壁と基板の主表面の角度85度のところにあり、上部分は、この基板の主表面と実質上、垂直な側壁、及び、第一幅を有する頂面を有し、下部分は、上部分の両側のテーパ型側壁、及び、第一幅より大きい第二幅を有する底部を有する。複数の分離構造は、それぞれ、基板の主表面から、変化位置上の点に延伸する。

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ホットキャリアの発生を大幅に抑制して、トランジスタの長期信頼性を高める。

【解決手段】基板102の一面のチャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162内部を埋め込むように形成されたゲート電極122を含むトランジスタにおいて、ソース領域112およびドレイン領域113の下方には、それぞれ第1のオフセット領域106および第2のオフセット領域107が形成される。ここで、第2のオフセット領域107は、ゲート長方向の断面において第2のオフセット領域107とチャネル領域108とのPN境界線のトレンチ162底部の角部を始点としたソース領域112に向けた横方向の距離をx、トレンチ162底部の角部を始点とした下方向の距離をyとして、合計距離x+yが0.1μm以上である。

(もっと読む)

半導体装置

【課題】駆動電力の高いフィン型のトランジスタを提供する。

【解決手段】所定の間隔で配置され、それぞれの中央部がチャネル領域、その両側部がソース/ドレイン領域となるフィン状の第1の半導体11層及び第2の半導体層11と、第1の半導体層11及び第2の半導体層11それぞれのチャネル領域の両側面にゲート絶縁膜12を介して形成されたゲート電極13と、第1の半導体層11のソース/ドレイン領域と第2の半導体層11のソース/ドレイン領域との間の溝を埋め込むように形成された絶縁膜19と、第1の半導体層11のソース/ドレイン領域及び第2の半導体層11のソース/ドレイン領域の絶縁膜19で覆われていない側面にそれぞれ形成されたシリサイド16とを備える。

(もっと読む)

蓄積型FINFET、回路、及びその製造方法

【課題】FinFET、集積回路、およびFinFETの形成方法を提供する。

【解決手段】基板120、前記基板上にあり、ソース106とドレイン110との間のチャネル108を含み、前記ソース106、前記ドレイン110、および前記チャネル108は、第1型ドーパントを有し、前記チャネル108は、ゲルマニウム、シリコンゲルマニウム、またはIII−V族半導体の少なくとも1つを含むフィン構造、前記チャネル108上のゲート誘電体層114、および前記ゲート誘電体層114上のゲート116を含むFinFET。

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート型FIN−FETにおいて、微細化に対してもFIN型トランジスタの利点を十分に発揮し、また、活性領域において十分なコンタクト面積を確保し、オン電流の低下を抑制したトレンチゲート型FIN−FETを提供する。

【解決手段】チャネル領域のFIN幅(162)を活性領域の幅(161)よりも狭くする。

(もっと読む)

フィンタイプデバイスシステム及び方法

フィンタイプデバイスシステム及び方法が開示される。特定の実施形態において、表面を有する基板内にトランジスタのゲートを形成する段階と、前記基板内に、第1BOX層面において前記ゲートに隣接する埋込酸化物(BOX)層を形成する段階と、を含むトランジスタの製造方法が開示される。本方法はまた、レイズドソース−ドレインチャネル(フィン)を形成する段階であって、前記フィンの少なくとも一部が前記基板の表面から延長し、前記フィンが、前記BOX層の第2BOX層面に隣接する第1フィン面を有する段階を含む。  (もっと読む)

(もっと読む)

高ゲルマニウム濃度のSiGeストレッサの形成方法

【課題】SiGeストレッサの形成方法と集積回路のトランジスタ構造を提供する。

【解決手段】SiGeストレッサを形成する方法であって、前記方法は、ソース領域とドレイン領域間にチャネルを有する半導体基板上のソース領域とドレイン領域の少なくとも1つに第1SiGe層を堆積するステップ、及び前記第1SiGe層の上部を酸化層に変換し、前記第1SiGe層の底部を第2SiGe層に変換するステップを含み、前記第2SiGe層は、前記第1SiGe層より高いGe濃度を有する方法。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】 極浅拡散層を形成することが可能な半導体装置の製造方法及び半導体製造装置

を提供することを目的とする。

【解決手段】

半導体基板100表面をアモルファス化することにより半導体基板100表面にアモル

ファス層111を形成するアモルファス層形成工程と、ドーパントを含むガス雰囲気中で

半導体基板100にマイクロ波を照射することにより、アモルファス層111にドーパン

トを拡散させるとともにドーパントの活性化を行い、半導体基板100に拡散層112を

形成する拡散層形成工程と、を具備する。

(もっと読む)

高移動度マルチゲートトランジスタのフィン構造

【課題】 半導体トランジスタの垂直フィン構造及びその製造方法を提供する。

【解決手段】 半導体トランジスタの垂直フィン構造であって、半導体基板、この半導体基板の上部のフィン層、及びこのフィン層を覆うキャッピング層を含み、半導体基板は、IV族半導体材料を含み、フィン層は、IV族半導体材料を含み、キャッピング層は、III−V族半導体化合物を含み、フィン層は、半導体トランジスタのチャネルとなり、キャッピング層は、フィン層に歪みを加え、チャネルを通過する移動度を向上させる垂直フィン構造。

(もっと読む)

半導体装置

【課題】ゲート・オール・アラウンドトランジスタの複数のチャネルそれぞれに流れる電流を均一にし、ゲート・オール・アラウンドトランジスタの信頼性を向上させる。

【解決手段】半導体基板と、半導体基板上に一定の間隔をおいて形成された第1の半導体層上に第2の半導体層を形成した積層構造が複数積み重なったソース・ドレイン領域と、第2の半導体層の同一レイヤ間をそれぞれ接続するようにワイア状に形成された複数のチャネル領域と、前記複数のチャネル領域をそれぞれ包み込むようにゲート絶縁膜を介して形成されたゲート電極とを具備し、チャネル領域のチャネル幅は、半導体基板から離れるほど狭く形成され、第2の半導体層及びチャネル領域の膜厚は、半導体基板から離れるほど広く形成される。

(もっと読む)

101 - 120 / 437

[ Back to top ]