Fターム[5F140BB05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSHC(垂直表面水平電流) (437)

Fターム[5F140BB05]に分類される特許

81 - 100 / 437

マルチゲートIII−V量子井戸構造

マイクロ電子構造を形成する方法を記載する。方法の実施形態は、基板上にIII−Vトライゲートフィンを形成する段階と、III−Vトライゲートフィンの周囲にクラッド材を形成する段階と、クラッド材の周りに高誘電率ゲート誘電体を形成する段階とを備える。 (もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置

【課題】 占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を得ることを目的とする。

【解決手段】 絶縁膜が埋め込まれたトレンチ素子分離領域と、凹部に周囲をゲート絶縁膜で覆われたゲート電極が埋め込まれたトレンチチャネル領域と、絶縁膜が埋め込まれた凹部の周囲を濃いN型の拡散層で覆ったトレンチドレイン領域とが形成されており、ESD保護用のN型MOSトランジスタのチャネル領域には、トレンチチャネル領域が形成され、なおかつESD保護用のN型MOSトランジスタのドレイン領域には、トレンチドレイン領域が形成されている。

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

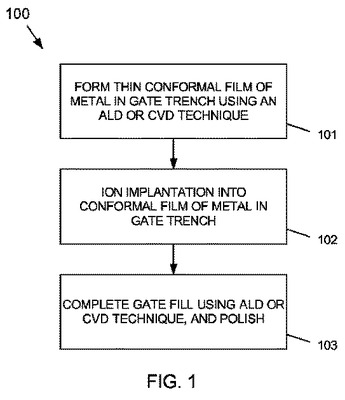

イオン注入を用いた圧縮金属ゲート応力の導入によるトライゲートMOSFETの駆動電流の増大化

半導体デバイスは、フィン及び金属ゲート膜を有する。フィンは半導体材料の表面に形成されている。金属ゲート膜は、フィン上に形成され、且つ金属ゲート内に圧縮応力を形成するために当該金属ゲート膜内に注入されたイオンを有する。典型的な一実施形態において、半導体材料の表面は(100)結晶格子方向を有し、フィンの方向は、半導体材料の結晶格子に関して<100>方向に沿っている。典型的な他の一実施形態において、半導体材料の表面は(100)結晶格子方向を有し、フィンの方向は、半導体材料の結晶格子に関して<110>方向に沿っている。フィンは、金属ゲート膜内の圧縮応力によって生成される面外圧縮を有する。  (もっと読む)

(もっと読む)

非平面ゲルマニウム量子井戸デバイス

非平面(ノンプレーナ)ゲルマニウム量子井戸構造を形成する技術が開示される。量子井戸構造は、IV族又はIII−V族の半導体材料を用いて実現されることができ、ゲルマニウムフィン構造を含む。一例において、非平面量子井戸デバイスが提供され、このデバイスは、基板(例えば、シリコン上にSiGe又はGaAsのバッファを有する)と、IV族又はIII−V族材料のバリア層(例えば、SiGe、GaAs又はAlGaAs)と、ドーピング層(例えば、デルタ/変調ドープされる)と、アンドープのゲルマニウム量子井戸層とを有する量子井戸構造を含む。アンドープのゲルマニウムフィン構造が量子井戸構造内に形成され、該フィン構造上に頂部バリア層が堆積される。ゲートメタルが、フィン構造を横切って堆積される。ドレイン/ソース領域がフィン構造のそれぞれのエンドに形成され得る。  (もっと読む)

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

半導体装置、および、その製造方法

【課題】半導体素子の特性を向上させると共に、半導体素子の微細化を容易に実現する。

【解決手段】半導体素子101にてゲート電極111gが設けられる部分の表面を凹凸面に形成する。ここでは、凹凸面のうち凸部CVでは、一対のソース・ドレイン領域112s,112dの表面と同一の面を覆うようにゲート絶縁膜111zを形成し、そのゲート絶縁膜111zの上面にゲート電極111gを設ける。これに対して、凹部TRでは、一対のソース・ドレイン領域112s,112dの表面から内部へ向けて設けられた溝Mの面を覆うようにゲート絶縁膜111zを形成し、その溝Mの内部を埋め込むようにゲート電極111gを設ける。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明はビット配線と半導体基板上の不純物拡散層とのコンタクト抵抗を低減した構造の提供を目的とする。

【解決手段】本発明は、半導体基板の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にビット配線が形成されるとともに、前記不純物拡散層に接続されたビット配線の少なくとも底部側が、不純物をドープした不純物ドープ型のポリシリコンに更に不純物イオンを打ち込みしてなる注入ポリシリコン膜からなることを特徴とする。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

半導体装置の製造方法

【課題】 これまでのイオン注入処理に比べて、高い時間効率で高濃度のキャリア不純物原子を、通常のイオン注入の処理時間で低エネルギードーピングできる方法を提供する。

【解決手段】 半導体基板としてのシリコン基板11の表面上に加工により突出部を形成した該シリコン基板の内部においてドナーもしくはアクセプターとなる不純物原子を含む不純物薄膜を、堆積膜13としてシリコン基板の表面上に堆積する工程と、前記突出部における前記堆積膜の斜め上方からイオン注入を行なうとともに、該イオン注入によって、前記不純物原子を堆積膜内部からシリコン基板の前記突出部の表面内部にリコイルさせる工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSトランジスタのオン電流を低下させずにMOSトランジスタを小型化する。

【解決手段】素子形成領域2を他の領域と分離する素子分離領域3が形成された基板(半導体基板1)と、素子形成領域2に形成されたゲート溝4と、素子形成領域2にゲート溝4を挟んで離間して形成された一対の拡散領域5を有する。更に、ゲート溝4内及びゲート溝4の周囲縁部に形成されたゲート6を有する。ゲート溝4は、チャネル幅方向Dではその開口端4aの形状が素子分離領域3により画定され、且つ、チャネル長方向Eでは一対の拡散領域5にそれぞれ接するように形成されている。チャネル幅方向Dにおいて、ゲート溝4と素子分離領域3との間に、一対の拡散領域5を繋ぐ半導体領域(シリコン領域20)を有している。

(もっと読む)

トレンチ型パワーMOSトランジスタおよびその製造方法

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

不均一な半導体装置のアクティブ領域パターン形成方法

【課題】不均一な半導体装置のアクティブ領域パターン形成方法を提供する。

【解決手段】具体例によると、少なくとも3つのアクティブ領域を含む半導体装置が提供される。少なくとも3つのアクティブ領域は隣接する。少なくとも3つのアクティブ領域の縦軸は平行で、少なくとも3つのアクティブ領域は、それぞれ、対応するアクティブ領域の縦軸と交差する辺縁を有する。少なくとも3つのアクティブ領域の辺縁は弧形を形成する。

(もっと読む)

半導体素子及びトランジスタ

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができる半導体素子及びトランジスタを提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができる半導体素子及びトランジスタを提供すること、を目的とする。

【解決手段】半導体基板上に形成されて第1半導体パターンを含む3次元直線状の第1構造物と、第一構造物の中心部を貫通するように配置され、第1半導体パターンと異なる結晶構造を有する第2半導体パターンを含む第2構造物と、第1構造物に対して直交する方向に延長して3面で第2構造物の一部を囲むゲートを含むトランジスタとする。

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細化が進んだトランジスタにおいて、他の問題を生じさせずに抵抗を低減する。

【解決手段】シリサイド層9は、ソース・ドレイン領域8の表層及びソース・ドレイン拡張領域6に形成されている。シリサイド層9は、半導体基板1に垂直かつゲート幅方向に対して平行な断面でみたときに、ソース・ドレイン領域8の中央部からチャネル領域に近づくにつれて半導体基板1の内側(図中下側)に近づいており、かつチャネル領域側の端部がソース・ドレイン拡張領域6に延在している。

(もっと読む)

トランジスタの製造方法

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができるトランジスタの製造方法を提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができるトランジスタの製造方法を提供すること、を目的とする。

【解決手段】半導体基板上に第1半導体層及び第1半導体層と異なる格子定数と結晶構造を有する第2半導体層を順次形成する段階と、第2半導体層及び第1半導体層をエッチングして格子定数の差によって第1半導体層の結晶構造が変形された変形結晶構造を有し、直線状の第1半導体パターンを形成する段階と、第1半導体パターン上に第1半導体層と同一な結晶構造を有する第3半導体層を形成する段階とを含む。

(もっと読む)

81 - 100 / 437

[ Back to top ]