Fターム[5F140BB05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSHC(垂直表面水平電流) (437)

Fターム[5F140BB05]に分類される特許

61 - 80 / 437

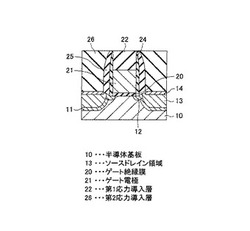

半導体装置及びその製造方法

【課題】チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させる半導体装置を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

(もっと読む)

双方向スイッチ及びその製造方法

【課題】トレンチゲート構造で共用ドレインを有する2つのMOS型トランジスタから構成される双方向スイッチのオン抵抗の低減を図る。

【解決手段】N型ウエル層2に複数のトレンチ3を形成する。次に前記複数のトレンチ3に挟まれたN型ウエル層2に1列おきにP型ボディ層6を形成する。複数のP型ボディ層6にはN+型第1ソース層7とN+型第2ソース層9を交互に形成する。N+型第1ソース層7を挟む1対のトレンチ3のそれぞれに第1ゲート電極5a、N+型第2ソース層9を挟む1対のトレンチ3のそれぞれに第2ゲート電極5bを形成する。第1ゲート電極5aが形成されたトレンチ3のP型ボディ層6側と反対側の側壁と第2ゲート電極5bが形成された同様の側壁に挟まれたN型ウエル層2を電界緩和層としてのN型ドレイン層11aとする。該N型ドレイン層11aを双方向スイッチのオン電流の流れる電流経路とする。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、基板102の素子形成領域に形成されたトレンチ162、トレンチ162の側壁および底面に形成されたゲート絶縁膜120、トレンチ162を埋め込むようにゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112、およびゲート長方向の他方の側に形成されたドレイン領域113、を有するトランジスタを含む。ここで、ゲート電極122は、トレンチ162外部の基板102上にも露出して形成され、ゲート電極122は、ゲート長方向における、トレンチ162の両端部上部が覆われるとともに、中央部に少なくとも一つ深さが基板まで達する凹部が形成されるように設けられている。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、ゲート幅方向に断続的に深さが変化する複数のトレンチ162、各複数のトレンチ162の側壁および底面に形成されたゲート絶縁膜120、ゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112およびゲート長方向の他方の側に形成されたドレイン領域113を有するトランジスタを含む。ここで、トレンチ162の側壁の基板102の表面から底面に向かう途中の位置から底面までの下部分におけるゲート絶縁膜120の膜厚が、当該側壁の途中の位置から表面までの上部分におけるゲート絶縁膜120の膜厚よりも厚く、かつ底面におけるゲート絶縁膜120の膜厚以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】チャネル領域を従来よりも拡大することが可能な半導体装置を提供する。

【解決手段】埋め込みゲート用の溝部9,10のうち、活性領域6に形成される第1の溝部9よりも素子分離領域5に形成される第2の溝部10の深さを深くすることによって、第2の溝部10の底面の間から活性領域6の一部が突き出した第1のフィン部12aと、埋め込みゲート用の溝部9,10の少なくとも上面開口部よりも下部側において、第1の溝部9よりも第2の溝部10の第1の方向における幅を大きくすることによって、第2の溝部10の両側面の間から第1のフィン部12aに連続して活性領域6の一部が突き出した一対の第2のフィン部と12bとを形成する。

(もっと読む)

半導体装置

【課題】最小加工寸法がフィン幅となるFinFETの構造において、極めて制御が困難なリング形状の加工を不要として、加工ばらつきに起因する特性ばらつきの小さなユニットセルを提供する。

【解決手段】ユニットセルは、半導体基板1上に形成された開ループ構造のゲート電極Gと、前記ゲート電極Gの内方となる領域にフィン状に形成されたドレイン領域2と、前記ゲート電極Gの外方となる領域に形成されたフィン状のソース領域3とを有する。前記ドレイン領域2の上にはドレインコンタクト2aが形成され、前記ソース領域3上にはソースコンタクト3aが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】例えばフィン型の半導体装置とその製造方法を提供すること。

【解決手段】半導体基板102上に第1の層108と、この第1の層上に形成された第の2層110と、この第2の層上に形成された第3の層112とを含む多層構造104を形成し、前記半導体基板と前記多層構造との上部を除去することにより、前記半導体基板上に複数のフィン202とこのフィン上に前記多層構造204の一部を形成し、前記フィンの間206に、上面が多層構造の上面と一致する分離材料300を形成し、前記第2の層を露出するよう前記第3の層と前記分離材料の上部とをエッチングし、前記第1の層が露出するように前記第2の層と残存する前記分離材料の上部の一部とをエッチングする。

(もっと読む)

半導体装置及びその製作方法

【課題】半導体記憶装置に適するトランジスタ構造及びその製作方法の提供。

【解決手段】デュアルチャネルトランジスタ50は、少なくとも、第一方向に沿って伸展する第一STI(シャロートレンチアイソレーション)と第二方向に沿って伸展する第二STIにより分離され、第一STIと第二STIが交差する半導体アイランド22と、第二方向に沿って伸展し、半導体アイランドの表面から内側に向かって凹んだゲートトレンチ26と、第二方向に沿って伸展し、ゲートトレンチ内に設けられたゲート30と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第一ソース/ドレイン領域と、第一ソース/ドレイン領域の間に設けられた第一U字型チャネル領域60と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第二ソース/ドレイン領域と、第二ソース/ドレイン領域の間に設けられた第二U字型チャネル領域62とを備える。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ構造を有するMOSトランジスタにおいて、チャネル領域のしきい値の適切な調整が可能となる半導体装置を提供する。

【解決手段】第1導電型半導体基板に作られたゲート幅方向に深さが変化する凹部領域と凸部領域の前記凹部領域はトレンチ構造で形成されているトレンチ構造を有するMOSトランジスタにおいて、前記第1導電型半導体基板表面に沿って成膜した犠牲酸化膜を介して形成された第1導電型ドープドポリシリコン膜を前記凹部領域のトレンチ構造に埋め込ませて熱処理をおこなうことで、前記トレンチ構造間の凸部領域上面およびトレンチ構造の凹部領域側面と底面に不純物拡散する。これにより、トレンチピッチが縮小されてもチャネルへの均一な不純物添加が可能になる。

(もっと読む)

プラズマ処理方法

【課題】3次元トランジスタ構造のPolyシリコンゲート側壁の窒素含有シリコン膜をシリコン基板削れを抑制しつつ、所望の形状に加工する方法を提供する。

【解決手段】3次元トランジスタ構造上の窒素含有シリコン膜をプラズマエッチングするために、堆積性の高いガスでエッチングする第1ステップと、堆積成分を除去する第2ステップとを有し、前記第1ステップと前記第2ステップを交互に繰り返すことにより、Polyシリコンゲート電極31の側壁にのみ窒素含有シリコン膜34を残し、かつ、シリコン基板33の削れを抑制するようにエッチング加工する。

(もっと読む)

半導体装置の製造方法

【課題】FIN状の半導体部により構成されるFIN型トランジスタを有する半導体装置において、FIN状の半導体部の上面の不純物濃度と側面の不純物濃度との差を小さくすることにより、FIN型トランジスタの特性ばらつきを抑えて、信頼性を向上させる。

【解決手段】

FIN状の半導体部10の上面に2〜5nm程度の厚さのパッド絶縁膜3を形成し、FIN状の半導体部10の一方の側面に、第1注入角度θ1を有する斜め方向からクラスタイオンを注入した後、FIN状の半導体部10の他方の側面に、第1注入角度θ1と対称の第2注入角度θ2を有する斜め方向からクラスタイオンを注入する。その後、FIN状の半導体部10に注入されたクラスタイオンを活性化して、ソース領域およびドレイン領域の一部を構成する拡散領域を形成する。

(もっと読む)

半導体記憶装置

【課題】活性領域の接触面積を増大でき、コンタクト抵抗を低減可能な半導体記憶装置を提供する。

【解決手段】フィン状の活性領域13は、半導体基板11内に設けられ、第1の側面、前記第1の側面に平行する第2の側面、及び前記第1、第2の側面を繋ぐ上面を有する。ワード線の一部としてのゲート電極14は、活性領域に形成された溝17内及び溝を跨いで形成され、活性領域と絶縁されている。シリサイド層16は、ゲート電極の両側の活性領域に位置し、ソース、ドレイン領域としての活性領域の少なくとも第1の側面に形成されている。少なくとも記憶素子21を接続するためのコンタクト15は、シリサイド層に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの閾値電圧のバックゲート電圧依存性を低減することができる。

【解決手段】半導体装置100は、基板(例えば、P型半導体基板3)と、基板に形成され素子形成領域1を他の領域と分離する素子分離領域2と、を有している。更に、素子形成領域1上に形成されたゲート電極4を有し、ゲート電極4は、素子分離領域2において素子形成領域1を介して互いに対向する第1及び第2領域2a、2bの上にそれぞれ延伸している。更に、ゲート電極4を基準としてチャネル長方向Dに相互に離間するように素子形成領域1に形成された一対の拡散領域(例えば、N型拡散領域5)を有する。第1領域2a及び第2領域2bの上面の少なくとも一部分ずつは、素子形成領域1の上面よりも下に、チャネル幅Wの5%以上の深さに凹んでおり、それら凹み7内にもゲート電極4の一部分ずつが存在している。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】側面に(110)面が形成されたGe若しくはSiGeのフィン構造を実現することができ、FinFET等の素子特性の向上に寄与する。

【解決手段】Ge若しくはSiGeのフィン構造部を有する半導体装置であって、Si基板10の表面部に、一方向に長いストライプ領域を挟むように埋め込み形成され且つ基板表面よりも高い位置まで形成された素子分離絶縁膜12と、ストライプ領域上に形成され、且つ最上面が前記素子分離絶縁膜の最上面よりも低い位置にあるSiGeバッファ層14と、バッファ層14上に形成され、該層14よりも一方向と直交する方向の幅が狭く基板面と垂直な(110)面を有するGeフィン構造16と、を備えた。

(もっと読む)

61 - 80 / 437

[ Back to top ]