Fターム[5F140BB05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSHC(垂直表面水平電流) (437)

Fターム[5F140BB05]に分類される特許

161 - 180 / 437

半導体装置の製造方法

【課題】Si系基板上に結晶性の良いSi系結晶またはGe系結晶をエピタキシャル成長させることのできる半導体装置の製造方法を提供する。

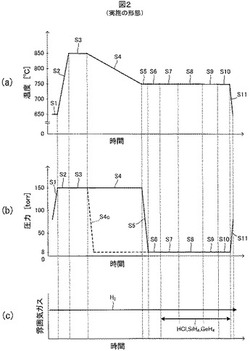

【解決手段】本発明の一態様に係る半導体装置の製造方法は、水素ガス雰囲気中において、圧力が第1の圧力であり、温度が第1の温度である条件下で、シリコン窒化物からなる部材を備えたSi系基板の前記部材に覆われていない領域の自然酸化膜および付着したシリコン窒化物を除去する工程と、水素ガス雰囲気中において、圧力を前記第1の圧力に保持したまま、温度を前記第1の温度から第2の温度に下げる工程と、水素ガス雰囲気中において、温度を前記第2の温度に保持したまま、圧力を前記第1の圧力から第2の圧力に下げる工程と、圧力を前記第2の圧力に下げた後、水素ガス、およびSiおよびGeのうちの少なくともいずれか1つを含む前駆体ガス雰囲気中において、前記Si系基板の表面にSiおよびGeのうちの少なくともいずれか1つを含む結晶をエピタキシャル成長させる工程と、を含む。

(もっと読む)

半導体装置

【課題】 従来の比例縮小側(係数α、α>1)を適用した平面型MOSTのしきい電圧のばらつきの標準偏差σ(VT)が、微細化とともに、すなわちαを大きくするとともに大きくなり、動作電圧が低くできないという問題がある。

【解決手段】 フィンの高さをチャンネル長よりも高くしたFinFET構造によって上記の問題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

電子回路および電子回路の製造方法

【課題】ESDダメージが低いESDパワーレベルで発生するFinFET集積回路において、ESDから回路デバイスを保護することができる電子回路を提供する。

【解決手段】電子回路400’は、静電放電現象から保護される少なくとも1つの電界効果トランジスタと、少なくとも1つの保護される電界効果トランジスタ400aとを含む。保護電界効果トランジスタ400bは、保護される電界効果トランジスタ400aの結晶方位とは異なった結晶方位を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、良好な移動度を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 第一の発明の半導体装置は、基板と、基板表面に形成され、Geを主成分とする半導体領域と、半導体領域上に形成された非金属Ge化合物層と、非金属Ge化合物層上に形成された絶縁膜と、絶縁膜上に形成された電極と、前記電極を挟む前記基板表面に形成されたソース・ドレイン領域とを備えることを特徴とする。非金属Ge化合物層は、例えばSrとGeの化合物、BaとGeの化合物もしくはBaとSiとGeの化合物を有する。

(もっと読む)

半導体装置の製造方法

【課題】活性領域表面に凹凸を生じることなく活性領域上端の角部を丸めることができる半導体装置の製造方法を提供する。

【解決手段】活性領域を画定する素子分離絶縁膜を形成する工程と、活性領域上に、0.1nm以上、0.7nm未満の膜厚の自然酸化膜を形成する工程と、水素を含む雰囲気中で、850℃よりも高く950℃未満の温度で熱処理を行い、活性領域の角部を丸めるとともに、自然酸化膜を還元除去する工程と、自然酸化膜を除去した活性領域上に、ゲート絶縁膜を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属微粒子と半導体基板の反応を利用して電極を形成する、高性能な半導体装置の製造方法およびグレイン粒径の小さい電極を有する高性能な半導体装置を提供する。

【解決手段】直径20nm以下の金属微粒子を溶媒中に分散した溶液を、半導体基板上に塗布する工程と、溶媒を蒸発させる工程と、金属微粒子と半導体基板を反応させ、半導体基板表面に金属半導体化合物薄膜を形成する工程とを有することを特徴とする半導体装置の製造方法。半導体基板上に金属半導体化合物薄膜を有する半導体装置であって、金属半導体化合物薄膜は膜厚方向に単グレインで形成され、単グレインの粒径が40nm以下であることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の周囲、全周にわたってチャネル領域を形成することで、単位面積当たりの電流量を増加させることを可能にする。

【解決手段】半導体領域11と、前記半導体領域11中に配置されたゲート電極21と、前記ゲート電極21の周囲に形成されたゲート絶縁膜22と、前記ゲート電極21の一端に前記ゲート絶縁膜22を介して形成されたソース・ドレイン電極になる第1不純物領域23と、前記ゲート電極21を横切るように前記半導体領域11に前記ゲート絶縁膜22を介して形成されたソース・ドレイン電極になる第2不純物領域24と、前記ゲート電極21の他端に接続されたゲート引き出し電極25を有し、前記第1不純物領域23と前記第2不純物領域24との間の前記ゲート電極21周囲の前記半導体領域11にチャネル領域が形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】閾値電圧が制御されて、且つ特性のばらつきが抑制された半導体装置を提供する。

【解決手段】基板2と、STI素子分離領域3と、活性領域4と、活性領域4に形成された第1ゲートトレンチ5と、第1ゲートトレンチ5の底部に設けられた第2ゲートトレンチ6と、第1及び第2ゲートトレンチ5,6にゲート絶縁膜7を介して埋め込み形成されたゲート電極8と、第1ゲートトレンチ5の幅方向両側の活性領域4にイオンを注入することによって形成されたソース/ドレイン領域9とを備え、第2ゲートトレンチ6と第2ゲートトレンチ6の長手方向に位置するSTI素子分離領域3との間に、チャネルを構成するシリコン薄膜部10が設けられていることを特徴とする半導体装置1。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

半導体装置の製造方法

【課題】Bulk Fin構造の製造に於いて、ハードマスクの側面の後退・破損を発生させること無く、パッド酸化膜のサイドエッチ量を最小限度にとどめて、ゲート加工等の後工程を行うに際して良好な形状を有するFin構造を実現する。

【解決手段】シリコン基板1上に、所定の間隔SDを隔てて配列し且つ各々が所定の方向へ延在すると共に、所定の高さDを有する複数のシリコン柱体1Fを形成する。その際に、各シリコン柱体1Fの上面には、パッド酸化膜2及びハードマスク3が順次に形成される。その後、酸素ガス、アルゴンガス、水素ガス及びシリコンガスをベースとなる反応ガスとして用いるPVD法によって、隣り合うシリコン柱体1Fによって形成されるリセス1Rを完全に充填すると共に、リセス1Rの上方及びハードマスク3の上方にまで至る埋め込み酸化膜5を堆積する。この堆積時に、幅Wのハードマスク3の側面は削除されない。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化しても動作特性の劣化が生じないSTI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのゲート電極部をNMOS仕事関数制御メタル層7及びゲート主電極5により構成する。NMOS仕事関数制御メタル層7をスパッタ法により形成され、ディボット部2dが設けられるエッジ近傍領域である領域bにおける膜厚は、他の領域である領域aにおける膜厚より薄く形成される。したがって、NMOS仕事関数制御メタル層7に関し、領域bにおける実効仕事関数が領域aにおける実効仕事関数に比べ、ミッドギャップよりに設定される。

(もっと読む)

トレンチ分離を備えたフィン型半導体デバイスを形成する方法

【解決手段】

フィンFETデバイス構造のような半導体デバイス構造(300)を製造する方法が提供される。方法は、バルク半導体材質(302)、バルク半導体材質(302)から形成される第1の伝導性フィン構造(306)、及びバルク半導体材質(302)から形成される第2の伝導性フィン構造(308)を備えている基板を提供することとによって開始する。第1の伝導性フィン構造(306)と第2の伝導性フィン構造(308)はギャップ(322)によって分離される。次いでギャップ(322)内であって且つ第1の伝導性フィン構造(306)及び第2の伝導性フィン構造(308)に隣接してスペーサ(332,334)が形成される。その後、エッチングステップが、スペーサ(332,334)をエッチングマスクとして用いてバルク半導体材質(302)をエッチングしてバルク半導体材質(302)内に分離トレンチ(336)を形成する。スペーサ(332,334)を覆い、第1の伝導性フィン構造(306)を覆い、且つ第2の伝導性フィン構造(308)を覆うように分離トレンチ(336)内に誘電体材質(340)が形成される。その後、分離トレンチ(336)内の誘電体材質(340)を保ちながら誘電体材質(340)の少なくとも一部分及びスペーサ(332,334)の少なくとも一部分がエッチングされて、第1の伝導性フィン構造の上部(342)及び第2の伝導性フィン構造(308)の上部(342)が露出させられる。これらのステップの後に、デバイスの製造は標準的な方法において完了する。

(もっと読む)

半導体装置及びその製造方法、並びに、データ処理システム

【課題】異なる特性を有するリセスチャネル型のトランジスタを同一工程で同時に形成する。

【解決手段】ハードマスク71〜73を用いて半導体基板2をエッチングし、ハードマスク71〜73の側面にサイドウォール絶縁膜38を形成し、ハードマスク71,72の側面に形成されたサイドウォール絶縁膜38を選択的に除去し、ハードマスク71〜73とサイドウォール絶縁膜38を用いて半導体基板2をさらにエッチングし、ハードマスク71〜73に覆われていた半導体基板2の一部にそれぞれゲートトレンチ12,22,32を同時に形成する工程と、ゲートトレンチ12,22,32の内部にゲート電極13,23,33を形成する工程と備える。これにより、フィン状領域21f,31fの高さが異なる複数のリセスチャネル型トランジスタを同時に形成することができる。

(もっと読む)

バルク基板上に形成されたダブルゲート及びトライゲートトランジスタ及びそのトランジスタを形成するための方法

【解決手段】

FinFETS及びトライゲートトランジスタのような三次元トランジスタ構造が、強化されたマスキング形態によって形成することができ、それによりバルク半導体材質内での自己整合手法によるドレイン及びソース区域(211D,211S)、フィン(210)並びに分離構造(208A)の形成が可能になる。基本フィン構造(210)を画定した後、プレーナトランジスタ構造の高度に効率的な製造技術を用いることができ、それにより三次元トランジスタ構造の総合的な性能を更に高めることができる。

(もっと読む)

プラズマドーピング方法及びプラズマドーピング装置

【課題】処理基板面内にイオンをより均等に注入することができるプラズマドーピング方法及びプラズマドーピング装置を提供する。

【解決手段】プラズマドーピング処理中に、ウェハ9を載置する電極6を電気的に複数の電極部18,19に分割し、少なくとも2つ以上の高周波電力を電極部にそれぞれ印加することによって、ウェハ表面に生成される電位に面内で分布をつくり、電気力線を曲げ、不純物元素を含むイオンを立体形状の側面にドーピングする。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、MOSFETのチャネル領域に生じる歪み量を増加させ、歪みに基づく素子性能を向上させることを目的とする。

【解決手段】 本発明に係る半導体装置は、半導体基板1と、半導体基板1の上面に、第1の方向に延びて設けられた第1の絶縁膜2aと、第1の方向と垂直な第2の方向から第1の絶縁膜2aを挟んで設けられ、第1の絶縁膜2aに第2の方向の応力を与え、第1の方向の歪みを誘起させる第1の歪み誘起層3と、第1の絶縁膜2a上に設けられ、第1の絶縁膜2aからの応力を受けて第1の方向の歪みを有するチャネル領域4を含む第1の半導体層5aと、第1の方向からチャネル領域を挟んで設けられたソース領域9及びドレイン領域10と、第1の半導体層5aの第2の方向に対向する側面及び上面に設けられたゲート絶縁膜6と、ゲート絶縁膜6を介してチャネル領域4と対向して設けられたゲート電極7とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】Nチャネル絶縁ゲート型電界効果トランジスタのシリコンのチャネル領域に引張応力を効果的に印加することを可能とし、また寄生トランジスタの移動度を高めることを可能にする。

【解決手段】シリコン基板11と、前記シリコン基板11に区画された素子形成部12と、前記素子形成部12に形成されたNチャネル絶縁ゲート型電界効果トランジスタ20と、前記シリコン基板11に形成されていて前記素子形成部12の側部を囲む溝部13と、前記溝部13内に絶縁材料が埋め込まれて形成された素子分離部14と、少なくとも前記Nチャネル絶縁ゲート型電界効果トランジスタ20のチャネル長L方向と平行な前記溝部13の側面に形成されたシリコンゲルマニウムエピタキシャル成長層15を有する。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域のゲート幅方向に与える応力を移動度が向上する方向に働かすとともに、ソース・ドレイン領域表面にシリサイド層を形成した際のリークを防止する。

【解決手段】半導体基板11に素子形成領域12を挟み、半導体基板11に埋め込まれるように素子分離領域13を形成する工程と、素子形成領域12上にそれを横切るようにダミーゲート52を形成する工程と、ダミーゲート52の両側の素子形成領域12にソース・ドレイン領域の接合位置が素子分離領域13の表面より深い位置にしてソース・ドレイン領域27、28を形成する工程と、半導体基板11上にダミーゲート52の表面を露出させて第1層間絶縁膜42を形成する工程と、ダミーゲート52を除去して溝29を形成する工程と、溝29内の素子分離領域13の上部を除去する工程と、溝29内の半導体基板11上にゲート絶縁膜21を介してゲート電極22を形成する工程とを備えている。

(もっと読む)

161 - 180 / 437

[ Back to top ]