Fターム[5F140BB05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSHC(垂直表面水平電流) (437)

Fターム[5F140BB05]に分類される特許

121 - 140 / 437

半導体装置

【課題】ゲート・オール・アラウンドトランジスタの複数のチャネルそれぞれに流れる電流を均一にし、ゲート・オール・アラウンドトランジスタの信頼性を向上させる。

【解決手段】半導体基板と、半導体基板上に一定の間隔をおいて形成された第1の半導体層上に第2の半導体層を形成した積層構造が複数積み重なったソース・ドレイン領域と、第2の半導体層の同一レイヤ間をそれぞれ接続するようにワイア状に形成された複数のチャネル領域と、前記複数のチャネル領域をそれぞれ包み込むようにゲート絶縁膜を介して形成されたゲート電極とを具備し、チャネル領域のチャネル幅は、半導体基板から離れるほど狭く形成され、第2の半導体層及びチャネル領域の膜厚は、半導体基板から離れるほど広く形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域を拡大し、駆動電流の増大を図ることを可能とした半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2に埋め込まれた埋込み絶縁膜3により絶縁分離された活性領域5と、活性領域5上に形成されたゲート絶縁膜6を介して当該活性領域5を跨ぐように形成されたゲート電極7と、ゲート電極7を挟んだ両側の活性領域5にイオン注入することによって形成されたソース領域8及びドレイン領域9とを備え、活性領域5に溝部10が設けられて、この溝部10の内側にゲート絶縁膜6を介してゲート電極7の一部が埋め込まれてなるトレンチ型のチャネル構造を有し、活性領域5の両側面に凹部11が対向して設けられて、これら凹部11の間に幅狭部12が形成されることによって、少なくとも溝部10の底面と幅狭部12との間に当該幅狭部12よりも幅広となるチャネル領域13が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートコンタクトプラグとシリコン基板とのショートを防ぐ。

【解決手段】半導体装置10は、半導体基板11と、半導体基板11の主面に対して垂直な側面を有するシリコンピラー14Bと、シリコンピラー14Bの側面を覆うゲート絶縁膜15Bと、半導体基板11の主面に対して垂直な内周側面16a及び外周側面16bを有し、ゲート絶縁膜15Bを介して内周側面16aとシリコンピラー14Bの側面とが対向するよう、シリコンピラー14Bの側面を覆うゲート電極16と、ゲート電極16の外周側面16bの少なくとも一部を覆うゲート電極保護膜17と、ゲート電極16及びゲート電極保護膜17の上方に設けられた層間絶縁膜30と、層間絶縁膜30に設けられたコンタクトホールに埋め込まれ、ゲート電極16及びゲート電極保護膜17に接するゲートコンタクトプラグGCとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域における電界の部分的な集中を防止する。

【解決手段】半導体装置は、分離絶縁領域(6)に囲まれた活性領域に形成された第1の拡散領域と第2の拡散領域と、第1の拡散領域と第2の拡散領域との間に形成された溝状のトレンチ領域と、トレンチ領域上に形成されたゲート絶縁膜(10)と、トレンチ領域を埋め込むようにゲート絶縁膜上に形成されたゲート電極(11)と、ゲート絶縁膜と分離絶縁領域とで挟まれた領域のうち上層側に位置する領域に形成された保護絶縁膜(4)と、を備える。

(もっと読む)

半導体装置

【課題】 従来の比例縮小側(係数α、α>1)を適用した平面型MOSTのしきい電圧のばらつきの標準偏差σ(VT)が、微細化とともに、すなわちαを大きくするとともに大きくなり、動作電圧が低くできないという問題がある。

【解決手段】 フィンの高さをチャンネル長よりも高くしたFinFET構造によって上記の問題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチゲート構造を有するトランジスタにおいて、サブスレッショルド特性を良好にする。

【解決手段】半導体装置100は、第1導電型のソース領域112およびドレイン領域113、これらの間に第2導電型のチャネル領域108が形成された基板102と、チャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162を埋め込むように形成されたゲート電極122とを有するトランジスタを含む。チャネル領域108において、基板102表面およびトレンチ162の底部には、それぞれ第2の高濃度領域132および第1の高濃度領域130が形成されており、第2導電型の不純物濃度がトレンチ162側方における第2導電型の不純物濃度よりも高くなっている。また、第1の高濃度領域130の第2導電型の不純物濃度が第2の高濃度領域132の第2導電型の不純物濃度以上である。

(もっと読む)

シャロートレンチアイソレーションプロセス

【課題】トレンチ構造の歪み導入要素によりに歪み導入されたチャネルを持つMOSトランジスタのリーク電流を改善する。

【解決手段】MOSトランジスタ106のチャネル領域108に、第1トレンチ構造55a、第2トレンチ構造55bによる歪み導入要素だけでなく、別の歪み導入要素として、MOSトランジスタ106表面上にコンフォーマルに設けられた窒化シリコンキャップ層130を設ける。別の態様では、チャネル領域108内の歪みは、ガス種、例えば水素、酸素、ヘリウムまたは別の希ガスをゲート110またはチャネル領域108の下の領域内に注入することによって導入される。

(もっと読む)

半導体装置及びその製造方法

【課題】フィントランジスタの素子分離膜中にボイドが発生しにくい構造の半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1の基準面103及び第1の基準面103よりも高い位置に設けられた第2の基準面104を有するシリコン基板100を備えている。シリコン基板100の上には、互いに間隔をおいて、上面が第2の基準面103よりも高い位置にあり、フィントランジスタを構成するフィン121及びフィン122が形成されている。第1の基準面103の上には、上面がフィン121及びフィン122の上面よりも低い位置にある第1の素子分離膜131Aが形成されている。第1の基準面103を挟んで隣接する2つのフィン121の間隔は、第2の基準面104を挟んで隣接する2つのフィン122の間隔よりも広い。

(もっと読む)

置換ゲート構造体を有するFET及びその製造方法

【課題】 マルチゲート型FETの置換ゲート構造体及びマルチゲート型FETの置換ゲート構造体の製造方法を提供する。

【解決手段】 MUGFET及びMUGFETを製造する方法が示される。MUGFETを製造する方法は、複数の活性領域の周りに一時的スペーサ・ゲート(図3の16)を形成することと、複数の活性領域の間を含む、一時的スペーサ・ゲートの上に誘電体材料(18a及び空間20内)を堆積させることとを含む。この方法は、誘電体材料(空間20内)の部分をエッチングして一時的スペーサ・ゲート(16)を露出させることと、一時的スペーサ・ゲートを除去して、活性領域と誘電体材料の残りの部分(18a)との間に空間を残すこととをさらに含む。この方法はさらに、活性領域と誘電体材料の残りの部分(18a)との間の空間(22)及び誘電体材料の残りの部分の上方をゲート材料で充填することを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

傾斜三元または四元マルチゲートトランジスタ

【課題】 フィン電界効果トランジスタ(FinFET)とその形成方法を提供する。

【解決手段】 半導体基板、前記半導体基板上の絶縁領域、及び前記半導体基板上に位置し、前記絶縁領域間の間隙に少なくとも一部を有し、第1III-V族化合物半導体材料を含むエピタキシー領域を含み、前記エピタキシー領域は、そこと前記半導体基板が第1格子不整合を有する下部分、及び前記下部分上に位置し、そこと前記半導体基板が前記第1格子不整合と異なる第2格子不整合を有する上部分を更に含む集積回路構造。

(もっと読む)

モデルパラメータ決定装置、モデルパラメータ決定方法及びプログラム

【課題】半導体集積回路を製造するプロセスを変更した場合において、デバイスモデルによって変更後のプロセスにより製造された半導体素子を表すためにデバイスモデルに含まれるモデルパラメータを容易に決定できるようにする。

【解決手段】モデルパラメータ決定装置は、第1の製法により製造された半導体素子を特徴付ける第1の物理パラメータ群と、半導体素子の特性を表すためのデバイスモデルに含まれるモデルパラメータ群であって第1の製法により製造された半導体素子を表すための第1のモデルパラメータ群と、第2の製法により製造された半導体素子を特徴付ける第2の物理パラメータ群とを入力し、第2の製法により製造された半導体素子の特性を当該デバイスモデルによって表すためのモデルパラメータ群を、第1の物理パラメータ群及び第1のモデルパラメータ群並びに第2の物理パラメータ群に基づいて決定する。

(もっと読む)

改善されたオン/オフ電流比の高移動度多重ゲートトランジスタ

【課題】 金属酸化物半導体(MOS)トランジスタとその形成方法を提供する。

【解決手段】 多重ゲートトランジスタは、基板、第1半導体材料で形成された中央フィン、及び中央フィンの対向側壁上の第1部分と第2部分を含み、第1半導体材料とは異なる第2半導体材料を包含する半導体層を含む基板上の半導体フィン、この半導体フィンの側壁の周囲を包むゲート電極、及び半導体フィンの対向端のソース領域とドレイン領域を含み、中央フィンと半導体層の各々は、ソース領域からドレイン領域に延伸する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置全体としてみたとき、微細化によるチップ面積の減少を図りつつ、各素子に必要とされる特性を維持・向上させる。

【解決手段】半導体装置は、FinFET10と、FinFET10と同一のチップ上に設けられたPlanarFET20とを具備する。PlanarFETの第2ゲート絶縁層24は、FinFET10の第1ゲート絶縁層14よりも厚い。

(もっと読む)

非平面な基板表面を有する基板を処理する方法

非平面的な表面を有する基板を共形的に処理する技術を開示する。この技術は、複数の段階を備える。第1段階では、基板の幾つかの面が効果的に処理される。第2段階では、これらの面が更に処理されるのを防ぐ又は制限するべく処理が行われる。第3段階では、基板のその他の面が処理される。ある適用例では、第1段階及び第2段階において、粒子の流れに垂直又は実質的に垂直な面が処理され、その他の面は、第3段階において処理される。ある実施形態では、第2段階は、基板への膜の堆積工程を含む。 (もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

半導体素子及び半導体装置

【課題】高い電流駆動力を有するn型半導体素子を提供する。

【解決手段】第1の主面を有し、III族の不純物を含み、1.2<N<10を満たすNを用いて(11N)面と表される、ないしはそれと結晶学的に等価な第1の面方位のみを前記第1の主面に有する、シリコンとゲルマニウムとの混晶層と、前記第1の主面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記混晶層の[110]方向ないしそれと結晶学的に等価な方向に、前記ゲート電極を挟む様に形成され、V族の不純物を含む半導体よりなるソース・ドレイン領域と、を有し、前記混晶層は面内方向に圧縮歪みが印加されていることを特徴とする。

(もっと読む)

半導体装置

【課題】電気的性質が良好なhigh−k膜/Geゲートスタック構造を有する半導体装置を提供する。

【解決手段】Geを主成分とする半導体領域(10)と、前記半導体領域上に形成された絶縁膜(11)と、前記絶縁膜上に形成された金属膜(12)とを具備する半導体装置である。前記絶縁膜は、少なくとも1種の希土類元素(MR)と、TiおよびZrから選択される少なくとも1種のIV族元素(MIV)と、酸素とを含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

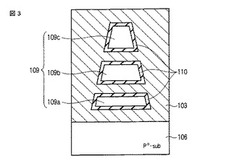

【課題】フィン型電界効果トランジスタの寄生抵抗を低減し、駆動電流を増大させる。

【解決手段】半導体基板本体部101と、半導体基板本体部101の上に突成された、フィン108と、を有し、フィン108は、両端側の一対のソース/ドレイン領域106および一対のソース/ドレイン領域106に挟まれたチャネル領域107を有するものとして構成された、半導体基板と、

半導体基板本体部101の上に形成された、シリコン酸化物からなる、素子分離絶縁膜102と、

素子分離絶縁膜102の上に形成された、シリコン窒化物又はシリコン炭窒化物からなる、被膜109と、

チャネル領域107におけるフィン108の上に形成されたゲート絶縁膜と、

ゲート絶縁膜を介してフィン108におけるチャネル領域107を挟むように形成された、ゲート電極103と、

ソース/ドレイン領域106を覆うと共に被膜109と隙間なく当接する、応力印加層105と、を備える。

(もっと読む)

121 - 140 / 437

[ Back to top ]