Fターム[5F140BD10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | SiN+SiO(多層の場合) (76)

Fターム[5F140BD10]に分類される特許

1 - 20 / 76

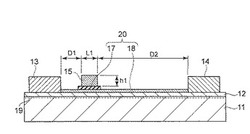

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】界面準位密度およびフラットバンド電圧がともに良好な界面特性を有する半導体装置の製造方法を提供すること。

【解決手段】まず、炭化珪素基板1の表面を洗浄する(ステップS1)。つぎに、原料ガスをECRプラズマ化し、原料ガスに含まれる原子を炭化珪素基板1に照射することで、炭化珪素基板1の表面にシリコン窒化膜2を成長させる(ステップS2)。つぎに、ECRプラズマ化学気相成長法により、シリコン窒化膜2の表面にシリコン酸化膜3を堆積する(ステップS3)。つぎに、窒素雰囲気中で、シリコン窒化膜2およびシリコン酸化膜3が形成された炭化珪素基板1のアニール処理を行う(ステップS4)。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極用溝18の底部に設けられた第1の不純物拡散領域27と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第2の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように半導体基板13に設けられ、第1の不純物拡散領域27と接合された第3の不純物拡散領域29と、を有する。

(もっと読む)

ISFETおよびISFETアレイ

【課題】センサ感度を向上したISFETおよびこのISFETセルを適用したISFETアレイを提供する。

【解決手段】第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域12と、ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20と、ゲート絶縁膜18に接触する液体試料26と、液体試料26中に配置された参照電極24とを備えるISFET2およびこのISFETセルを適用したISFETアレイ4。

(もっと読む)

半導体装置および半導体装置の製造方法

【目的】水素終端よりも強い界面終端構造を有する半導体装置を提供することを目的の1つとする。

【構成】実施形態の半導体装置は、絶縁膜とSi半導体部とを備えている。絶縁膜は、酸化物と窒化物と酸窒化物とのいずれかを用いて形成される。Si半導体部202は、前記絶縁膜下に配置され、硫黄(S)とセレン(Se)とテルル(Te)とのうち少なくとも1種の元素が前記絶縁膜との界面に存在する、シリコン(Si)を用いて形成される。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜-半導体構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図り、界面準位密度の低い良好なゲート酸化膜/半導体界面が形成された半導体装置、およびそれを形成する重水素処理装置およびその作製方法を提供する。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置。

(もっと読む)

コンデンサ及びその製造方法

【課題】金属−絶縁体−金属コンデンサや、内部接続構造の金属間誘電体として使用して、その素子や構造の平均故障寿命を改善できる誘電体構造を提供すること。

【解決手段】酸化膜層、誘電体材料層及び誘電体材料層の上に第2酸化膜層を有する、炭化ケイ素用のコンデンサ及び内部接続構造が提供される。酸化膜層の厚みは、酸化膜層と誘電体材料層の約0.5から約33パーセントであってよい。誘電体構造として酸窒化ケイ素層を有する炭化ケイ素用のコンデンサおよび内部接続構造もまた提供される。こうしたコンデンサ及び構造を作製する方法もまた提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】Y方向に延在するように半導体基板13に設けられ、底面18c及び対向する第1及び第2の側面18a,18bを有するゲート電極用溝18と、ゲート絶縁膜21を介して、ゲート電極用溝18の下部を埋め込むように配置されたゲート電極22と、ゲート電極用溝18を埋め込むように配置され、ゲート電極22の上面22aを覆う埋め込み絶縁膜24と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第1の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように、半導体基板13に設けられた第2の不純物拡散領域29と、を有する。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】界面準位密度のゲート酸化膜/半導体界面が形成された半導体装置、および作製方法の提供。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置とする。シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜(あるいは酸化膜)-半導体(MISあるいはMOS)構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図る。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極と半導体基板との間のショートの発生を抑制した上で、厚さが厚く、かつ均一な厚さとされたシリサイド層を形成可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜27を介して、ピラー26の側面26a,26bに設けられたゲート電極61,62と、ピラー26の上端26−1に形成されたシリサイド層38と、ゲート電極61,62を覆うと共に、ピラー26の側面を囲むように配置され、かつシリサイド層38の側面を露出する絶縁膜と、シリサイド層38の側面を覆うように設けられ、かつピラー26の上端26−1に含まれるシリコンをシリサイド化させる金属膜39と、シリサイド層38の下面38bと接触するように、ピラー26に形成された上部不純物拡散領域36と、シリサイド層38の上面38aに設けられたキャパシタ52と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置

【課題】本発明は、不純物拡散層と半導体基板との間に形成される空乏層中におけるGIDLを抑制することのできる半導体装置を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成された第2の溝32と、少なくとも第2の溝32の側面32aを覆うゲート絶縁膜38と、ゲート絶縁膜38を介して、第2の溝32の側面32aに形成され、その上端面45aが半導体基板11の表面11aより低い位置にあってゲート電極39となる第1の導電膜45と、第1の導電膜45に形成され、その上端面46aが第1の導電膜45の上端面45bよりも高く、かつ半導体基板11の表面11aより低い位置にあってゲート電極39となる第2の導電膜46と、第1の導電膜45の上端面45b、及び第1の導電膜45の上端面45bから突出した第2の導電膜46を覆うように、第2の溝32内に設けられた第2の絶縁膜と、を有する。

(もっと読む)

電荷トラップを有するゲート誘電体を含む揮発性メモリ及びその製造方法

【課題】チャネルイオン注入領域のドーピング濃度を相対的に低下しながらも所望のしきい電圧値を得ることができる揮発性メモリを提供する。

【解決手段】ゲート誘電体として順次積層された下部ゲート誘電体、電荷トラップのための中間ゲート誘電体、及び上部ゲート誘電体を備えたセルトランジスタと、ゲート誘電体として単一層の酸化膜を備えたロジック用トランジスタとで、揮発性メモリを構成する。

(もっと読む)

半導体素子の製造方法

【課題】ピッティング不良が抑制され、簡単な工程を通じて形成することができる高性能の半導体素子の製造方法を提供する。

【解決手段】半導体基板にゲート電極を形成する段階と、ゲート電極に側壁スペーサを形成する段階と、側壁スペーサの両側の半導体基板を一部エッチングしてトレンチを形成する段階と、トレンチ内にSiGe混晶層を形成する段階と、SiGe混晶層上にシリコン層を形成する段階と、シリコン層の面の結晶方向に従って、エッチング率が異なるエッチング液を利用してシリコン層の一部をエッチチングすることによって111傾斜面を有するシリコンファセット(Si facet)を含むキャッピング層を形成する段階と、を有する。キャッピング層を含むことによって半導体素子でホールの移動度が高まる。キャッピング層内のピッティング不良が減少することによって半導体素子の特性が良好になる。

(もっと読む)

半導体装置

【課題】 占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を得ることを目的とする。

【解決手段】 絶縁膜が埋め込まれたトレンチ素子分離領域と、凹部に周囲をゲート絶縁膜で覆われたゲート電極が埋め込まれたトレンチチャネル領域と、絶縁膜が埋め込まれた凹部の周囲を濃いN型の拡散層で覆ったトレンチドレイン領域とが形成されており、ESD保護用のN型MOSトランジスタのチャネル領域には、トレンチチャネル領域が形成され、なおかつESD保護用のN型MOSトランジスタのドレイン領域には、トレンチドレイン領域が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層上に第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタは、基板1、チャネル層3及びバリア層4と、バリア層4上にこの順で離間して設けられたソース電極6、ゲート電極7およびドレイン電極8とを備え、ソース電極6の直下に第1のn型不純物拡散領域12が設けられ、ドレイン電極8の直下に第2のn型不純物拡散領域13が設けられ、第2のn型不純物拡散領域の下側の前記チャネル層3および第2のn型不純物拡散領域の前記ゲート電極側の前記チャネル層3および前記バリア層4に第3のn型不純物拡散領域15が設けられる。第3のn型不純物拡散領域15は第2のn型不純物拡散領域13よりも低いn型不純物濃度を有し、ゲート電極とドレイン電極との間に電圧が印加されたときバリア層4およびチャネル層3においてその絶縁破壊強度を超える電界集中が生じることを抑制する。

(もっと読む)

1 - 20 / 76

[ Back to top ]