Fターム[5F140BE09]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成するための処理 (4,399) | 堆積 (1,850)

Fターム[5F140BE09]の下位に属するFターム

CVD (1,050)

Fターム[5F140BE09]に分類される特許

41 - 60 / 800

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】finFETにおける高集積化可能な、高濃度ソースドレインの形成方法の提供。

【解決手段】ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを形成する。チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有するゲートスタックを形成する。チャネル領域を残したまま、ソース領域およびドレイン領域をエッチング除去する。ソース領域およびドレイン領域に隣接したチャネル領域の両側にソースエピタキシー領域およびドレインエピタキシー領域を形成する。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を成長させながら、その場ドープされる。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

コーナートランジスターとその製作方法

【課題】改善された性能を有し、かつ縮小されたサイズを有することのできるコーナートランジスターを提供する。また、コーナートランジスターを製作する方法を提供し、それがトランジスターの性能を改善するとともに、簡単なプロセスを介して、そのサイズを縮小することができる。

【解決手段】この発明のコーナートランジスターを製作する方法を以下に記述する。分離構造(isolation structure)が基板中に形成されて能動エリア(active area)を定義する。処理プロセスが実施されて、能動エリア中の基板がそのトップエッジに鋭いコーナーを有するようにする。能動エリア中の基板がゲート誘電層により被覆される。ゲート導体がゲート誘電層上に形成される。ソース領域およびドレイン領域がゲート導体両側の基板中に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ダミーゲート電極の除去により形成されたゲート溝へのゲート電極材料の埋め込み性を改善することにより、適切な閾値電圧を持つ電界効果型トランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】ゲート電極111bは、それぞれ金属又は導電性金属化合物からなる第1導電膜108b、第2導電膜109b及び第3導電膜110bが下から順に形成された積層構造を有し、ゲート電極111aは、第2導電膜109a及び第3導電膜110aが下から順に形成された積層構造を有する。第1導電膜108bの仕事関数と第2導電膜109a、109bの仕事関数とは異なっている。第1導電膜108bは板状に形成されており、第2導電膜109a、109bは凹形状に形成されている。

(もっと読む)

炭化珪素半導体を用いたMOS構造およびその酸化膜形成方法

【課題】 SiO2/SiC界面における界面準位自体を低減することが出来るSiC半導体を用いたMOS構造、およびその酸化膜の形成方法を提供する。

【解決手段】 SiC半導体基板1を処理炉内に用意し、処理炉内を比較的低い700℃に設定して、SiC半導体基板1の基板表面を酸素ガス雰囲気中にさらす。この熱酸化により、SiC半導体基板1の基板表面には、SiO2から成る中間層2が約1nmの極薄い厚さで形成される。次に、中間層2上にSiO2膜を約50nmの厚さに堆積して、SiO2から成る堆積層3を形成する。次に、SiC半導体基板1が酸化しない温度および時間で、堆積層3をアニーリングする。このアニーリングは、赤外線ランプなどの急速加熱装置により、SiO2膜の融点である1200℃に近い、この1200℃の融点よりも低い例えば1000〜1100℃程度の温度で、短時間に急速に行われる。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体装置の、ソース・ドレイン間のオン抵抗を低減する。

【解決手段】ソース・ドレイン間を走行する窒化物半導体層と下地となる窒化物半導体層の間に、両窒化物半導体層より電子親和力が大きく、下地となる窒化物半導体よりも格子定数の大きい材料を形成する。その結果、ゲート電圧の印加によりゲート絶縁膜の下方に形成されるチャネルと、ゲート部以外で形成される二次元電子ガスを、深さ方向において近づけることができ、オン抵抗の低減が可能となる。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】高性能なIII−V族MISFETの実現を可能にする、より効果的なIII−V族化合物半導体表面のパッシベーション技術を提供する。

【解決手段】エピタキシャル成長により化合物半導体層をベース基板上に形成するステップと、前記化合物半導体層の表面をセレン化合物を含む洗浄液で洗浄するステップと、前記化合物半導体層の上に絶縁層を形成するステップと、を有する半導体基板の製造方法を提供する。前記セレン化合物として、セレン酸化物が挙げられる。前記セレン酸化物として、H2SeO3が挙げられる。前記洗浄液が、水、アンモニアおよびエタノールからなる群から選択された1以上の物質をさらに含んでもよい。前記化合物半導体層の表面がInxGa1−xAs(0≦x≦1)からなる場合、前記絶縁層がAl2O3からなるものであることが好ましく、Al2O3は、ALD法により形成されることが好ましい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

半導体装置及び半導体装置の製造方法

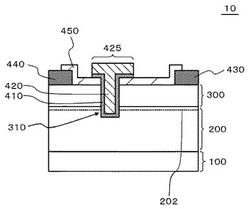

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】界面準位密度およびフラットバンド電圧がともに良好な界面特性を有する半導体装置の製造方法を提供すること。

【解決手段】まず、炭化珪素基板1の表面を洗浄する(ステップS1)。つぎに、原料ガスをECRプラズマ化し、原料ガスに含まれる原子を炭化珪素基板1に照射することで、炭化珪素基板1の表面にシリコン窒化膜2を成長させる(ステップS2)。つぎに、ECRプラズマ化学気相成長法により、シリコン窒化膜2の表面にシリコン酸化膜3を堆積する(ステップS3)。つぎに、窒素雰囲気中で、シリコン窒化膜2およびシリコン酸化膜3が形成された炭化珪素基板1のアニール処理を行う(ステップS4)。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

半導体装置の製造方法

【課題】高い誘電率でリーク電流の低い誘電体膜を有する高集積化可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記熱処理後の誘電体膜にイオン化したガスクラスターを照射する照射工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

電界効果型トランジスタ

【課題】実用上十分なプロセスマージンを備える状態で、リーク電流の増大およびキャリア濃度の低下を招くことなく、ゲート電極とチャネル層との距離が短縮できるようにする。

【解決手段】InPからなる基板101の上に形成された電子供給層102と、電子供給層102の上に形成されたスペーサ層103と、スペーサ層103の上に形成されたチャネル層104と、チャネル層104の上に形成された障壁層105とを備え、障壁層105は、GaおよびAlの少なくとも1つと、Inと、Pとを含んだアンドープの化合物半導体から構成し、InPよりショットキー障壁高さが高いものとされている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

高誘電性ナノシート積層体、高誘電性ナノシート積層体、高誘電体素子、および高誘電体薄膜素子の製造方法

【課題】コンデンサなどに好適な、非常に薄くしても高い誘電率と良好な絶縁特性を同時に実現する高誘電体薄膜を提供する。

【解決手段】上記課題は、ペロブスカイト構造を有する酸化物ナノシートなどの高誘電体により構成される薄膜により達成される。

(もっと読む)

41 - 60 / 800

[ Back to top ]