Fターム[5F140BE09]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成するための処理 (4,399) | 堆積 (1,850)

Fターム[5F140BE09]の下位に属するFターム

CVD (1,050)

Fターム[5F140BE09]に分類される特許

781 - 800 / 800

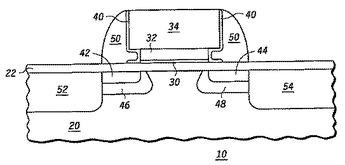

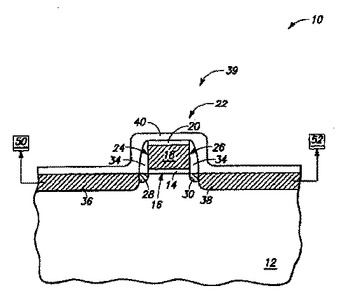

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

III族窒化膜双方向スイッチ

【課題】電力用デバイスにおいて双方向に電圧をブロックできるようにする。

【解決手段】大電流を搬送するチャンネルを得るAlGaN/GaNインターフェースを備えたIII族窒化物双方向スイッチであり、この双方向スイッチは、この双方向スイッチのために、電流を搬送するチャンネルを形成するための二次元電子ガスの発生を阻止したり、または可能にする少なくとも1つのゲートにより作動する。

(もっと読む)

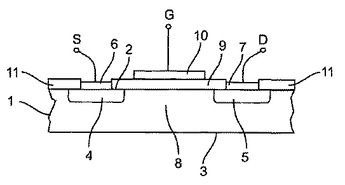

トンネル層に量子ドットを有するトランジスタ

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

酸化ハフニウム層および酸窒化ハフニウム層または酸化ジルコニウム層および酸窒化ジルコニウム層のための前駆体としての溶解ハフニウムアルコキシドまたはジルコニウムアルコキシドの使用

本発明は、酸化ハフニウム層および酸窒化ハフニウム層用の前駆体としての高濃度の少なくとも1種のハフニウムアルコキシド溶液の使用に関するものである。本発明は特には、CVD法またはALD法用の酸化ハフニウム層および酸窒化ハフニウム層を製造するための濃度30〜90重量%の少なくとも1種のハフニウムアルコキシドの溶液の使用に関するものである。さらに本発明は、コーティング対象物上での酸化ハフニウム層および酸窒化ハフニウム層の製造方法、ならびに30〜90重量%の少なくとも1種のハフニウムアルコキシドを含むハフニウムアルコキシド溶液に関するものである。本発明の別の実施形態では、前記化合物において、ハフニウムをジルコニウムに置き換える。 (もっと読む)

ドープされたゲート誘電体を有するトランジスタ

トランジスタおよびその製造方法。ゲート誘電体材料を堆積する前に半導体基材をドープする。別個のアニール工程、または、トランジスタを製造するために使用される後続のアニール工程の間を用いて、ドーパント種を、基材のドープされた領域から、ゲート誘電体内に出力拡散して、ドープされたゲート誘電体を生成する。ドーパント種は、ゲート誘電体の原子構造における各空孔を埋め、その結果、トランジスタの動作速度が上昇し、電力消費が低減され、電圧安定性が改善される。  (もっと読む)

(もっと読む)

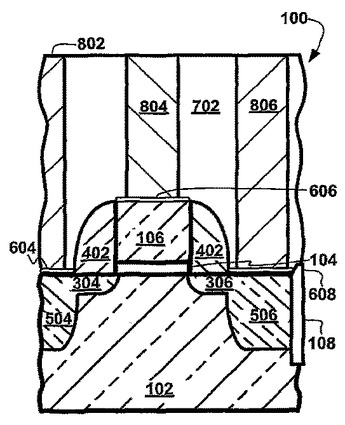

集積回路技術における低応力の側壁スペーサ

半導体基板(102)に集積回路の形成方法(900)を提供する。半導体基板(102)上にゲート絶縁膜(104)が形成され、このゲート絶縁膜(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(304)(306)が形成される。低出力プラズマ化学気相成長法プロセスを使用して、ゲート(106)の周りに側壁スペーサ(402)を形成する。ソース/ドレイン接合部(304)(306)およびゲート(106)に、シリサイド(604)(606)(608)を形成し、半導体基板(102)上に層間絶縁層(702)をたい積する。その後、層間絶縁層(702)中にシリサイド(604)(606)(608)へのコンタクト(802)(804)(806)が形成される。  (もっと読む)

(もっと読む)

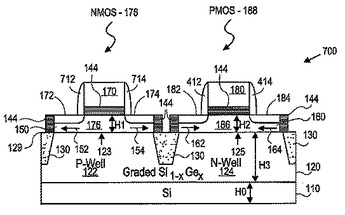

CMOS用歪トランジスタの集積化

【解決手段】CMOSデバイスに関連する本発明の様々な実施形態は、(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

(もっと読む)

乱数生成素子

【課題】 増幅回路を用いなくても1Mbit/s以上の乱数生成レートが可能となるような物理現象中のランダムノイズを利用した乱数生成素子を提供することを目的とする。

【解決手段】 半導体表面との間で非常に薄いトンネル絶縁膜を介して電子の充放電が可能な導電性微粒子をチャネル上に設け、チャネル幅Wを狭く、かつ導電性微粒子の面密度Ddotを多く、かつチャネル〜導電性微粒子間のトンネル抵抗を小さくする。例えば、膜厚0.8nmのシリコン窒化膜をトンネル絶縁膜とするバルク基盤上の素子の場合、チャネル幅W=0.1μm、平均粒径d=8nm程度のSi微結晶粒子群を1.7×1012cm−2程度の面密度で形成すると、1MHzのノイズ成分を0.1%にできる。

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

高誘電率誘電体膜の窒化方法

本発明は、低温プロセスを用いてhigh−k誘電体膜内に窒素の取り込み(例えば窒化物形成)を促進する。更に、本発明は、原位置法、すなわちhigh−k誘電体膜の形成及び膜の窒化物形成が従来の後処理技術とは対照的に膜の堆積中に同じプロセスチャンバ内で実施される方法を提供する。別の態様では、半導体デバイス内のゲート誘電体層として用いるための多層材料の堆積方法が提供される。 (もっと読む)

半導体装置の製造方法

シリコン基板(101)上に、RTO法によりシリコン酸化物からなる下地層(103)を形成する。このとき、下地層(103)の膜厚を1.5nm以上とする。次に、下地層(103)上に、CVD法によりハフニウム窒化物を0.5乃至1.0nmの厚さに堆積させ、金属化合物層(104)とする。次に、水素雰囲気中において熱処理を施し、金属化合物層(104)から下地層(103)中にハフニウム元素を拡散させてシリケート化させ、ゲート絶縁膜(106)を形成する。その後、酸化雰囲気中において熱処理を行う。このとき、シリコン基板(101)とゲート絶縁膜(106)との界面には、ハフニウム元素が到達しないようにする。  (もっと読む)

(もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

ハフニウムベースの高誘電率誘電体の原子層堆積

ハフニウムベースの誘電体膜を堆積する方法が提供される。本方法は、オゾンとハフニウム前駆体を含む1つ又はそれ以上の反応物質とを用いた原子層堆積段階を含む。半導体デバイスもまた提供される。該デバイスは、基板と、基板上に形成されたハフニウムベースの誘電体層と、基板及びハフニウムベースの誘電体層間に形成された界面層とを含み、該界面層は二酸化ケイ素を含み且つ結晶構造を有する。 (もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

絶縁膜形成方法

半導体基板上に形成する絶縁膜を高性能化して、リーク電流の少ない電子デバイスを製造する方法を提供する。高誘電材料金属のみを半導体基板上に金属膜として形成し、その金属膜を250〜450℃に加熱し、その加熱した金属膜に、クリプトンガス(またはキセノンガス)を酸素ガスと混合させ、その混合ガスをプラズマ化したガスを加えることにより、金属膜を酸化して、半導体基板上に絶縁膜を形成するようにしたことを特徴とする。 (もっと読む)

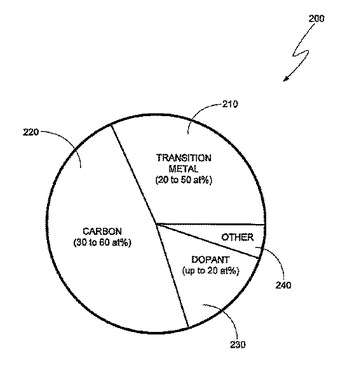

ゲート電極として使用される遷移金属合金およびこれらの合金を取り入れた装置

高温で顕著に変化しないn型またはp型の仕事関数を有する遷移金属合金の実施例を示した。示された遷移金属合金は、トランジスタのゲート電極として使用しても良く、ゲート電極の一部を構成しても良い。これらの遷移金属合金を用いて、ゲート電極を形成する方法についても示した。  (もっと読む)

(もっと読む)

電気試験データに基づいてゲート絶縁層の特性および特徴を制御するための方法、これを実施するためのシステム

本発明は、一般に、電気試験データ(46)に基づいてゲート絶縁層(16)の特性および特徴を制御する各種方法、ならびにこれを実施するためのシステムを対象としている。例示的な一実施形態では、上記方法は、少なくとも1つの半導体デバイスに少なくとも1つの電気試験を実施するステップと、以降形成する半導体デバイスに少なくとも1つのゲート絶縁層(16)を形成するために実施する少なくとも1つのプロセス操作の少なくとも1つのパラメータを、電気試験から得られた電気データに基づいて決定するステップと、決定されたパラメータを含む少なくとも1つのプロセス操作を実施して、ゲート絶縁層(16)を形成するステップとを有する。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

SiC基板1と、SiC基板1表面に形成されたソース3a及びドレイン3bと、SiC表面に接して形成され厚さが1分子層以上のAlN層5と、その上に形成されたSiO2層とを有する絶縁構造と、この絶縁構造上に形成されたゲート電極15とを有しており、SiCとの間の界面状態を良好に保ちつつ、リーク電流を抑制することができる。 (もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

多成分誘電体膜を形成するためのシステム及び方法

【課題】半導体用途における誘電体膜を形成するためのシステム及び方法、特に、混合気化前駆体を用いて基板上に多成分誘電体膜を作製するためのシステム及び方法を提供する。

【解決手段】本発明は、気化した前駆体の混合物が、原子層堆積(ALD)処理における単一パルス段階中にチャンバ内に一緒に存在して多成分膜を形成するような気化前駆体の混合をもたらすためのシステム及び方法を提供する。気化前駆体は、少なくとも1つの異なる化学成分から成り、そのような異なる成分が単層を形成して多成分膜を生成することになる。本発明の更に別の態様では、組成勾配を有する誘電体膜が提供される。

(もっと読む)

781 - 800 / 800

[ Back to top ]