Fターム[5F140BF32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 構造、不純物の状態 (690) | 材料の不均一性 (81)

Fターム[5F140BF32]に分類される特許

61 - 80 / 81

半導体装置

【課題】ゲート電極の空乏化を抑制しながら、電子移動度の劣化を低減することが可能な半導体装置を提供する。

【解決手段】この半導体装置では、nチャネルMOSトランジスタ50aのゲート電極8aは、ゲート絶縁膜7aを部分的に覆うようにドット状に形成された金属含有層9aと、金属含有層9a上に形成され、ゲート絶縁膜7aの金属含有層9aにより覆われていない部分に接触する下部ポリシリコン層10aとを含み、pチャネルMOSトランジスタ50bのゲート電極8bは、ゲート絶縁膜27aを部分的に覆うように形成された金属含有層29aと、金属含有層29a上に形成され、ゲート絶縁膜27aの金属含有層29aにより覆われていない部分に接触する下部ポリシリコン層30aとを含み、ゲート電極8aおよびゲート電極8bは、互いに異なる金属(HfおよびPt)を含む。

(もっと読む)

リセスチャネル構造を有するセルトランジスタを含む半導体装置およびその製造方法

【課題】動作電圧の変動が少なく、正常に動作する半導体装置を提供すること。

【解決手段】表面チャネル型nMOSFET構造を備えたトランジスタ構造および表面チ

ャネル型pMOSFET構造を有備えたトランジスタ構造を有するデュアルゲート型周辺

トランジスタと、リセスチャネル構造を備えたnMOSFET構造を有するセルトランジ

スタと、を含む半導体装置であって、前記セルトランジスタ中のゲート電極を構成するN

型ポリシリコン層に含まれるN型不純物の濃度が、略一定である半導体装置。

(もっと読む)

二重の完全ケイ化ゲートを形成する方法と前記方法によって得られたデバイス

【課題】各トランジスタタイプの金属ゲート電極の仕事関数を、簡単で能率的に設計でき、トランジスタ又は使われたゲート絶縁体のジオメトリ及び/または大きさとは関係なくコントロール可能な二重の金属ゲートCMOSデバイスを製造する複雑でない製造方法を提供する。

【解決手段】 二重の完全ケイ化ゲートデバイスを製造する方法は、異なる厚さを有する半導体ゲート電極をそれぞれが有する少なくとも2つのMOSFETデバイスを提供するステップと、前記半導体ゲート電極の各々の上に一定の厚さの金属層を積層するステップと、熱処理を遂行するステップとを含み、前記半導体ゲート電極を完全にケイ化するように、各々の半導体厚さを選択し、それによって前記少なくとも2つのMOSFETは異なる仕事関数を有する。

(もっと読む)

多重仕事関数金属窒化物ゲート電極を有するMOSトランジスタ、これを採用するCMOS集積回路素子及びその製造方法

【課題】多重仕事関数金属窒化物ゲート電極を有するMOSトランジスタが提供される。

【解決手段】MOSトランジスタは半導体基板及び前記半導体基板上に配置された中心ゲート電極を具備する。前記中心ゲート電極は金属窒化物からなる。前記中心ゲート電極の両側壁上にそれぞれソース側ゲート電極及びドレイン側ゲート電極が提供される。前記ソース/ドレイン側ゲート電極は窒素よりも小さい電気陰性度を有する第1不純物または窒素よりも大きい電気陰性度を有する第2不純物を含むドープ金属窒化物からなる。前記MOSトランジスタを採用するCMOS集積回路素子及びその製造方法も提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の少なくともゲート絶縁膜側をハフニウムと窒素とを含む膜で形成し、そのハフニウムと窒素とを含む膜中の窒素を適性な組成比にすることで、従来から用いられているPoly−Si電極とほぼ同レベルの良好な移動度を得ることを実現する。

【解決手段】半導体基板11上にゲート絶縁膜14を介してゲート電極15を備えた電界効果トランジスタからなる半導体装置1であって、前記ゲート電極15は少なくとも前記ゲート絶縁膜14側がハフニウムと窒素とを含む膜からなり、前記ハフニウムと窒素とを含む膜は少なくとも窒素を含みかつハフニウムと窒素とに対する窒素の組成比が51%以下である。

(もっと読む)

半導体装置の製造方法

【課題】シリコン酸化膜中に導入する窒素の窒素濃度及び偏析位置を制御する工程を有する半導体装置の製造方法を提供する。

【解決手段】半導体装置18の製造方法は、基板10上にシリコン酸化膜12を形成するシリコン酸化膜形成工程1と、シリコン酸化膜12上にシリコン膜14を形成する工程(シリコン膜形成工程2)と、シリコン膜12が最表面に形成された基板10に対して熱窒化処理を行うことにより、シリコン酸化膜12中に窒素を導入する工程(熱窒化処理工程3)とを有する。

(もっと読む)

多層ゲート構造を備える半導体素子及びそれの製造方法

【課題】半導体基板と半導体基板上に形成されたドープされた導電膜を含む半導体素子を提供する。

【解決手段】拡散バリヤ膜がドープされた導電膜上に形成される。拡散バリヤ膜は、非晶質半導体物質を含む。オーミックコンタクト膜が拡散バリヤ膜上に形成される。金属バリヤ膜がオーミックコンタクト膜上に形成される。金属膜が金属バリヤ膜上に形成される。これにより、界面抵抗を所望の範囲内に維持できながら、オーミックコンタクト膜下部の導電体にドープされた不純物が外部に拡散することを効果的に防止できて、多層構造を採用した半導体素子の反転キャパシタンス特性などを向上させることができる。

(もっと読む)

半導体デバイスのための改善されたゲート電極

本発明は、ゲート絶縁膜上に形成されると共にゲート物質から形成されるゲート電極及び半導体基板を有するMIS型半導体デバイスを提供する。ゲート電極は、基板に向かう方向に向けられる第一の側部及び前記基板から離れる方向に向けられる第二の測部を有し、前記活性化された結晶ゲート物質の第一の層は、1019イオン/cm3又はそれより高いドーピングレベルを有する活性化された結晶ゲート物質の第一の層と、前記活性化された結晶ゲート物質の第一の層の前記第二の側部におけるゲート物質の第二の層とを有する。本発明は、このようなデバイスを製造する方法も提供する。  (もっと読む)

(もっと読む)

エピタキシャルシリコンウエハとその製造方法および半導体装置とその製造方法

【課題】シリコンウエハにおいて金属汚染に強いエピタキシャルシリコンウエハの製造方法を得ること。

【解決手段】シリコンウエハ上にシリコンのエピタキシャル層を成長させるエピタキシャル層成長工程と、シリコンウエハに対して600〜900℃で1時間以上の熱処理を行う低温熱処理工程と、シリコンウエハに対して1000〜1050℃で1〜12時間の熱処理を行う高温熱処理工程と、を含み、低温熱処理工程と高温熱処理工程のうち少なくとも一方の熱処理の一部を酸化雰囲気下で行う。

(もっと読む)

CMOSデバイスの自己形成金属シリサイド化ゲート

【課題】 CMOSデバイスの自己形成金属シリサイド化ゲートを提供すること。

【解決手段】 シリサイドが自己形成され(すなわち、別個の金属/シリコン反応ステップを必要とせずに形成され)、シリコン材料のCMP又はエッチ・バックを必要としない、金属シリサイド・ゲートをFETデバイスに形成するためのプロセス。第1のシリコン材料層(3)(ポリシリコン又はアモルファス・シリコン)が、ゲート誘電体(2)の上に形成され、次いで、金属層(4)が第1のシリコン材料層(3)の上に形成され、金属層(4)の上に第2のシリコン材料層(5)が形成される。その後、ソース/ドレイン活性化アニールのような高温(700℃より高い)処理ステップが実施され、このステップは、金属層(4)の金属を第1のシリコン材料層(13)におけるシリコン材料と反応させることにより、ゲート誘電体(2)の上にシリサイド層(30)を形成するのに有効である。第2の高温処理ステップ(ソース/ドレインのシリサイド化のような)を実施することができ、これは第2のシリコン材料層(5)におけるシリコン材料から第2のシリサイド層(50)を形成するのに有効である。シリサイド層の厚さは、高温処理において、第1のシリコン材料層の実質的にすべて及び第2のシリコン材料層の少なくとも一部が、シリサイド材料で置き換えられるような厚さである。従って、完全シリサイド化ゲート構造体を生成することができる。

(もっと読む)

半導体装置とその製造方法

【課題】 絶縁性金属酸化膜をゲート絶縁膜に使用したMOSトランジスタの特性を向上させることができる半導体装置とその製造方法を提供すること。

【解決手段】シリコン(半導体)基板1と、シリコン基板1の上に形成され、絶縁性金属酸化物で構成されるゲート絶縁膜14と、ゲート絶縁膜14の上に形成され、シリコンを含有するゲート電極18と、ゲート電極18の側方のシリコン基板10に形成され、ゲート絶縁膜14とゲート電極18と共にMOSトランジスタTR1を構成するソース/ドレイン領域22とを有し、ゲート電極18の少なくとも下面に鉄族元素を拡散させたことを特徴とする半導体装置による。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極に含まれる不純物に起因した品質の低下が抑制された高品質の半導体装置およびその製造方法を得ること。

【解決手段】半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、不純物が導入された複数の半導体膜が積層されてなるゲート電極と、を備え、前記ゲート電極は、前記不純物の不純物濃度プロファイルが前記複数の半導体膜の各層において急峻なピークを有し、前記絶縁膜上に形成された最下層の前記半導体膜の前記絶縁膜近傍における不純物濃度が他の前記半導体膜の不純物濃度よりも小とされている。

(もっと読む)

半導体装置のシリサイド膜の形成方法

【課題】 半導体装置のシリサイド膜の製造方法が開示される。

【解決手段】 まず、第1シリサイド膜を形成する。そして、前記第1シリサイド膜のうち、不連続部分がある場合、前記不連続部分に金属物質を選択的蒸着して、前記金属物質によって電気的に連結された第2シリサイド膜を形成する。前述した方法は、80nm以下のデザインルールを有する半導体ゲート電極上に不連続部分を含まないシリサイド膜を形成することができるのみならず、不連続部分を連結する工程で追加熱処理工程を行わなくても良いので、トランジスタの特性劣化を防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

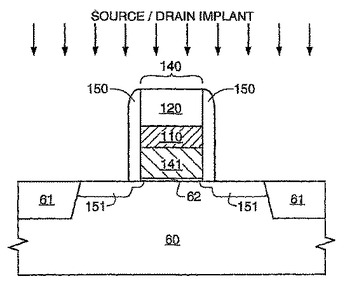

ゲート・スタック

【課題】 上部領域が破損しにくいゲート・スタックを提供する。

【解決手段】 半導体基板(110)においてソース/ドレイン領域を定めるのに用いられるゲート・スタック構造体及びその製造方法である。本方法は、(a)基板(110)の上にゲート誘電体層(120)を形成し、(b)ゲート誘電体層(120)の上にゲート・ポリシリコン層(130)を形成し、(c)ゲート・ポリシリコン層(130)の上部層(130a)にn型ドーパントを注入し、(d)基板(110)の上にゲート・スタック(132、134、122)を形成するように、ゲート・ポリシリコン層(130)及びゲート誘電体層(120)の一部をエッチングによって除去し、(e)窒素運搬ガスの存在下でゲート・スタック(132、134、122)の側壁を熱酸化することを含む。結果として、拡散バリア層(170)が、ドープ濃度に関わらずゲート・スタック(132、134、122)のポリシリコン材料内の同じ深さのところに形成される。したがって、ゲート・スタックのn型ドープ領域(132)は、ゲート・スタック(132、134、122)の非ドープ領域(134)の幅と等しい幅を有する。

(もっと読む)

ポリシリコンゲルマニウムゲートスタック及びその形成方法

従来のCMOSゲートスタックと比べて反転キャパシタンスを増大させるCMOSゲートスタックが記載される。ゲート誘電体層に近い従来のポリSiゲートの代わりに、ポリSiGeゲートを用いて、活性化され得る埋込まれたドーパント量を増加させる。この増加は、従来のCMOSゲートスタックにおける反転キャパシタンスを制限するポリシリコンの枯渇を克服する。ポリSiGe層をゲートスタックに組込むために、ゲート誘電体層とポリSiGe層との間にSi薄層を堆積させる。適切なサリサイド形成を確実にするために、ポリSiGe層の上にポリSi層のキャップを被せる。ポリSiGeの上に微粒子のポリSiを得るために、ポリSi層とポリSiGe層の間に第2のSi層を堆積させる (もっと読む)

メモリ素子及びその製造方法

【課題】

ショートチャネル効果を防止してメモリ素子のしきい電圧の調整を容易にし、ストレージノード接合領域で発生する接合漏れ電流を減少させてメモリ素子のデータ保持時間を増大させることのできるメモリ素子及びその製造方法を提供すること。

【解決手段】

凹部(600)が形成された半導体基板(610)と、凹部内部の半導体基板の表面下部に形成された第1接合領域(670A)と、凹部外部の半導体基板の表面下部に形成された複数の第2接合領域(670B)と、第1接合領域と第2接合領域との間の半導体基板の上に形成され、少なくとも一部分が凹部内部の半導体基板の上に形成されるゲート構造(655)と、ゲート構造間の埋込により第1接合領域上に形成される第1コンタクトプラグ(690A)と、ゲート構造間の埋込により第2接合領域上に形成される複数の第2コンタクトプラグ(690B)とを備えることを特徴とするメモリ素子を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】厚み均一で且つ低抵抗のシリサイド層をゲート電極に有する半導体装置およびその製造方法を提供する。

【解決手段】シリサイド化する高融点金属の堆積前に、ゲート電極上面に角が発生しないように端部丸めを実施した後にシリサイド化を行ことで、熱処理時に発生する膜応力の集中を緩和し、均一でかつ十分な厚さのシリサイド層を形成する。

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

61 - 80 / 81

[ Back to top ]