Fターム[5F140BF43]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388) | 断面形状 (1,038) | 溝掘りゲート (564)

Fターム[5F140BF43]に分類される特許

201 - 220 / 564

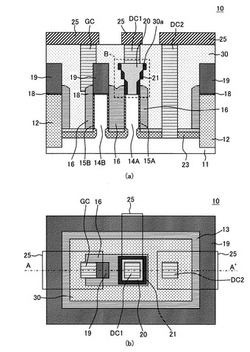

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

GaN系半導体素子およびその製造方法

【課題】SiO2からなるゲート絶縁膜を常圧CVDによって形成することで、十分なノーマリオフ特性が得られるGaN系半導体素子およびその製造方法を提供する。

【解決手段】基板11上にバッファ層13を介して積層されたp型のGaN系化合物半導体からなるチャネル層14とゲート電極Gとの間にゲート絶縁膜17が形成されたGaN系半導体素子1において、ゲート絶縁膜17が、常圧CVD法により成膜されたSiO2膜である。常圧CVD法により成膜されたSiO2膜は、Si−H結合や未結合手の発生が抑制された高品質のSiO2膜である。このようなSiO2膜により、GaN系半導体素子のしきい値の制御に及ぼす悪影響も抑制されるので、十分なノーマリオフ特性が得られる。

(もっと読む)

電界効果トランジスタ

【課題】高いしきい値電圧と大きい動作電流とを両立した電界効果トランジスタを提供すること。

【解決手段】基板と、前記基板上に形成され、窒化物系化合物半導体からなり、チャネル層を含む半導体層と、前記チャネル層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層上において前記ゲート電極を挟むように配置されたソース電極およびドレイン電極と、を備え、前記チャネル層の表面の、少なくとも前記ゲート電極直下の領域が、窒素極性の表面を含む。

(もっと読む)

窒化物半導体装置および窒化物半導体装置製造方法

【課題】窒素不足に起因する移動度の低下を抑制し、窒素不足に起因するリーク電流を低減することができる窒化物半導体装置、その製造方法を提供する。

【解決手段】窒化物半導体装置1は、基板10と、バッファ層11と、窒化物半導体層(第1窒化物半導体層12、第2窒化物半導体層13、第3窒化物半導体層14)と、第1電極22と、第2電極23と、制御電極25とを備える。第1電極22と第2電極23との間で第3窒化物半導体層14の表面から第2窒化物半導体層13に渡って凹状に形成されたリセス部16を備え、リセス部16は、絶縁性窒化物で形成された窒化物絶縁膜17を備え、制御電極25は、導電性窒化物で形成され窒化物絶縁膜17(ゲート絶縁膜)に重ねて配置されている。

(もっと読む)

集積回路構造

【課題】III−V族化合物半導体を含むトランジスタとその形成方法を提供する。

【解決手段】基板20、前記基板上にあり、III族とV族元素を含む第1のIII−V族化合物半導体材料で形成されたチャネル層26、前記チャネル層の上方の高ドープ半導体層30、前記高ドープ半導体層を穿通して形成され前記高ドープ半導体層の側壁に接触したゲート誘電体50、及び前記ゲート誘電体の下部部分上のゲート電極52を含み、ゲート誘電体50が前記ゲート電極の側壁上の側壁部分を有している集積回路構造。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法

【課題】低いオン抵抗と高い耐圧性とを有する電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法を提供する。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板101と、前記基板上に形成された高抵抗層103と、前記高抵抗層上に形成された、炭素濃度が1×1018cm−3以下であり層厚が10nmより厚く、100nm以下であるチャネル層104を含む半導体動作層106と、前記半導体動作層に前記チャネル層の内部に到る深さまで形成されたリセス部107と、前記半導体動作層上に前記リセス部を挟んで形成されたソース電極108およびドレイン電極109と、前記半導体動作層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜110と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極111と、を備える。

(もっと読む)

半導体装置

【目的】ゲート酸化膜の薄膜化が生じないようにして、ゲート耐圧の低下を防止することこができる半導体装置を提供する。

【解決手段】閉ループで蛇行した1条の第1トレンチ3と、この第1トレンチ3を囲む閉ループの第2トレンチ25と、第1トレンチ3と第2トレンチ25を接続する第3トレンチ71と、第1トレンチ3の曲線部とこれに対向する直線部を接続する第4トレンチ72とをそれぞれ形成し、第3トレンチ71に第1ゲートポリシリコン配線19、第4トレンチ72に第2ゲートポリシリコン配線20を形成する。第1、第2ゲートポリシリコン配線19、20を形成する第3、第4トレンチ71、72にトレンチ終端部がないために、第1、第2ゲートポリシリコン配線19,20下のゲート絶縁膜10が薄くならずゲート耐圧の低下を防止できる。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板と、前記基板上に形成されたバッファ層と、前記バッファ層上に形成された高抵抗層又は下地層と、前記高抵抗層又は下地層上に形成された、炭素を含有するキャリア濃度制御層と、前記キャリア濃度制御層上に形成されたキャリア走行層と、前記キャリア走行層上に形成された、前記キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層と、前記キャリア供給層から所定の深さに到るまで形成されたリセス部と、前記キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記キャリア供給層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル電位固定用のウェル給電用素子を設ける際に、縦型MOSトランジスタ間に素子分離用の埋込絶縁層を必要とせず、素子分離用の埋込絶縁層の形成に必要な面積を削減して、半導体装置の高集積化を図る。

【解決手段】半導体基板1に形成された第1導電型のウェル2内に、ウェル給電用素子Xと縦型MOSトランジスタYとが備えられ、ウェル給電用素子Xは、ウェル2と同じ導電型のボディ領域からなるピラー部P1を有し、ピラー部P1の上部には、第1導電型のウェル2の濃度よりも高い濃度を有する第1導電型の第1不純物拡散層13を備え、縦型MOSトランジスタYは、ウェル2と同じ導電型のボディ領域からなるピラー部P2を有し、かつ縦型MOSトランジスタYのピラー部P2の上部には、第2導電型の第2不純物拡散層7を備えることを特徴とする半導体装置を採用する。

(もっと読む)

電界効果トランジスタ

【課題】大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層13の表面領域に形成されたソース18s及びドレイン18dと、半導体活性層13上にゲート酸化膜14を介して形成されたゲート電極15と、ゲート電極15とドレイン18dの間の半導体活性層13上に形成されたパッシべーション膜20とを備える。電界効果トランジスタ10では、パッシベーション膜20を構成する二酸化シリコンの膜質が、ゲート酸化膜14を構成する二酸化シリコンの膜質よりも密度が粗である。

(もっと読む)

電界効果トランジスタ

【課題】耐電圧を高めて、大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層11の表面領域に形成されたソース16s及びドレイン16dと、半導体活性層11上にゲート酸化膜12を介して形成されたゲート電極13とを備える。電界効果トランジスタ10は、ゲート電極13とドレイン16dとの間の半導体活性層11内に形成された電界緩和層20を有する。電界緩和層20は、正の電荷が生じる第1の層21と負の電荷が生じる第2の層22とが、膜厚方向に交互に配置される積層構造を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コスト増や大型化を招くことなく、耐圧特性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体層13と、半導体層13上のゲート電極15、ソース電極16sおよびドレイン領域16dと、を備えたMOSFET1は、半導体層13中であってこの半導体層13の上面および下面それぞれから離間する中間領域に所定の導電性を備えたドーパント(例えばシリコン(Si))を含む縦方向電界緩和領域19を備えている。

(もっと読む)

電界効果トランジスタ

【課題】 ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタの下面または上面にボディ電極8を設ける。下面にボディ電極8を設ける場合、p型Si基板2上にAlN層31およびGaN層32の繰り返しによるバッファ層3を介してp−GaN層4を設け、バッファ層3の最上層のAlN層31を薄くし、p型Si基板の下面にボディ電極8を形成する。上面にボディ電極8を設ける場合、サファイア基板21上にp−GaN層4を設け、ソース電極5およびドレイン電極6下の部分にAlGaN層13を設け、AlGaN層13上にボディ電極8を設ける。アバランシェにより生じる正孔20をボディ電極8より引き抜く。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN/AlGaN−HEMTをE−mode動作させるに当たり、Vf及び最大ドレイン電流を向上させ、かつ良好なゲート−ドレイン間耐圧を有し、さらに、ゲートリーク電流を抑制する。

【解決手段】基板15と、この基板上に形成されており、GaN層17及びAlGaN層19が順次積層されてなる積層構造体21とを含む下地13と、AlGaN層に開口形成されているゲート形成用凹部27と、このゲート形成用凹部の内側底面27a、ゲート形成用凹部の内側壁面27b、及びゲート形成用凹部外の下地面13aを一体的に被覆して形成されているSiN膜29と、SiN膜の表面を被覆して形成されているアモルファスAlN膜31と、SiN膜及びアモルファスAlN膜が形成されているゲート形成用凹部を埋め込むゲート電極33とを具える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】アニール時の酸化剤の拡散によるゲート電極の酸化を抑制する。

【解決手段】半導体基板の活性領域にゲートトレンチを形成する工程と、前記半導体基板の活性領域上及びゲートトレンチ内にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の前記ゲートトレンチの開口縁近傍における窒素濃度が、前記ゲートトレンチの底部近傍における窒素濃度よりも高濃度となるように、プラズマ窒化処理によって前記ゲート絶縁膜に窒素を導入する窒化工程と、前記ゲートトレンチを埋めて前記ゲート絶縁膜を覆うようにゲート電極層を積層してから、前記ゲート電極層をエッチングによりパターニングしてゲート電極を形成するゲート電極形成工程と、前記ゲート電極層のエッチングによって露出した前記活性領域をアニールするアニール工程と、を具備してなることを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

GaN系電界効果トランジスタ

【課題】低オン抵抗・高耐圧で動作可能なGaN系化合物半導体デバイスを提供する。

【解決手段】基板上に形成されたバッファ層、チャネル層と、前記チャネル層上に形成され、ドリフト層と、前記ドリフト層上に配置されたソース電極およびドレイン電極と、ドリフト層に形成されたリセス部の内表面および前記ドリフト層の表面に形成された絶縁膜と、前記絶縁膜上に形成されたフィールドプレート部を有するゲート電極とを備えたGaN系電界効果トランジスタにおいて、前記ドリフト層は、前記リセス部と前記ドレイン電極との間に、シートキャリア密度が5×1013cm−2以上、1×1014cm−2以下のn型GaN系化合物半導体からなる電界緩和領域を有し、前記ドリフト層の前記電界緩和領域上に形成された前記絶縁膜の厚さが300nm以上であることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

窒化物半導体装置

【課題】窒化物半導体装置の表面安定化を実現し、これにより、電流コラプスを抑制した窒化物半導体装置を提供する。

【解決手段】第1の窒化物半導体からなるキャリア走行層103と、キャリア走行層103の上方に設けられた第2の窒化物半導体からなるキャリア供給層104と、キャリア走行層103とオーミック接触するソース電極106及びドレイン電極107と、キャリア供給層104の上方に設けられたゲート電極110とを備え、ゲート電極110とドレイン電極107との間において、キャリア供給層104の表面の少なくとも一部が、構成元素として窒素元素を含む窒化物絶縁膜で覆われ、窒化物絶縁膜において、窒素元素の含有量が他の構成元素の含有量の合計よりも多い。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

201 - 220 / 564

[ Back to top ]