Fターム[5F140BG43]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極形成後の処理 (1,641) | 不純物の導入 (232) | イオン注入 (191)

Fターム[5F140BG43]に分類される特許

141 - 160 / 191

半導体装置及びその製造方法

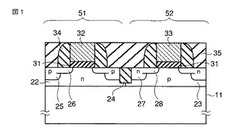

【課題】 製造方法が容易なデュアルメタルゲート構造を実現することができ、CMOSデバイス等の特性向上に寄与する。

【解決手段】 基板上に、pチャネルMISトランジスタ51とnチャネルMISトランジスタ52を具備した半導体装置であって、pチャネルMISトランジスタ51のゲート電極32の膜厚方向に対するTaC(111)面の結晶配向比率[TaC(111)面/{TaC(111)面+TaC(200)面}]は80%以上であり、nチャネルMISトランジスタ52のゲート電極53の膜厚方向に対するTaC(111)面の結晶配向比率[TaC(111)面/{TaC(111)面+TaC(200)面}]は60%以下である。

(もっと読む)

半導体装置

【課題】プラズマチャージによる影響を抑制することによる信頼性の向上、かつ、微細化が図られた半導体装置を提供する。

【解決手段】本発明にかかる半導体装置は、第1導電型の半導体層10と、半導体層10に設けられた分離絶縁層20により特定された第1領域10Aおよび第2領域10Bと、第2領域10Bに設けられたゲート絶縁層32と、第1領域10Aおよび第2領域10Bの上方に設けられた連続したゲート電極34と、第2領域10Bに設けられたゲート電極34を挟む不純物領域36と、を含み、少なくとも第1領域10Aの上方に位置するゲート電極34は、第2導電型の半導体部である。

(もっと読む)

フィールドプレートを具える半導体デバイス及びその製造方法

半導体の製造方法は、半導体デバイス層中に浅溝隔離構造14の形成を具える。前記浅溝隔離構造は、前記半導体デバイス層を形成するフィールド領域を囲んだU字形又はO字形であり、前記半導体デバイス層は、導電性を得るためにドープ及び/又は自滅される。前記半導体デバイスは、延在したドレイン領域50又はドリフト領域、及び、ドレイン領域42を有する。絶縁ゲート26は、本体領域の上部に設けられる。ソース領域34、40は、深ソース領域40及び浅ソース領域34を有するように加工されている。前記本体と同じ導電型のコンタクト領域60は、前記深ソース領域40に隣接して設けられる。前記本体は、前記浅ソース領域34の下で、前記コンタクト領域60と接触するように延在している。  (もっと読む)

(もっと読む)

炭素クラスターの注入により半導体デバイスを製造するためのシステムおよび方法

集積回路中のPMOSトランジスタ構造の製造において基板にホウ素およびリンをドープする場合に、炭素クラスターを基板中に注入してトランジスタの接合特性を改善することを包含するプロセスを開示する。この新規アプローチに由来するプロセスは二つある:(1)USJ形成のための拡散制御;および(2)ストレスエンジニアリングのための高ドーズ量炭素注入。USJ形成のための拡散制御を、PMOS中のソース/ドレイン構造のホウ素または浅いホウ素クラスターインプラントと併せて説明する。より詳細には、最初に、C16Hx+のようなクラスター炭素イオンを、これに続くホウ素インプラントとほぼ同じドーズ量でソース/ドレイン領域中に注入し;その後、好ましくはB18Hx+またはB10Hx+のようなホウ化水素クラスターを用いて、浅いホウ素、ホウ素クラスター、リンまたはリンクラスターイオンインプラントを行って、ソース/ドレインエクステンションを形成する。これに続くアニーリングおよび活性化において、炭素原子による格子間欠陥のゲッタリングによりホウ素の拡散は低減する。 (もっと読む)

半導体装置の製造方法

【課題】 複数の電圧レベルを扱う半導体装置の製造方法を提供する。

【解決手段】シリコン基板上に、同一工程でゲート酸化膜、ポリシリコン電極層を形成し、パターニングしてゲート電極パターンを形成し、基板とゲート電極パターンの表面を酸化し、ゲート電極下部において端部から中央部に向かって酸化を進行させ、ゲート酸化膜と一体化し、ゲート電極パターンの側壁から中央部に向かって次第に厚さが減少し、中央部の厚さが低電圧駆動時に最適な膜厚であり、端部において耐圧を向上したゲート酸化膜を形成する。ゲート電極パターンをマスクとして不純物を低濃度でドープし、比較的高電圧で駆動されるMOSトランジスタのゲート電極および第1ソース/ドレイン領域に適した低濃度にすると共に、比較的低電圧で駆動されるMOSトランジスタのLDD領域に適した低濃度とする。

(もっと読む)

半導体装置およびその製造方法

【課題】フルシリサイド化ゲート電極を含むMISFETに、ライナー膜によるチャネル部分へのストレス印加技術を適用可能な半導体装置およびその製造方法を実現する。

【解決手段】MISFET形成済みの半導体基板上に第1のライナーシリコン窒化膜11aを形成し、ゲート電極6の側方を十分に充填するよう、第1のライナーシリコン窒化膜11a上にシリコン酸化膜等の絶縁膜を形成する。次に、絶縁膜および第1のライナーシリコン窒化膜11aに平坦化処理を施して、ポリシリコンゲート電極6aを露出させ、第1のライナーシリコン窒化膜11aを残置しつつ絶縁膜を除去する。露出したゲート電極6をフルシリサイド化し、第1のライナーシリコン窒化膜11aおよび露出したフルシリサイド化ゲート電極6を覆う第2のライナーシリコン窒化膜11bを形成する。

(もっと読む)

酸化シリコン層の選択的除去

【解決手段】本発明は、装置を製造する方法に関し、前記装置の第1領域内に第1酸化シリコン層を形成し、前記装置の第2領域内に第2酸化シリコン層を形成するステップと、前記第1領域内に第1タイプのドーピングイオンを注入するステップと、前記第2領域内に第2タイプのドーピングイオンを注入するステップと、前記第1酸化シリコン層が除去され、前記第2酸化シリコン層の少なくとも一部が残るように、定められた継続時間前記第1及び第2領域をエッチングするステップとを備える。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物からなるゲート電極の抵抗ばらつきの発生を抑制できる半導体装置の製造方法を実現すること。

【解決手段】半導体装置の製造方法は、半導体基板200上にゲート絶縁膜201を形成する工程と、前記ゲート絶縁膜上に、金属と半導体との化合物からなり、所定のゲート長を有するゲート電極206を形成する工程とを含む半導体装置の製造方法であって、前記ゲート電極206を形成する工程は、平均粒径が前記所定のゲート長に対応した所定値以下に制御され、かつ、シリコンおよびゲルマニウムの少なくとも一方を含む、多結晶の半導体膜205を形成する工程と、前記半導体膜205上に金属膜203を形成する工程と、熱処理により前記半導体膜205と前記金属膜203とを反応させ、前記半導体膜205の全体を金属半導体化合物層に変える工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 金属材料からなるゲート電極を有するnチャネル型MISトランジスタおよびpチャネル型MISトランジスタの製造工程を簡略化する。

【解決手段】 ゲート絶縁膜5上に堆積したルテニウム膜をパターニングすることによって、nチャネル型MISトランジスタおよびpチャネル型MISトランジスタのそれぞれのゲート電極を同時に形成する。次に、それぞれのゲート電極に酸素を導入することによって、仕事関数が大きいゲート電極6Aに変換する。その後、nチャネル型MISトランジスタのゲート電極6Aを水素アニールで選択的に還元することによって、仕事関数の小さいゲート電極6Bに変換する。

(もっと読む)

多層ゲート電極及びその製造方法、ならびに多層ゲート電極が形成された半導体素子及びその製造方法

【課題】高温で安定であり、抵抗等の特性が改善され、信頼性が高い多層ゲート電極及びこれを備える半導体素子、ならびに多層ゲート電極の製造方法及び半導体素子の製造方法を提供する。

【解決手段】多層ゲート電極は、ゲート絶縁膜上に形成され導電型不純物がドープされた多結晶半導体膜と、前記多結晶半導体膜上に形成されタングステン(W1−x)及び非タングステン金属(Mx、x=0.01〜0.55)を含むオーミックコンタクト膜と、前記オーミックコンタクト膜の上に形成された金属バリヤ膜と、前記金属バリヤ膜の上に形成された高融点金属膜と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜を劣化させることなくキャリアの移動度を向上させたMISFETを提供する。

【解決手段】MISFETにおいて、ゲート電極5のうち素子分離領域の上に設けられた部分25aは格子定数を変化させる不純物が導入されている。ゲート電極5の部分25を起点としてチャネル領域にキャリア移動度を向上させる方向のストレスを印加する。

(もっと読む)

MIS型電界効果トランジスタの製造方法及び半導体記憶装置の製造方法

【課題】欠陥が誘起され難く、水素や水分に対する耐性が強い金属酸化物をゲート絶縁膜として用いたMIS型電界効果トランジスタの製造方法を提供する。

【解決手段】MIS型電界効果トランジスタの製造方法は、シリコン基板上に金属酸化物膜を形成する工程と、金属酸化物膜上にゲート電極を形成する工程と、前記金属酸化物膜にフッ素を導入する工程とを有し、金属酸化物膜としてHfの酸化物、Alの酸化物を用いる。例えば、金属酸化物膜へのフッ素の導入は、シリコン基板上へ金属酸化物膜を形成する前にシリコン基板にフッ素またはフッ素を含むイオンを導入し、金属酸化物膜を形成した後にシリコン基板を熱処理してシリコン基板から金属酸化物膜へフッ素を拡散させることにより行う。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】シリコン基板の表面から非常に浅い領域に高濃度の不純物を導入することができる半導体装置の製造方法を提供する。

【解決手段】p型シリコン基板1上の所定の位置に形成された所定形状のゲート絶縁膜4とゲート電極5を含むゲート構造のゲート長方向両側に浅い接合のソース/ドレイン領域を形成する半導体装置の製造方法であって、ソース/ドレイン領域の形成領域を、所定の深さにエッチングするエッチング工程と、p型シリコン基板1上に所定の組成の30Si層を堆積させ、ソース/ドレイン領域の形成領域に30Si層21を選択エピタキシャル成長させる30Si層形成工程と、p型シリコン基板1に中性子線50を照射して、30Si層21中に所定の濃度の31Pを形成する中性子線照射工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】しきい値電圧のばらつき及びNBTI現象を抑制し、且つ、接合リーク電流の少ない優れたトランジスタ特性を有する半導体装置を提供する。

【解決手段】N型半導体基板21上にゲート絶縁膜22及びゲート電極23が形成されている。そして、ゲート電極23の側方下に位置する半導体基板21には、P型エクステンション領域24と、その外側にP型ソース・ドレイン領域26が形成されている。そして、ゲート電極23及びP型ソース・ドレイン領域26上には、シリサイド層27a、27bが形成されている。そして、ゲート絶縁膜22の両端部、及び、ゲート電極23とシリサイド層27bとの間に位置するP型エクステンション領域24とP型ソース・ドレイン領域26の表面部にフッ素注入層25が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の目的は、素子分離絶縁膜の端部におけるシリサイド化を抑制して接合リークの発生を防止した半導体装置およびその製造方法を提供することにある。

【解決手段】本実施形態に係る半導体装置は、半導体基板1に形成され、活性領域を区画する素子分離絶縁膜3と、活性領域における半導体基板1上に、ゲート絶縁膜4を介して形成されたゲート電極5と、ゲート電極5の両側に形成されたサイドウォール絶縁膜6と、ゲート電極5の両側における半導体基板1に形成されたソース・ドレイン領域8と、ソース・ドレイン領域8の表層に形成されたシリサイド層10と、素子分離絶縁膜の端部に生じた窪み部3aを埋めるように形成され、端部における半導体基板1のシリサイド化を防止する第1絶縁膜21とを有する。

(もっと読む)

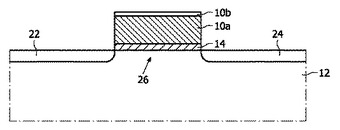

ポリシリコン電極を有する半導体デバイス

MOSトランジスタなどの半導体デバイスを製造する方法。本デバイスは、ポリシリコンのゲート(10)および、半導体基板(12)内に形成されチャネル領域(26)で分離されたドーピング領域(22,24)を備える。後の熱アニールの間にドーパント・イオンが拡散することを阻害するために、半導体基板の露出面を、例えばイオン衝撃によって、アモルファス化する。活性化およびポリシリコン再成長のためのサーマルバジェットが低いことは、ソース/ドレイン領域における急峻なドーピングプロファイルを確実にするために好ましい。結果として、ゲート電極の上部(10b)は、アモルファスのままである。ポリシリコンの下部を用いて低抵抗の接点を作成するために、ゲート電極の上部を除去する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 シリサイドがサイドウォールの下側に形成されないようにすることにより、当該シリサイド起因の接合リーク電流等の電気特性の不良の発生を低減するための半導体装置及びその製造方法を提供する。

【解決手段】 サイドウォールが形成されている半導体基板の上に制御膜を形成した後、シリサイドを形成するための活性化領域をイオン注入法により形成する。その後、制御膜を除去し、金属膜を形成し、熱処理してシリサイドを活性化領域に形成する。

(もっと読む)

多重仕事関数金属窒化物ゲート電極を有するMOSトランジスタ、これを採用するCMOS集積回路素子及びその製造方法

【課題】多重仕事関数金属窒化物ゲート電極を有するMOSトランジスタが提供される。

【解決手段】MOSトランジスタは半導体基板及び前記半導体基板上に配置された中心ゲート電極を具備する。前記中心ゲート電極は金属窒化物からなる。前記中心ゲート電極の両側壁上にそれぞれソース側ゲート電極及びドレイン側ゲート電極が提供される。前記ソース/ドレイン側ゲート電極は窒素よりも小さい電気陰性度を有する第1不純物または窒素よりも大きい電気陰性度を有する第2不純物を含むドープ金属窒化物からなる。前記MOSトランジスタを採用するCMOS集積回路素子及びその製造方法も提供される。

(もっと読む)

PFETの移動度を強化したステップ埋め込みSiGe構造

【課題】埋設されたSiGe層を有し、そのSiGe層の浅い部分がPFETチャネルに近く、SiGe層の深い部分がPFETチャネルからさらに離れているPFETを含むデバイスと、その製造方法を提供する。

【解決手段】SiGe層はテーパーされているチャネル方向に面する側面に境界を有している。このような形状によって、PFETチャネルは実質的に拡張接合特性を劣化させる必要なく、大きい圧縮応力を受けることができる。テーパーされたSiGe境界は複数のディスクリートなステップとして構成される。例えば2、3以上のディスクリートなステップが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率材料からなるゲート絶縁膜であっても、しきい値電圧がシフトすることがない半導体装置及びその製造方法を提供する

【解決手段】シリコン基板10とHigh−kゲート絶縁膜18との間にシリコン窒化膜16からなる透過防止膜を挿入してHigh−kゲート絶縁膜18から酸素が欠損するのを防止すると共に、ゲート電極層20の成膜後に酸素アニールを行って酸素を補うようにする。透過防止膜であるシリコン窒化膜16はシリコン酸窒化膜17となるが膜厚が変化せず、トランジスタの性能を低下させることなく、High−kゲート絶縁膜18の酸素欠損による特性劣化を防止する。

(もっと読む)

141 - 160 / 191

[ Back to top ]