Fターム[5F140BG43]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極形成後の処理 (1,641) | 不純物の導入 (232) | イオン注入 (191)

Fターム[5F140BG43]に分類される特許

161 - 180 / 191

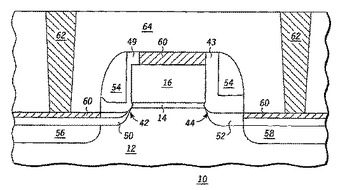

非対称性誘電領域を備える半導体装置の形成方法及びその半導体装置の構造

半導体基板(12)を形成するステップ、半導体基板の上方に第一側面及び第二側面を備えるゲート電極(16)を形成するステップ、及びゲート電極の下方にゲート誘電体を形成するステップを含む半導体装置(10)の形成方法。ゲート誘電体は、ゲート電極の下方でゲート電極の第一側面に隣接した第一領域(42)と、ゲート電極の下方でゲート電極の第二側面に隣接した第二領域(44)と、ゲート電極の下方で第一領域及び第二領域間にある第三領域(14)とを備えている。第一領域は、第二領域よりも薄く、第三領域は、第一領域よりも薄く、更に第二領域よりも薄い。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極の端部近傍領域に自己整合的にオーバーラップし、電界緩和層として働く、低濃度拡散層を有する高耐圧MOSトランジスタ及びその製造方法を提供することを目的とする。

【解決手段】 第1のN−低濃度拡散層105と、ゲート電極端部126を画定する熱酸化膜106とは、共に、シリコン窒化膜103からなるパターンをマスクとして自己整合的に形成され、更に、第1のN−低濃度拡散層105に隣接する第2のN−低濃度拡散層109は、ゲート電極108をマスクとして自己整合的に形成される。結果、電界緩和層として働く第1のN−低濃度拡散層105と、ポリシリコンゲート電極108の端部近傍領域に位置する熱酸化膜106とは、水平方向位置でみて、互いに自己整合的にオーバーラップしている。ポリシリコンゲート電極108の端部近傍領域にオーバーラップし、電界緩和層として働く第1のN−低濃度拡散層105が、ゲート電極端部126に自己整合的に形成される。

(もっと読む)

半導体装置

【課題】 ショットキー型電界効果トランジスターに於いて、殊にソース領域近傍のチャネル領域に対するゲート電極の制御性を高めて、素子の電流駆動能力の向上を図る。

【解決手段】 ゲート絶縁膜を異なる誘電率を持つ膜の積層とすることで、誘電率の高い材料のみで形成した場合と比べてゲート絶縁膜の幾何学的な意味の厚さを薄く形成することを可能とし、ゲート電極から出た電気力線のゲート絶縁膜の側面から外への漏れに起因する、殊にソース領域近傍のチャネル領域の電位に対するゲート電極の制御性の低下を抑制する事が可能となる。また、誘電率の高い材料よりなるゲート側壁絶縁膜12を設ける事に依り、異なる誘電率を持つ物質の界面に於ける電気力線の屈折に依って、ゲート電極から出た電気力線をソース領域近傍のチャネル領域に集める事が可能となり、ソース領域とチャネル領域との間に形成されるショットキー障壁を薄くし、その抵抗を低減する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の高抵抗化を防ぐとともに、Poly−Siからなるゲート電極を形成する場合と設計事項を変えることなく、不純物イオンのチャネリング現象を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】基板11上に、ポリシリコンからなるゲート電極14を形成する工程と、ゲート電極14の表面を露出させる状態で、基板11上にレジストマスクRを形成する工程と、イオン注入法により、レジストマスクRから露出したゲート電極14の表面側にSiを注入することで、ゲート電極14の表面側に選択的に非晶質層21を形成する工程と、レジストマスクRを除去した後、ゲート電極14の両側の基板11の表面側に不純物イオンを注入して、SD領域を形成する工程と、熱処理を行うことで、SD領域の前記不純物イオンを活性化させるとともに、非晶質層21をポリシリコンに変化させる工程とを有することを特徴とする半導体装置の製造方法である。

(もっと読む)

高電圧用トランジスタの製造方法

【課題】高電圧用トランジスタの製造方法においてシリコン窒化膜を不純物注入時に防護膜とすることによってスペース酸化膜を形成しなくてもソース/ドレイン拡散領域を二重拡散ドレインジャンクション構造とし一度のパターン工程及びイオン注入工程により安定した二重拡散構造のソース/ドレイン拡散領域を形成する。

【解決手段】本方法は(a)半導体基板にゲート酸化膜、多結晶シリコン層及びシリコン窒化膜を順番に形成する段階と(b)前記シリコン窒化膜、前記多結晶シリコン層及び前記ゲート酸化膜をフォトリソグラフィ工程及び等方性エッチング工程によりパターニングして窒化膜シェード及び多結晶シリコンゲート電極を形成する段階と(c)前記窒化膜シェードをイオン注入に対する防護膜として前記基板に不純物をイオン注入するとともに熱処理することで二重拡散構造のソース−ドレイン拡散領域を形成する段階と(d)前記窒化膜シェードを除去する段階とを備える。

(もっと読む)

半導体装置とその製造方法

【課題】 絶縁性金属酸化膜をゲート絶縁膜に使用したMOSトランジスタの特性を向上させることができる半導体装置とその製造方法を提供すること。

【解決手段】シリコン(半導体)基板1と、シリコン基板1の上に形成され、絶縁性金属酸化物で構成されるゲート絶縁膜14と、ゲート絶縁膜14の上に形成され、シリコンを含有するゲート電極18と、ゲート電極18の側方のシリコン基板10に形成され、ゲート絶縁膜14とゲート電極18と共にMOSトランジスタTR1を構成するソース/ドレイン領域22とを有し、ゲート電極18の少なくとも下面に鉄族元素を拡散させたことを特徴とする半導体装置による。

(もっと読む)

絶縁ゲート電界効果トランジスタの製造方法および絶縁ゲート電界効果トランジスタ

【課題】ゲート長の短縮に対応して最適な接合深さのエクステンション部を形成できなくなってきている。

【解決手段】ゲートスタック7と側壁絶縁膜9からなる所定の幅のスペーサをマスクとする不純物のイオン注入と活性化アニールにより、2つのソース・ドレイン領域10をPウェル3に形成する。側壁絶縁膜9を除去し、これより薄い隔壁絶縁膜11を形成することによって、このスペーサの幅方向両側を後退させる。これによりスペーサのエッジと2つのソース・ドレイン領域10のエッジとを幅方向両側で離す。この状態で、後退したスペーサの幅方向両側に露出し2つのソース・ドレイン領域10を含むウェル領域に選択的なエピタキシャル成長により半導体材料を成長させ、後退したスペーサにより分離する2つのエクステンション部12を形成する。この製法においては、イオン注入の活性化アニールによりエクステンション部12内の不純物がPウェル3内に熱拡散しない。

(もっと読む)

半導体装置の製造方法

ゲート電極にイオン注入されるホウ素のゲート絶縁膜突き抜けを抑制し、チャネル領域の移動度の低下を抑制することのできる半導体装置の製造方法を提供する。 半導体装置の製造方法は、半導体基板の活性領域上にゲート絶縁層を形成する工程と、上記ゲート絶縁層表面側から活性窒素により窒素を導入する工程と、窒素を導入したゲート絶縁層内の、表面側で高く、半導体基板との界面で低い窒素濃度分布を保つようにNOガス雰囲気中でのアニール処理を施す工程と、を含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させることが可能な技術を提供する。

【解決手段】ゲート構造20及びオフセットスペーサ5a,5bを覆って半導体基板1上に下層膜8、中層膜9及び上層膜10を順に形成する。下層膜8及び上層膜10は、LPCVD法を用いてTEOSを分解することにより形成されるシリコン酸化膜である。そして、下層膜8、中層膜9及び上層膜10を部分的に除去して半導体基板1を露出させ、ゲート構造20の側面上に下層膜8、中層膜9及び上層膜10を含むサイドウォールスペーサをオフセットスペーサ5aを介して形成する。

(もっと読む)

半導体装置の製造方法

不純物のゲート絶縁膜突き抜けを抑制できると共にソース/ドレイン領域の容量増大、リーク電流増大を抑制できる半導体装置の製造方法を提供する。 半導体装置の製造方法は、n型ウェル内にn型閾値調整領域を有する半導体基板上にゲート絶縁膜を介して、ゲート電極を形成し、低い加速エネルギで、p型不純物をイオン注入してゲート電極両側の半導体基板内にエクステンション領域を形成し、ゲート電極の側壁上に、サイドウォールスペーサを形成し、ゲート電極内で実質的異常テーリングを生じない低いドーズ量、比較的高い加速エネルギで、p型不純物をイオン注入して閾値調整領域より深いp型ソース/ドレイン領域を形成し、半導体基板に原子をイオン注入し、ゲート電極とソース・ドレイン領域の上層をアモルファス化し、高ドーズ量で、p型不純物をイオン注入し、ソース/ドレイン領域内に高濃度領域を形成し、イオン注入した不純物を活性化する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】微細化・高速化可能な半導体装置に必要なNiシリサイド層を形成する際に、低抵抗層であるNiSi層を安定して形成すると共にシリコン−シリサイド界面抵抗を低減する。

【解決手段】シリコン基板100上にゲート電極103が形成されている。シリコン基板100におけるゲート電極103の両側にソース・ドレイン領域となる不純物拡散層109が形成されている。不純物拡散層109上に積層シリサイド層114が形成されている。積層シリサイド層114は、界面層であるHfシリサイド層111と、表面層であるNiシリサイド層113とから構成されている。

(もっと読む)

半導体集積回路

【課題】ソース電位(VSS)との間に低不純物濃度のウェル領域を具備することにより、容量素子と他の回路素子との容量結合を抑制する。

【解決手段】N型の基板10上にP型のウェル領域11とN型のウェル領域12を形成する。N型ウェル領域12の表面にゲート電極14、ソース・ドレイン領域13、N型の拡散領域15を形成し、ゲート酸化膜16を誘電体として容量素子を形成する。P型のウェル領域11にはソース電位(VSS)を印加する。ゲート電極14を一方の端子Aとし、ソース・ドレイン領域13とN型の拡散領域12とを他方の端子Bとする。N型ウェル領域12とP型ウェル領域11とが低濃度PN接合となるので、他方の端子Bとソース電位(VSS)間の寄生容量を低減できる。

(もっと読む)

深く炭素がドーピングされた領域並びに隆起したドナーがドーピングされたソース及びドレインを特徴とする歪みnMOSトランジスタ

本発明に係る複数の実施例は、炭素がドーピングされた領域、及び隆起したソース/ドレイン領域を有することで、nMOSトランジスタチャネル中に引っ張り応力を供する。

(もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧およびドレイン電流の経時的変化を抑制できる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明における第1形態の半導体装置の製造方法では、半導体基板10にフッ素をイオン注入した後に、半導体基板10の上にゲート絶縁膜14A、ゲート電極15Aおよび保護膜16Aを形成し、再度フッ素をイオン注入する。さらに、p型ソース・ドレインエクステンション領域18およびソース・ドレイン領域19を形成する。

(もっと読む)

半導体装置の製造方法および半導体製造装置

【課題】 n型不純物が導入されたレジスト膜を除去する工程において、異常生成物の発生を抑制することができる技術を提供する。

【解決手段】 ポリシリコン膜15上にレジスト膜16を形成した後、このレジスト膜16に対して露光・現像することにより、レジスト膜16をパターニングする。パターニングは、ポリシリコン膜15のゲート電極形成領域に開口部17が形成されるように行う。次に、パターニングしたレジスト膜16をマスクにして、開口部17から露出したポリシリコン膜15内にリンを注入する。このとき、マスクであるレジスト膜16にもリンが注入されて硬化層16aが形成される。次に、酸素ガスおよびフォーミングガスを導入して硬化層16aおよびレジスト膜16を除去する。ここで、酸素ガスとフォーミングガスとの混合ガスに対するフォーミングガスの体積比率を5%以上30%以下にする。

(もっと読む)

集積回路の領域に、特にトランジスタの電極にコンタクト・パッドを生成するための方法

【課題】コンパクト・パッドの生成について改善された方法を提供する。

【解決手段】領域(51)は、該領域の表面の少なくとも一部に伸長する区域(510)であって、該領域に対して選択的に除去することが可能な材料から形成される区域を作成するよう、局所的に変更される。該領域は、絶縁材料(7)で覆われており、該区域の表面に出現するオリフィス(90)が、該絶縁材料内に形成される。該選択的に除去が可能である材料は、該区域に代わってキャビティ(520)を形成するように、該区域から、オリフィスを介して除去される。キャビティおよびオリフィスは、少なくとも1つの導電性材料(91)で充填される。

(もっと読む)

半導体装置の製造方法、電極膜、MOSトランジスタ、及び半導体装置

【課題】

容易に膜厚が制御され、かつ結晶性が良好であり、低抵抗率や良好なエッチング選択性等といった、良好な特性を示すシリサイド膜およびその作製手段を提供する。

【解決手段】

本発明では、半導体基板上に電極膜を成膜する時、基板温度を400℃から900℃まで加熱しながら、成膜速度を極めて遅くして(1〜1000Å/min)堆積させる。また、電極膜を成膜する前に、ArイオンやGeイオンやXeイオンによって表面を非晶質化するためのイオン注入をおこなってもよい。また、電極膜を成膜中にSiが電極膜中に拡散するための時間およびシリサイド化反応が進む時間が、成膜時間だけでは足らない場合は、数原子層成膜した後、Siが拡散してシリサイド化反応が進むまで成膜を止めて、適切な時間が経過した後、再び電極膜を成膜する、多段階成膜法をおこなっても良い。

(もっと読む)

FETにおける埋め込みバイアス・ウェル

【課題】 リーク電流及び接合キャパシタンスを除去又は減少させるために、半導体デバイスにおける新規な構造体を提供する。

【解決手段】 半導体装置の構造体及び該構造体を製造するための方法が開示される。半導体構造体は、第1及び第2のソース/ドレイン領域、該第1及び第2のソース/ドレイン領域の間に配置されたチャネル領域、該チャネル領域と物理的に接する埋め込みウェル領域、該埋め込みウェル領域と該第1のソース/ドレイン領域との間に配置され、かつ、該埋め込みウェル領域と該第2のソース/ドレイン領域との間に配置される埋め込みバリア領域とを含み、該埋め込みバリア領域が、該埋め込みウェル領域と該第1のソース/ドレイン領域との間のリーク電流及びドーパント拡散、並びに該埋め込みウェル領域と該第2のソース/ドレイン領域との間のリーク電流及びドーパント拡散を防止する。

(もっと読む)

半導体装置の製造方法

【課題】 短波長光の照射による活性化により、浅接合の拡散層を形成する際の、ゲート絶縁膜中のトラップの発生を抑える。

【解決手段】 半導体装置の製造において、まず、基板に、ゲート絶縁膜を介して、ゲート電極を形成する。少なくともゲート電極をマスクとして、不純物を注入し、拡散層を形成する。また、この拡散層形成のための不純物注入の前又は後に、少なくともゲート電極をマスクとして、フッ素イオンを注入する。更に、波長約1000nm以下の光を、約1ミリ秒以内の時間照射する。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造工程を簡略化して製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】 本発明に係る半導体装置は、シリコン基板1上に形成された第1及び第2のオフセット絶縁膜2a,2bと、第1のオフセット絶縁膜2aと第2のオフセット絶縁膜2bとの間に位置するシリコン基板1上に形成されたゲート酸化膜5と、ゲート酸化膜5上、第1のオフセット絶縁膜2aの一部上及び第2のオフセット絶縁膜2bの一部上に形成されたN型のゲート電極6と、ゲート電極6の外側に位置し且つ第1のオフセット絶縁膜2aに隣接するシリコン基板1に形成されたP型のソース領域の不純物層7aと、ゲート電極6の外側に位置し且つ第2のオフセット絶縁膜2bに隣接するシリコン基板1に形成されたP型のドレイン領域の不純物層7bとを具備する。

(もっと読む)

161 - 180 / 191

[ Back to top ]