Fターム[5F140BG43]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極形成後の処理 (1,641) | 不純物の導入 (232) | イオン注入 (191)

Fターム[5F140BG43]に分類される特許

41 - 60 / 191

半導体装置及びその製造方法

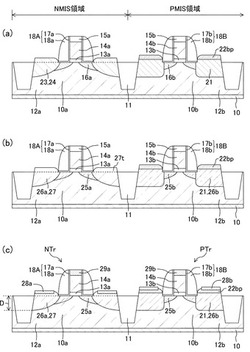

【課題】炭素含有シリコン領域を有するn型MISトランジスタを備えた半導体装置において、チャネル領域のゲート長方向に印加される引っ張り応力の大きさを、効果的に増大させる。

【解決手段】少なくともn型MISトランジスタNTrを有する半導体装置において、n型MISトランジスタnTrは、半導体基板10における第1の半導体領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール18Aと、第1のサイドウォール18Aの外側方に形成された炭素含有シリコン領域27とを備え、炭素含有シリコン領域27の上面高さは、第1の半導体領域10aにおける第1のゲート絶縁膜13aの下に位置する領域の上面高さよりも高い。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのしきい値のばらつきを抑制する。

【解決手段】半導体基板1に素子分離領域2を形成し、MISFETのしきい値調整用のチャネルドープイオン注入を行なってから、ゲート絶縁膜5a,5bおよびゲート電極GE1,GE2を形成する。それから、イオン注入によりエクステンション領域7a,7bおよびハロー領域8a,8bを形成し、更に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することにより拡散防止領域10a,10bを形成する。その後、ゲート電極GE1,GE2の側壁上にサイドウォールSWを形成してから、イオン注入により、ソース・ドレイン用のn+型半導体領域11aおよびp+型半導体領域11bを形成して、nチャネル型MISFETおよびpチャネル型MISFETが形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体装置、半導体装置の製造方法、静電放電保護素子

【課題】製造効率を向上すると共に、内部回路の保護を的確に行うことが容易に可能な半導体装置、半導体装置の製造方法、静電放電保護素子を提供する。

【解決手段】半導体基板20に第1導電型の第1半導体領域21が形成され、その両側に第2導電型の第2及び第3半導体領域(22,23)が形成され、第1半導体領域の上方に絶縁膜を介してゲート電極32が形成され、第1半導体領域と第3半導体領域の接合面をまたいでそれらにかかるように第1導電型の第4半導体領域30が形成され、第2及び第3半導体領域にソース領域26とドレイン領域28が形成され、ゲート電極及びソース領域が接地され、内部回路に接続された入力パッド40がドレイン領域に接続され、入力パッドにサージ電圧が入力された際にドレイン領域と第4半導体領域との間でツェナー降伏が生じて寄生バイポーラトランジスタがオン状態となり、サージ電圧を放電する。

(もっと読む)

半導体装置及びその製造方法

【課題】強い圧縮応力を有するシリコン窒化膜を用いたpMISFETを有する半導体装置及びその製造方法において、歩留まりが高く且つスイッチングスピードが高い半導体装置及びその製造方法を提供する。

【解決手段】ボックスマーク102内においてシリコン基板1を覆うようにシリコン酸化膜14を形成する。次に、基板上の半導体領域にシリサイド化反応によりニッケルシリサイド8を形成する。その後、強い圧縮応力を有するシリコン窒化膜9をpMISFET101及びボックスマーク102を覆うように形成する。その上に層間絶縁膜11を形成した後レジストをパターニングしてコンタクトホール13を形成する。この際、重ね合わせ精度が所定の規格を満たすまで、レジストを一旦除去し再度レジスト12bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御でき、短チャネル効果を効果的に抑制できる半導体装置を提供する。

【解決手段】シリコン基板1と接してショットキー接合を形成するソース領域10,ドレイン領域11と、上記シリコン基板1とソース領域10との境界が露出する部分およびシリコン基板1とドレイン領域11との境界が露出する部分を被覆するように設けられた絶縁層を備える。上記絶縁層は、シリコン基板1とソース領域10との境界およびシリコン基板1とドレイン領域11との境界を跨ぐように、シリコン基板1とソース領域10に接すると共にシリコン基板1とドレイン領域11に接する固定電荷を含む領域8を有する。上記固定電荷は、熱平衡状態において荷電している。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

ファセットされたシリサイドコンタクトを有する半導体デバイス及び関連する製造方法

【解決手段】

開示される主題は、半導体トランジスタデバイス及び、従来のシリサイドコンタクトと比較して増大された実効サイズを有するシリサイドコンタクトを形成するために利用することができる関連する製造技術に関する。ここに開示されるプロセスに従って製造される半導体デバイス(200)は、半導体材質(102)の層と、半導体材質(102)の層を覆うゲート構造(112,128)とを含む。チャネル領域(218)が半導体材質(102)の層内に形成され、チャネル領域(218)はゲート構造(112,128)の下層となる。半導体デバイス(200)はまた、半導体材質(102)の層内のソース及びドレイン領域(216)を含み、チャネル領域(218)はソース及びドレイン領域(216)の間に配置される。また、半導体デバイス(200)はソース及びドレイン領域(216)を覆うファセット形状シリサイドコンタクト区域(210,308,406)を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造工程においてストレッサー膜などから発生する水素によるp型MOSトランジスタの駆動力低下を防止する。

【解決手段】半導体装置は、n型活性領域13B上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16Bと、ゲート絶縁膜15及びゲート電極16Bの側面に形成された内側サイドウォール17及び外側サイドウォール20Bと、p型ソースドレイン領域21Bと、内側サイドウォール17の側面及び外側サイドウォール20Bの側面における少なくとも底部に形成され、水素に対してバリア性を有する絶縁性の水素バリア膜23とを備える。

(もっと読む)

半導体装置と、電子部品及び半導体装置の製造方法

【課題】オン電流の低下を抑制しつつ、閾値電圧を高くすることを可能とした半導体装置と、電子部品及び半導体装置の製造方法を提供する。

【解決手段】半導体基板1に形成されたHVトランジスタ10を備え、HVトランジスタ10は、半導体基板1上に絶縁膜を介して形成されたゲート電極19と、ソース15及びドレイン13を有し、ゲート電極19の内部は、当該ゲート電極19に電圧が印加されてソース15とドレイン13との間に電流が流れるときに空乏化する。このような構成であれば、空乏化によりゲート電極19に容量が生じ、この容量はゲート絶縁膜の容量と直列に接続される。これにより、ゲート絶縁膜の容量が実質的に低下するため、HVトランジスタ10の閾値電圧を高くすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】Hf及びZrの少なくともいずれかを含むゲート絶縁膜の膜質を安定させることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、半導体層と、半導体層の上に設けられ、Hf及びZrの少なくともいずれかを含むゲート絶縁膜と、ゲート絶縁膜の上に設けられ、Hf及びZrの少なくともいずれかを含む炭窒化物を含むゲート電極と、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】パンチスルーの発生を抑制すると共に、ソース、ドレインの寄生容量を低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】凹部13が形成された半導体基板1と、凹部13の底面上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成されたゲート電極5と、ゲート電極5とその直下6とを含む領域の両側の半導体基板1にそれぞれ形成された第1導電型のS/D層7と、半導体基板1に形成された第2導電型のハロー層9と、を備え、S/D層7は、凹部13の直下の領域に形成された低濃度の第1不純物層7aと、凹部13の側面に隣接する領域に形成された高濃度の第2不純物層7bと、を有し、ハロー層9は、第1不純物層7aの直下の領域に形成され、且つ第2不純物層7bの直下の領域には形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中のシリコン混晶層の形成を制御することにより、キャップ膜の形成を不要とし、シリサイド層を精度良く形成する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第2導電型のポリシリコン膜28Aとポリシリコン膜28A上に形成された炭素を含む第1のシリコン混晶層25とを有するゲート電極25Aと、第1のシリコン混晶層25上に形成された第1のシリサイド層29と、半導体領域10xにおけるゲート電極25Aの側方下の領域に形成された第2導電型の不純物拡散領域24と、不純物拡散領域24の上部領域に形成された炭素を含む第2のシリコン混晶層26と、第2のシリコン混晶層26上に形成された第2のシリサイド層30とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】生産性を損なうことなく、MISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1の主面s1のNMIS領域RNには素子用pウェルpwを、PMIS領域RPには素子用nウェルnwを形成した後、主面s1に順に形成したゲート絶縁膜GIおよび第1多結晶シリコン膜E1aを透過させるようにしてアクセプタとなる不純物イオンを注入して、チャネル領域CHの不純物濃度を調整する。その後、第1多結晶シリコン膜E1aおよびその上に形成した第2多結晶シリコン膜のうち、NMIS領域RNにはドナー不純物を、PMIS領域RPにはアクセプタ不純物を注入した後、これらを加工して、n型のゲート電極とp型のゲート電極とを形成する。ゲート絶縁膜GIは、シリコン基板1の主面を酸化した後、炉体内において一酸化二窒素雰囲気中で熱処理を施すようにして形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル移動度の低下を防止して、パンチスルーストッパを形成する。

【解決手段】半導体基板100と、前記半導体基板上に形成され、長手方向と短手方向とを有し、順に積層されたボロンを含むシリコン炭化膜とシリコン膜とを有する半導体層110と、少なくとも前記半導体層の前記短手方向の側面に形成されたゲート電極150と、前記半導体層に形成され、前記ゲート電極の前記長手方向に隣接して形成されたソース・ドレイン領域111、112と、前記半導体層の側面であって、前記ゲート電極と前記半導体基板との間に形成された素子分離絶縁膜130と、を備える。

(もっと読む)

半導体装置

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になる第1の導電層6の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体装置

【課題】半導体装置における耐圧性能を向上させる。

【解決手段】半導体装置100は、エピタキシャル層3と、エピタキシャル層3に形成されたチャネル領域を含むボディ層4と、ボディ層4と重畳するようにして形成されたソース層6と、ソース層6を囲んでエピタキシャル層3上に形成された環状のゲート絶縁膜10と、ゲート絶縁膜10を介して形成されたゲート電極12と、ボディ層4を囲んでエピタキシャル層3に環状に形成されたドリフト層14と、ソース層6と対向してエピタキシャル層3表面に形成されたドレイン層と、を備える。ボディ層4は、ゲート幅方向端部においてその境界面がゲート絶縁膜10の下面に接するように設けられている。また、ゲート絶縁膜10は、ゲート幅方向端部におけるボディ層4の境界面と接する少なくとも一部に、ゲート長方向のチャネル領域上部よりも膜厚が厚い厚膜部24を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】側面方位とキャリア極性に応じて歪み方向が最適化されたFinFETおよびナノワイヤトランジスタと、これを実現するSMTを導入した製造方法を提供する。

【解決手段】半導体基板14と、半導体基板14の上部に形成され、半導体基板14主面に平行な上面と、半導体基板14主面に垂直な(100)面の側面を有する直方体状半導体層40と、直方体状半導体層40内に形成されるチャネル領域18と、チャネル領域18の少なくとも側面上に形成されるゲート絶縁膜20と、ゲート絶縁膜20上のゲート電極30と、直方体状半導体層40内に、チャネル領域18を挟み込むよう形成されるソース/ドレイン領域とを備え、チャネル領域18に、半導体基板14主面に対して垂直方向の圧縮歪みが印加されているpMISFETを有することを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率ゲート絶縁膜/多結晶シリコン界面におけるダイマーの発生を既存の製造工程になじみやすい工程により抑制して、フェルミレベルピンニングを除去する。

【解決手段】 半導体基板上方に形成されたHf、Zr或いはAlの少なくとも一つと酸素とを含むゲート絶縁膜とシリコンを含むゲート電極との間に、炭素を含むキャップ層を設ける。

(もっと読む)

41 - 60 / 191

[ Back to top ]