Fターム[5F140BK13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域の形成 (4,176) | 不純物の導入 (3,397) | イオン注入 (3,132)

Fターム[5F140BK13]の下位に属するFターム

斜めイオン注入、回転イオン注入 (261)

Fターム[5F140BK13]に分類される特許

2,861 - 2,871 / 2,871

バンド設計超格子を有する半導体装置

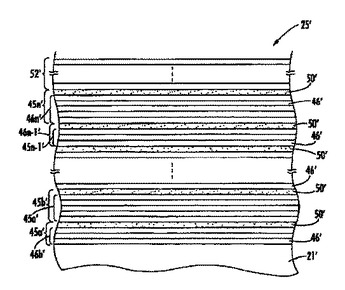

半導体装置は、複数の積層された層群を有する超格子を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

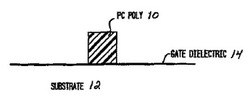

SiC基板1と、SiC基板1表面に形成されたソース3a及びドレイン3bと、SiC表面に接して形成され厚さが1分子層以上のAlN層5と、その上に形成されたSiO2層とを有する絶縁構造と、この絶縁構造上に形成されたゲート電極15とを有しており、SiCとの間の界面状態を良好に保ちつつ、リーク電流を抑制することができる。 (もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

半導体デバイス並びに量子井戸構造体を製造する方法及び量子井戸構造体を有する半導体デバイス

量子井戸構造体(4)を備える多重層構造体(3)を基板(2)上に得るための半導体デバイス(1)及び方法が開示されている。量子井戸構造体(4)は、絶縁物質(6、6’)によって挟まれる半導体層(5)を有し、絶縁物質(6、6’)の物質は好ましくは、高誘電率を有する。FETにおいて、量子井戸(4、9)はチャネルとして機能し、より高い駆動電流及びより低いオフ電流が可能になる。短チャネル効果が低減される。多重チャネルFETは、サブ35nmゲート長に対してさえも動作するのに適している。本方法において、量子井戸は、好ましくはMBEを用いて、半導体物質及び高誘電率物質のエピタキシャル成長によって互いの上に交互に形成される。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

Si(100)基板の表面にシリコン酸化膜を形成した後、このシリコン酸化膜をプラズマ窒化して酸窒化シリコン膜にする。その後NOガス雰囲気中で770乃至970℃の温度条件下で熱処理することにより、ゲート絶縁膜における基板との界面部分の窒素濃度を1乃至10原子%にすると共に、基板と酸窒化シリコン膜との界面に存在する界面Si結合欠陥の結合手の方位角分布が、基板の[100]方位に対して25°以上の角度にピークをもつようにする。 (もっと読む)

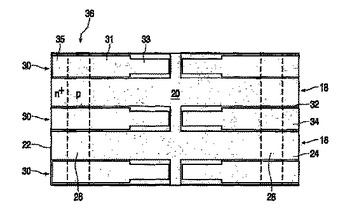

絶縁トレンチゲート電極を有する横型電界効果トランジスタ

縦方向、横方向に交互に配置されたソース領域(22)、ソースボディ領域(26)、ドリフト領域(20)、ドレインボディ領域(28)、およびドレイン領域(24)をそれぞれ有するセル(18)を、減表面電界を達成するための構造とともに有する、電界効果トランジスタである。実施形態における構造は、ソースまたはドレイン領域(22、24)近傍にゲート領域(31)を定義する縦方向に離間された絶縁ゲートトレンチ(35)と、ドリフト領域(20)近傍に縦方向に延在する電位プレート領域(33)と、を含むことができる。代替的に、別個の電位プレート領域(33)または縦方向に延在する半絶縁フィールドプレート(50)をドリフト領域(20)近傍に設けてもよい。このトランジスタは、双方向切り替えに適している。  (もっと読む)

(もっと読む)

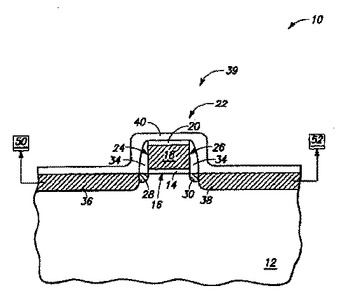

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

2,861 - 2,871 / 2,871

[ Back to top ]