Fターム[5F140CC09]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741) | SiON (77)

Fターム[5F140CC09]に分類される特許

61 - 77 / 77

応力が加えられたゲート金属シリサイド層を含む高性能MOSFET及びその製造方法

【課題】 応力が加えられたゲート金属シリサイド層を含む高性能の金属酸化物半導体電界効果トランジスタ(MOSFET)及び高性能MOSFETを製造する方法を提供すること。

【解決手段】 本発明は、ソース領域、ドレイン領域、チャネル領域、ゲート誘電体層、ゲート電極及び1つ又は複数のゲート側壁スペーサを備えた少なくとも1つの電界効果トランジスタ(FET)を含む半導体デバイスに関する。このようなFETのゲート電極は、1つ又は複数のゲート側壁スペーサによって横方向に制限され、かつ、FETのチャネル領域内に応力を生じさせるように配置され構成される内因性応力が加えられたゲート金属シリサイド層を含む。半導体デバイスは、少なくとも1つのp−FETを含むことが好ましく、p−チャネルFETは、1つ又は複数のゲート側壁スペーサによって横方向に制限され、かつ、FETのp−チャネル内に圧縮応力を生じさせるように配置され構成される内因性応力が加えられたゲート金属シリサイド層を備えたゲート電極を有することがより好ましい。

(もっと読む)

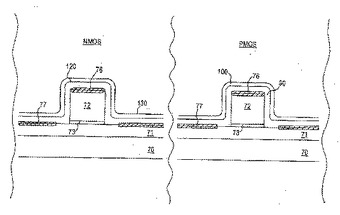

コンタクト絶縁層および異なる特性を有するシリサイド領域を形成するための技法

NチャネルトランジスタおよびPチャネルトランジスタのための金属シリサイドを別個に形成できるようにする技法が提供され、同時に、トランジスタタイプ毎に歪み誘発機構も別個に設けられる。このようにして、NMOSトランジスタ(120、220)のチャネル領域まで短い距離を有するコバルトシリサイド(130、230)を設けることができ、その一方で、Pチャネルトランジスタ(140、240)は、Nチャネルトランジスタ(120、220)の特性に過度に影響を及ぼすか、またはその特性を劣化させることなく、高導電性のニッケルシリサイド(150、250)を収容することができる。  (もっと読む)

(もっと読む)

高電圧半導体装置及びその製造方法

【課題】高電圧半導体装置及びその製造方法が開示される。

【解決手段】高電圧半導体装置及びその製造方法において、第1深さを有する複数のドリフト領域は、半導体基板に第1不純物をドーピングして、それぞれ互いに離隔してチャンネル領域を限定するように形成される。第1深さに対して浅い第2深さを有するソース/ドレイン領域は、ドリフト領域に第2不純物をドーピングして形成される。第1深さに対して浅い第3深さを有する不純物蓄積領域は、ソース/ドレイン領域と隣接するドリフト領域に第3不純物をドーピングして形成される。ソース/ドレイン領域を部分的に露出させるゲート絶縁膜パターン及びチャンネル領域のゲート絶縁膜パターン上にゲート導電膜パターンが形成される。ゲート絶縁膜パターン及びゲート導電膜パターン上に急激に電流が増加することを顕著に減少させるバッファ膜が形成される。

(もっと読む)

半導体装置、および半導体装置の作製方法

【課題】フッ素原子を分子中に含むガスでは、SiN膜のエッチングが等方的に進行するため、サイドウォールの幅が小さくなり、LDD領域の幅を大きくすることが困難であった。

【解決手段】ゲート電極上に窒化珪素膜を形成し、エッチングガスとして臭化水素ガスを主に用い、ICP(誘導結合型プラズマ)法などのエッチング方法により、窒化珪素膜のうちゲート電極上の部分と基板表面部のみを除去し、同時にゲート電極の側面部のみに窒化珪素膜を残す。

(もっと読む)

半導体装置およびその製造方法

【課題】大きなディボットやコンタクト接続不良の発生を回避しつ半導体基板にストレスをかけることにより、キャリアの移動度を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上に、ゲート絶縁膜3を介してゲート電極4が形成されている。ゲート電極4の両側における半導体基板1には、ソース・ドレイン領域8が形成されている。素子分離用溝2の内壁から、ソース・ドレイン領域8上およびゲート電極4上まで連続してライナー膜11が形成されている。ひとつなぎにしたライナー膜11により、半導体基板1にストレスをかけて、キャリアの移動度を向上させる。ライナー膜11は、コンタクト13の形成のためのエッチングストッパとしての役割ももつ。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果によるリーク電流の低減に優れた半導体装置およびその製造方法を提供する。

【解決手段】単結晶半導体基板上に形成された電界効果トランジスタの作成過程において、エクステンション領域を形成するために不純物を導入するとともに、単結晶格子を崩してアモルファス化させる。または、不純物および原子量の大きい元素を導入することによって、単結晶格子を崩してアモルファス化させる。そして、パルス幅が1fs以上10ps以下、かつ波長が370nm以上640nm以下のレーザビームを照射することにより、アモルファス化した部分のみを選択的に活性化させ、エクステンション領域を20nm以下の厚さで形成する。

(もっと読む)

半導体装置の作製方法

【課題】材料の利用効率を向上させ、作製工程を簡略化した半導体装置の作製技術を提供することを目的とする。また、それらの半導体装置を構成する配線等のパターンを、所望の形状で密着性よく形成できる技術を提供することも目的とする。

【解決手段】第1の導電層上に第1の絶縁層を形成し、第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層上に第1の開口を有する第1のマスク層を形成し、第1の絶縁層及び第2の絶縁層をエッチングすることにより、第1の導電層に達する第1の開口部を形成し、第1のマスク層除去後、第1の開口よりも開口面積が広い第2の開口を有し、且つ、導電性材料を含む組成物に対してぬれ性の低い第2のマスク層を第2の絶縁層上に形成し、第1の絶縁層上面の一部が露出するように第2の絶縁層をエッチングし、第2の開口部を形成し、第1の開口部及び第2の開口部に導電性材料を含む組成物を充填し、第2の導電層を形成する。

(もっと読む)

高移動度シリコンチャネルを有する縦型MISFET半導体装置

半導体基板上の絶縁層より突出した箱形半導体領域の少なくとも側面をチャネル領域として用いる縦型MIS型電界効果トランジスタのチャネル領域に、熱膨張係数差による引張り歪みの導入、または格子緩和シリコン・ゲルマニウムの表面にシリコン膜を形成することで、引っ張り応力を印加し、チャネル領域の移動度を向上させる。  (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】 RTAによるアニール法は、微細化に限界がある。RTAによるアニール法は、加熱時間が数秒で、半導体基板全体が高温に加熱されるために不純物が半導体基板の深部へ拡散する恐れがあるため、今後のさらなる微細化に対応することが困難である。

【解決手段】レーザ光を非線形光学素子に通すことなく基本波のままとし、高強度、且つ、繰り返し周波数の高いパルスのレーザ光を不純物拡散層に照射してレーザアニールを行って不純物を電気的に活性化させることを特徴とする。本発明により、シリコン基板表面の薄い層を局所的に溶かして活性化することができる。また、一度のレーザ走査で活性化される領域の幅を拡大することができるため、格段に生産性を向上させることができる。

(もっと読む)

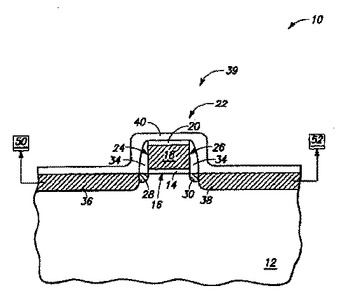

半導体デバイスおよび半導体デバイスの製造方法

【課題】 後続するコンタクト・ホール工程で使用される層間絶縁(ILD)エッチング停止層を有する高電圧用トランジスタ・デバイスを提供する。

【解決手段】 エッチング停止層は、10Ω−cmより大きい抵抗を有する高抵抗膜である。この結果、ゲート部において5Vより大きい高電圧を駆動する場合のリークを防止し、破壊電圧は向上する。高電圧用デバイスの製造方法は、現在の低電圧デバイスの製造工程と中電圧デバイスの製造工程と混載可能である。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

チャネルキャリア移動度向上のための高応力ライナーを備えたSi−Geに基づく半導体デバイス

応力ライナーを用いることで、Si−Geデバイスのトランジスタのチャネル領域のキャリア移動度が増加される。一実施形態においては、緩和ソース/ドレイン領域を覆う高圧縮膜あるいは高引っ張り応力膜を適用する。他の実施形態としては、ポストシリサイドスペーサを除去した後、P−チャネルトランジスタあるいはN−チャネルトランジスタのゲート電極(72)および歪みソース/ドレイン領域(71)にそれぞれ、高圧縮応力膜(90)あるいは高引っ張り応力膜(120)を適用する。  (もっと読む)

(もっと読む)

pFET中のボロン拡散係数の減少方法

半導体材料の構造物または本体(例えば基板または層)によって定められる境界を横切って加えられる応力を受ける膜は、境界の近傍の半導体材料中に引張り応力から圧縮応力への変化を提供し、アニーリングの間のホウ素拡散速度を変化させ、ひいては最終ホウ素濃度またはプロフィル/勾配あるいはその両方を変化させるために用いられる。電界効果トランジスターの場合、側壁の有無にかかわらず、ソース/ドレイン、拡張注入部またはハロ注入部、あるいはその両方に対する境界の位置を調節するために、ゲート構造物を形成させることができる。水平方向と垂直方向とで異なるホウ素拡散速度を作り出すことができ、ヒ素と同程度の拡散速度を実現することができる。同じプロセス工程で、nFETとpFETとの両方の接合キャパシタンスの減少を同時に実現することができる。

(もっと読む)

(もっと読む)

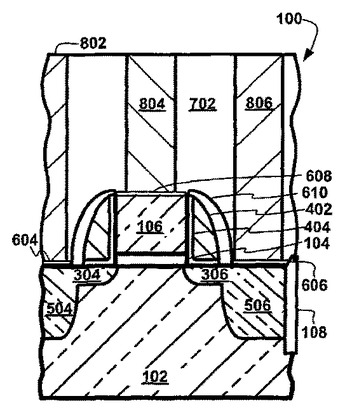

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

61 - 77 / 77

[ Back to top ]