Fターム[5F140CC09]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741) | SiON (77)

Fターム[5F140CC09]に分類される特許

21 - 40 / 77

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン・ゲート電極作成のためのエッチング処理時に、クランプによって覆われていたポリサイド層上の層間絶縁膜の膜剥がれが起こりにくい半導体装置の製造方法を提供する。

【解決手段】半導体基板110上に、ポリシリコン膜220及びタングステン・シリサイド膜210をこの順に積層してポリサイド・ゲート電極230を形成する。ポリサイド・ゲート電極230を含む半導体基板110上に、B濃度が高濃度の下層BPSG膜140を第1の成膜速度v1で形成する。下層BPSG膜140の上に、B濃度が下層BPSG膜140より低い低濃度の上層BPSG膜120を第2の成膜速度v2で形成する。第2の成膜速度は前記第1の成膜速度未満である。

(もっと読む)

半導体装置の製造方法

【課題】短いゲート長を加工可能にする半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法の一形態は、シリコン基板2上にシリコン酸化膜34を形成し、酸化膜34上に所定幅T1を有する多結晶シリコン膜35aを形成し、少なくとも多結晶シリコン膜35aの両側部を酸化し、所定幅T1よりも狭い幅を有する酸化膜34の部分を多結晶シリコン膜35aの下に残すように、酸化膜34を、多結晶シリコン膜35aの酸化された部分と共にエッチングし、酸化された部分がエッチングされた多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入し、多結晶シリコン膜35aの両側に側壁絶縁膜14を形成し、側壁絶縁膜14が形成された多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入する、工程を有する。

(もっと読む)

ゲート・ダイオード構造及びゲート・ダイオード構造の製造方法

【課題】改善された特性と強化された機能とを備えたダイオード構造とその製造方法が望まれている。

【解決手段】ゲート・ダイオード構造及びSOI基板(SOI)等の上にゲート・ダイオード構造を製造する方法であって、緩和下地層(34‘)を用いる。緩和下地層は歪下地層(34)から形成される。歪下地層(34)は典型的にはゲート・ダイオード構造と同時に形成される電界効果型トランジスタに用いられる。緩和下地層は歪下地層(34)のイオン注入処理のような処理により形成される。反応性イオンエッチング方法を用いてゲート・ダイオード構造から歪下地層を除去するときのゲート・ダイオードの損傷がないので、歪下地層に比較して、緩和下地層はゲート・ダイオード構造の理想値を改善する。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する、シリサイド化される金属を含有する複数の電気素子要素と、複数の電気素子要素を覆い、電気素子要素に含まれる金属が実質的にシリサイド化しない温度で薄膜形成したシリコンを含む保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、保護絶縁膜は、シリコンおよび窒素を含有できる。保護絶縁膜は、260℃以下の温度で薄膜形成した窒化シリコン膜であってよく、好ましくは100℃以下の温度で薄膜形成した窒化シリコン膜である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

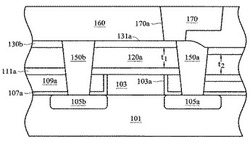

半導体装置及び半導体装置の製造方法

【課題】コンタクトプラグとゲート電極との間のショートおよび/またはコンタクトプラグとシリコンピラーとの間のショートを防止した半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】基板1上に立設された第一のシリコンピラー2と、その側面を覆う絶縁膜5と、絶縁膜5を覆うとともに、その先端部6aが第一のシリコンピラー2の先端部2aよりも基板1よりに位置してなるゲート電極6と、からなる縦型Tr部101と、基板1上に立設された第二のシリコンピラー2’と、その側面を覆う絶縁膜5’と、絶縁膜5’を覆うとともに、その先端部6’aが第二のシリコンピラー2’の先端部2’aよりも基板1から離れた側に位置してなり、ゲート電極6に接続されてなるゲートコンタクト電極6’と、からなるゲートコンタクト部102と、を有する半導体装置111を用いることにより、上記課題を解決できる。

(もっと読む)

前駆体造成物、薄膜形成方法、これを利用したゲート構造物の製造方法、及びキャパシタの製造方法

【課題】 前駆体造成物、薄膜形成方法、これを利用したゲート構造物の製造方法、及びキャパシタの製造方法を提供する。

【解決手段】 半導体装置の製造に利用されることができる薄膜形成用造成物、薄膜形成方法、ゲート構造物の製造方法、及びキャパシタの製造方法において、薄膜造成方法は、前駆体と電子供与化合物を接触させて安定化された前駆体を基板上に提供した後(S20)、前駆体と結合を形成できる反応物質を基板上に導入して、薄膜を形成する(S30)。電子供与化合物によって安定化された前駆体は、熱的安定性が優秀で、ステップカバレッジが優秀な薄膜を形成することができる。半導体製造工程の安全性、効率性及び信頼性を向上させることができる。

(もっと読む)

半導体装置及び電子機器

【課題】面積を増大させることなく、過電圧に対する耐性を高めることを課題の一つとする。

【解決手段】第1の端子部100に設けられ、第1のn型不純物領域106と、平面視において前記第1のn型不純物領域106の内周部に設けられた第1の抵抗領域107と、平面視において前記第1の抵抗領域107の内周部に設けられた第1のp型不純物領域108と、を有する第1の半導体領域103と、前記第2の端子部101に設けられ、第2のp型不純物領域109と、平面視において前記第2のp型不純物領域109の内周部に設けられた第2の抵抗領域110と、前記第2の抵抗領域110の内周部に設けられた第2のn型不純物領域111と、を有する第2の半導体領域104と、有する構成である。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート誘電膜を用いるpチャネルFETをゲート先作りプロセスにより形成すると閾値が大きくなる。

【解決手段】High-Kゲート誘電膜104の側面と接触するようにHigh-K誘電膜102を形成した後、酸素雰囲気中でアニールする。

(もっと読む)

導電性コンタクトの組み込みのための構造体及びプロセス

【課題】 キーホール・シームの形成を排除した信頼性が高い高アスペクト比のコンタクト構造体を含む半導体構造を提供する。

【解決手段】 キーホール・シームの形成は、本発明においては、誘電体材料内部に存在する高アスペクト比のコンタクト開口部内に高密度化貴金属含有ライナを設けることによって排除される。高密度化貴金属含有ライナは拡散バリアの上に配置され、これら両方の要素は、本発明のコンタクト構造体の導電性材料を、下層の半導体構造体の導電性材料から分離する。本発明の高密度化貴金属含有ライナは、第1の抵抗率を有する貴金属含有材料の堆積、及び、堆積した貴金属含有材料の抵抗率をより低い抵抗率に減少させる高密度化処理プロセス(熱又はプラズマ)を、堆積した貴金属含有材料に施すことによって形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】素子形成領域間の分離絶縁膜を保護し、接合リークなしに素子と配線膜とを電気的に接続することができる半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板1に形成されて素子形成領域2を画定する分離絶縁膜3と、素子形成領域2に形成された素子と、素子および分離絶縁膜3を覆うように半導体基板1上に形成された層間絶縁膜5と、層間絶縁膜5をエッチングして形成されたコンタクトホール内に埋め込まれて素子と電気的に接続する配線膜6、7とを備え、少なくとも分離絶縁膜3と層間絶縁膜5との間に、前記エッチングによる分離絶縁膜3の浸食を防止するための3層以上の絶縁膜4a、4b、4cが積層されてなる保護積層膜4が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体デバイスを形成する方法

【課題】 ボイドフリーかつシームフリーの金属ゲート導体層が比較的薄い高kゲート誘電体層の上に位置決めされている少なくとも1つの高アスペクト比ゲート構造を有する相補型金属酸化膜半導体(CMOS)デバイスを形成する方法を提供する。

【解決手段】 これらの方法実施形態は、高アスペクト比ゲート・スタック開口部を下から上に金属ゲート導体層で充填するために電気メッキ・プロセスを使用するゲート交換戦略を取り入れている。電気メッキ・プロセス用の電子の発生源は、基板の裏面を直接通過する電流である。これは、シード層の必要性を排除し、ボイドまたはシームなしで金属ゲート導体層が形成されることを保証するものである。さらに、実施形態次第で、電気メッキ・プロセスは、所与の領域への電子流を増強するために(すなわち、メッキを増強するために)照明を受けて実行され、所与の領域への電子流を防止するために(すなわち、メッキを防止するために)暗闇で実行される。

(もっと読む)

少なくとも1つの誘電体層を形成するための方法およびシステム

【課題】エッチングされた所望のアスペクト比の提供。

【解決手段】構造を形成するための方法が、基板の表面にわたって少なくとも1つの特徴部を形成するステップを含む。少なくとも1つの特徴部の上には窒素含有誘電体層を形成する。少なくとも1つの特徴部の少なくとも1つの側壁上の窒素含有層の第1の部分を、第1の速度で取り除き、少なくとも1つの特徴部の底部領域に隣接する基板の上の窒素含有層の第2の部分を、第2の速度で取り除く。第1の速度は第2の速度よりも大きい。窒素含有誘電体層の上に誘電体層を形成する。

(もっと読む)

接点抵抗が改善された半導体構造およびその製造方法(接点抵抗が改善された半導体構造)

【課題】 構造の接点抵抗を改善した、すなわち低下させた半導体構造を提供する。

【解決手段】 自己組織化・ポリマー技術を用いて、半導体構造の導電性コンタクト領域に存在する材料内に少なくとも1つの配列されたナノサイズ・パターンを形成する。配列されたナノサイズ・パターンを有する材料は、相互接続構造または電界効果トランジスタの半導体ソースおよびドレイン領域の導電材料である。接点領域内に整列ナノサイズ・パターニング材料が存在することによって、以降の接点形成のための全領域(すなわち界面領域)が拡大し、これによって構造の接点抵抗が低下する。接点抵抗の低下により、構造を通る電流が改善する。上述のことに加えて、本発明の方法および構造では、接合領域が不変のままであるので、構造の接合容量は影響を受けない。

(もっと読む)

電界効果型トランジスタの修復方法、半導体装置の修復方法、半導体装置の作製方法、及び半導体装置

【課題】電界効果型トランジスタのリーク電流を低減し、寿命の向上を図るための簡便な修復方法を提供することを課題とする。また、作製コストの増加を抑え、消費電力が小さく、且つ信頼性の高い半導体装置を提供することを課題とする。

【解決手段】ソース電極又はドレイン電極の一方と、ゲート電極との間に、電気的な衝撃を加える。または、ソース電極又はドレイン電極の一方と、ソース電極又はドレイン電極の他方との間に、電気的な衝撃を加える。これにより、リークパスを絶縁化し、リーク電流を低減することができる。なお、上記の電気的な衝撃は、静電気等の電気パルスであっても良いし、直流電圧、交流電圧、直流電流、交流電流等であっても良い。

(もっと読む)

半導体装置

【課題】従来と異なる方法によりチャネル領域に歪みを発生させたMISFET構造を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成された第1のソース・ドレイン領域および第1のチャネル領域を有するn型MISFETと、前記半導体基板上に形成された第2のソース・ドレイン領域および第2のチャネル領域を有するp型MISFETと、前記第1のソース・ドレイン領域に接続され、前記第1のチャネル領域に伸張歪みを与える第1のコンタクトプラグと、前記第2のソース・ドレイン領域に接続され、前記第2のチャネル領域に圧縮歪みを与える第2のコンタクトプラグと、を有する。

(もっと読む)

21 - 40 / 77

[ Back to top ]