Fターム[5F140CE02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | リフトオフ (193)

Fターム[5F140CE02]に分類される特許

121 - 140 / 193

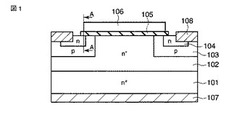

炭化珪素半導体装置

【課題】ゲート絶縁膜の信頼性が向上した炭化珪素半導体装置を提供する。

【解決手段】第1と第2の主面を有する炭化珪素基板(101)と、炭化珪素基板の第1の主面に設けられた第1導電型の炭化珪素層(102)と、炭化珪素層の表面に設けられた第2導電型の第1の炭化珪素領域(103)と、第1の炭化珪素領域内の表面に設けられた第1導電型の第2の炭化珪素領域(104)と、炭化珪素層、第1の炭化珪素領域、及び第2の炭化珪素領域が連続して連なる部分に跨るように選択的に設けられたゲート絶縁膜(105)と、ゲート絶縁膜上に形成されたゲート電極(106)と、第2及び第1の炭化珪素領域の隣接する部分に選択的に設けられたトレンチに埋め込まれた第1の電極(108)と、炭化珪素基板の前記第2の主面に形成された第2の電極(107)とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極下端の側面に接する領域に半導体表面が露出することを防止することが可能な半導体装置を提供する。

【解決手段】 半導体基板(20)の上に、電子走行層(21)と電子供給層(23)とが配置されている。電子供給層の上に、ソース電極(30F)及びドレイン電極(31F)が、相互に間隔を隔てて配置されている。ソース電極とドレイン電極との間の電子供給層の上に、ゲート電極(40F)が配置されている。電子供給層の上に、ソース電極とゲート電極との間の領域、及びドレイン電極とゲート電極との間の領域を覆う保護膜(35)が形成されている。ゲート横開口(38)が保護膜に形成されている。ゲート横開口は、ソース電極とゲート電極との間の領域、及びドレイン電極とゲート電極との間の領域の少なくとも一方に、ゲート電極、ソース電極、及びドレイン電極のいずれからも間隔を隔てて配置されている。

(もっと読む)

GaN系電界効果トランジスタ

【課題】簡易な製造工程によって形成可能なノーマリーオフ型のGaN系FETを提供すること。

【解決手段】本発明においては、ソース電極S直下およびドレイン電極D直下にそれぞれn−AlGaN層16を形成し、さらにn−AlGaN層16の間に位置するチャネル層であるp−GaN層14上に形成される絶縁膜17の上にゲート電極Gを形成することによって、ソース電極Sおよびドレイン電極Dとn−AlGaN層16との接触抵抗を低下させたノーマリーオフ型のGaN系のFET1を実現することができる。

(もっと読む)

炭化ケイ素半導体装置およびその製造方法

【課題】炭化ケイ素からなる基板上に欠陥密度の低減された活性層が形成された炭化ケイ素半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、面方位{0001}に対しオフ角が50°以上65°以下である、炭化ケイ素からなる基板2と、バッファ層21と、活性層(エピタキシャル層3、p型層4、およびn+領域5、6)とを備える。バッファ層21は、基板2上に形成され、炭化ケイ素からなる。活性層は、バッファ層21上に形成され、炭化ケイ素からなる。活性層におけるマイクロパイプ密度は基板2におけるマイクロパイプ密度より低い。また、活性層における、バーガーズベクトルの向きが[0001]である転位の密度は、基板2における当該転位の密度より高い。

(もっと読む)

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、デバイス特性及び信頼性を向上させる。

【解決手段】半導体装置を、半導体基板6上に形成された化合物半導体積層構造1と、少なくとも化合物半導体積層構造1の表面に露出している部分を覆う第1絶縁膜4と、第1絶縁膜4上に形成された第2絶縁膜5とを備えるものとし、第2絶縁膜5を第1絶縁膜4よりも水素を多く含むものとする。

(もっと読む)

ダイヤモンド電界効果トランジスタ

【課題】最大ドレイン電流密度が高く、長時間の電力動作にも耐える信頼性の高い、実用的なダイヤモンド電界効果トランジスタを提供すること。

【解決手段】p型またはn型の伝導性を有するダイヤモンド結晶層1をCVD装置などで成長させる。次に、金を蒸着させ、ソース電極2、ドレイン電極3を形成する。次に、76Torrに減圧したCVDチャンバ内で、上記ダイヤモンド結晶層1に、酸素ガス、水素ガス、トリメチルアルミニウムを供給し、ソース電極2とドレイン電極3との間のゲート部に厚さ8nmのAl(OH)3またはAl1-x-yOxHy化合物からなる絶縁層4を形成する。最後に、絶縁層4上にAl金属膜6を蒸着させてゲート部を形成する。

(もっと読む)

炭化ケイ素半導体装置およびその製造方法

【課題】チャネル移動度のような電気的特性の優れた炭化ケイ素半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、面方位{0001}に対しオフ角が50°以上65°以下である、炭化ケイ素からなる基板2と、半導体層(図1のp型層4)と絶縁膜(図1の酸化膜8)とを備える。半導体層(p型層4)は基板2上に形成され、炭化ケイ素からなる。絶縁膜(酸化膜8)は、半導体層(p型層4)の表面に接触するように形成されている。半導体層と絶縁膜との界面(チャネル領域と酸化膜8との界面)から10nm以内の領域における窒素原子濃度の最大値が1×1021cm-3以上である。

(もっと読む)

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率膜をゲート絶縁膜として用い、pチャネル型MISFETおよびnチャネル型MISFETのそれぞれに要求されるしきい値電圧を容易に実現できる相補型MISFETおよびその製造技術を提供する。

【解決手段】n型ウエル3およびp型ウエル4のそれぞれの表面に清浄な酸化シリコン膜5を形成した後、酸化シリコン膜5上に2A族元素の酸化物、3A族元素の酸化物、3B族元素の酸化物、4A族元素の酸化物、および5A族元素の酸化物等からなる酸素欠損調整層6と、高誘電率膜8と、水素に対する還元触媒効果を有する導電性膜12とを順次堆積し、H2を含む雰囲気中にて基板1に対して熱処理を施すことで酸素欠損調整層6と酸化シリコン膜5との間にダイポールを形成する。その後、導電性膜12、高誘電率膜8、酸素欠損調整層6および酸化シリコン膜5等をパターニングしてゲート電極およびゲート絶縁膜を形成する。

(もっと読む)

相補型半導体装置及びその製造方法

【課題】 メタルゲート電極及び高誘電率ゲート絶縁膜を用いたn型MISトランジスタとp型MISトランジスタの双方において適正なしきい値電圧を得る。

【解決手段】 半導体基板30の表面部に形成された第1及び第2の半導体領域10,20と、第1の半導体領域10上に形成された、La及びAlを含む第1のゲート絶縁膜11及び第1のゲート電極12を有するn型MISトランジスタと、第2の半導体領域20上に形成された、La及びAlを含む第2のゲート絶縁膜21及び第2のゲート電極22を有するp型MISトランジスタと、を備えた相補型半導体装置であって、第2のゲート絶縁膜22における原子濃度比Al/Laが、第1のゲート絶縁膜11における原子濃度比Al/Laよりも大きい。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】高電圧動作するGaNベースの高出力化合物半導体装置を提供する

【解決手段】化合物半導体装置は、ソース領域およびドレイン領域の間にチャネル領域を含むIII−V族窒化物半導体層と、前記III−V族窒化物半導体層上に、前記チャネル領域を覆って形成された、金属酸化物成分を含む第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、前記チャネル領域において前記ゲート絶縁膜を露出する開口部を有する第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に、前記第2のゲート絶縁膜の表面を覆って形成され、前記開口部において前記第1のゲート絶縁膜に接するゲート電極と、前記III−V族窒化物半導体層上、前記ソース領域およびドレイン領域にそれぞれオーミック接触して形成されたソースおよびドレイン電極と、よりなる。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】表面リーク電流を低減することができる、III族窒化物半導体を用いた窒化物半導体素子およびその製造方法を提供すること。

【解決手段】この電界効果トランジスタは、n型GaN層3、p型GaN層4およびn型GaN層5が、順に積層された窒化物半導体積層構造部2を備えている。ゲート絶縁膜9が形成されている。このゲート絶縁膜9は、窒化物半導体積層構造部2の表面全域に接して形成された窒化シリコン膜20と、この窒化シリコン膜20の上に形成された酸化シリコン10膜とを備えている。ゲート絶縁膜9の上には、ゲート絶縁膜9を挟んで領域12に対向するようにゲート電極11が形成されている。また、窒化物半導体積層構造部2の引き出し部6の表面には、ドレイン電極7が接触形成されている。一方、窒化物半導体積層構造部2のn型GaN層5の頂面には、ソース電極13が接触形成されている。

(もっと読む)

化合物半導体装置とその製造方法

【課題】ゲート電極の近傍での耐圧が高められた化合物半導体装置とその製造方法を提供すること。

【解決手段】SiC基板20と、SiC基板20の上に形成された電子走行層21と、電子走行層21の上に形成された電子供給層23と、電子供給層23の上に互いに間隔をおいて形成されたソース電極27a及びドレイン電極27bと、ソース電極27aとドレイン電極27bの間の電子供給層23上に形成され、SiC基板20に向かって狭径となる開口29bを備えた保護絶縁膜30と、開口29b内の電子供給層23上に形成されたゲート電極32とを有する化合物半導体装置による。

(もっと読む)

溝ゲート型SiC半導体装置の製造方法

【課題】均一な厚さのゲート絶縁膜を形成することを可能とした溝ゲート型SiC半導体装置の製造方法を提供する。

【解決手段】六方晶SiCの(0001)Si面に形成した溝ゲート型SiC半導体装置の製造方法において、

ゲート絶縁膜を形成する処理が、下記の工程:

SiC基板のSi面に形成した溝の底面および側面と溝以外のSiC基板面全体に、堆積法によりSiO2層を形成する工程、および

1000〜1300℃での熱酸化により上記SiO2層を成長させて上記ゲート絶縁膜を完成させる工程

を含むことを特徴とする溝ゲート型SiC半導体装置の製造方法。

(もっと読む)

窒化物半導体素子

【課題】ノーマリオフ動作を実現することができるとともに、所望のゲート閾値電圧を実現することができる、窒化物半導体素子(HEMT)を提供すること。

【解決手段】このHEMTは、真性GaN層3およびn型AlGaN層4が積層された窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2は、ストライプ状の線状部10と、島状の合流部11とを備えている。複数本の線状部10は、隣接する線状部10との間に形成されたストライプ状のトレンチ6によって、互いに分離されている。線状部10においてトレンチ6内に露出した積層境界7には、ゲート絶縁膜12を介してゲート電極13が対向している。また、n型AlGaN層4には、ソース側合流部11Sおよびドレイン側合流部11Dにおいて、ソース電極14およびドレイン電極15がそれぞれ接触形成されている。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】チャネルが形成される部分における分極電荷の発生を抑えると共に、ブレークダウンの発生を抑制できる、窒化物半導体素子およびその製造方法を提供すること。

【解決手段】電界効果トランジスタは、n型GaN層3、p型GaN層4およびn型GaN層5が積層された窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2には、ドレイントレンチ6が形成されることにより、メサ積層部8が形成されている。メサ積層部8の壁面9は、n型GaN層5の頂面5aとの境界付近に位置する上側端部11と、n型GaN層3の上面3aとの境界付近に位置する下側端部12と、上側端部11と下側端部12との間に位置する中央部10とを有している。より具体的には、壁面9は、全体として傾斜角度の異なる複数の平面形状の傾斜部分17〜27を有している。そして、この壁面9には、ゲート絶縁膜15を挟んで、ゲート電極16が対向配置されている。

(もっと読む)

III族窒化物半導体を用いた電界効果トランジスタ

【課題】ノーマリオフ動作の半導体素子で、高耐圧と大電流の両立を図ったノーマリオフ型のIII族窒化物半導体を用いた電界効果トランジスタを提供する。

【解決手段】MOSFET200は、基板201上に形成されたp型GaN層の半導体層203と、チャネル領域203a上にゲート酸化膜205を介して形成されたゲート電極208と、ソース電極206及びドレイン電極207とを備える。チャネル領域203aの両側にコンタクト領域210,211が形成され、ゲート電極208とドレイン電極207の間にリサーフ領域212が形成されている。コンタクト領域210,211は、半導体層203にn型不純物をイオン注入法により注入して形成したn+型GaN層である。リサーフ領域212のシートキャリア濃度を1×1012 cm-2以上5×1013 cm-2以下の範囲内に設定し、かつ、そのシート抵抗を100 Ω/sq.以上10 kΩ/sq.以下の範囲内に設定して高耐圧と大電流の両立を図る。

(もっと読む)

ヘテロ構造電界効果トランジスタ

【課題】利得を高くしかつゲートリーク電流を小さくする。

【解決手段】チャネル層半導体11上に障壁層半導体12を形成し、障壁層半導体12に凹部13を設け、凹部13内にゲート絶縁膜14を形成し、ゲート絶縁膜14上にゲート電極15を形成し、ゲート絶縁膜14の誘電率をεi、障壁層半導体12の誘電率をεsとし、ゲート電極15の下方の障壁層半導体12の膜厚をdsg、それ以外の障壁層半導体12の膜厚をds、ゲート絶縁膜14の膜厚をdiとしたとき、di/εi+dsg/εs≦ds/εsまたはdi/εi+dsg/εs≦2(ds/εs)とする。

(もっと読む)

半導体装置及びその製造方法

【課題】III族窒化物半導体からなるトランジスタにおける相互コンダクタンスを向上しながら、ソース抵抗を小さくできるようにする。

【解決手段】半導体装置は、AlGaNからなる障壁層104と、該障壁層104の上に形成され、AlGaN/GaNの超格子層105を含み且つ障壁層104を露出するゲートリセス108を有するキャップ層107と、該キャップ層107の上にゲートリセス108を挟んで対向するように形成されたソース電極110及びドレイン電極111とを有している。少なくとも障壁層104におけるゲートリセス108からの露出部分の上には絶縁膜109が形成され、ゲートリセス108の底面上には、絶縁膜109を介在させてゲート電極112が形成されている。

(もっと読む)

121 - 140 / 193

[ Back to top ]