Fターム[5F140CE02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | リフトオフ (193)

Fターム[5F140CE02]に分類される特許

81 - 100 / 193

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

GaN系MOS型電界効果トランジスタ

【課題】ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOSFETを提供する。

【解決手段】p−GaNからなる電子走行層13とゲート電極18との間にゲート絶縁膜15が形成されたGaN系MOSFET10である。ゲート電極18は、AlGaInP混晶からなる。ゲート電極18は、p型AlGaInP混晶からなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20と、この上に形成された金属層(AuGe/Au電極)21とを有する。AlGaInP混晶の混晶比を変化させることにより、しきい値電圧を制御することが出来る。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚みのバラツキを抑制できるJFET、MOSFETもしくはMESFETを備えた半導体装置およびその製造方法を提供する。

【解決手段】n+型層3に対して異方性エッチングを行うことによって凹部4を形成したのち、この凹部4内にエピタキシャル成長させることによってn型チャネル層5を形成する。これにより、n型チャネル層5を一定の膜厚かつ一定の濃度で形成することが可能となる。このため、従来の構造と異なり、n型チャネル層5の膜厚が一定なバラツキのない構造とすることが可能となる。したがって、JFETの特性も一定とすることが可能となる。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

非対称スペーサをゲートとして備えるLDMOSトランジスタ

【課題】本発明は、横方向拡散金属酸化物半導体(LDMOS)トランジスタと、これを製造する方法を提供する。

【解決手段】LDMOSトランジスタはp型基板上に形成されたn型エピタキシャル層と、LDMOSトランジスタのゲートとして機能する非対称導体スペーサとを備える。LDMOSトランジスタはまた、非対称導体スペーサの両側のソース領域及びドレイン領域と、イオン注入を非対称導体スペーサに行うことで形成されたチャネル領域とを備える。非対称導体スペーサの高さはソース領域からドレイン領域に向かって増加する。チャネル領域は、基本的に完全に非対称導体スペーサの下に存在し、従来技術のLDMOSトランジスタのチャネル領域の長さよりも短い長さを有する。本発明のLDMOSトランジスタはまた、当該トランジスタの活性領域を囲むフィールド酸化物層と、非対称導体スペーサをn型エピタキシャル層から絶縁する薄い誘電体層とを備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリセス構造を採用してノーマリーオフ動作を可能とするも、バラツキの小さい安定した閾値を有し、十分な高耐圧を実現する信頼性の高い化合物半導体装置を実現する。

【解決手段】電子走行層3と電子供給層4との間にi−AlNからなる中間層5を形成し、キャップ構造7上のゲート電極の形成予定部位に中間層5をエッチングストッパとして用いて開口11aを形成した後、中間層5の開口11aに位置整合する部位に熱リン酸を用いたウェットエッチングにより開口11bを形成して、開口11a,11bからなる開口11をゲート絶縁膜12を介して下部が埋め込み、上部がキャップ構造7上方に突出するゲート電極13を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】オン抵抗を大幅に低減し、十分な高電圧動作且つ高出力を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ソース電極12及びドレイン電極13の下方の凹部7,8を充填し、電子供給層4の上方を覆う、Siを含むn−GaN層9が形成されており、n−GaN層9は、ソース電極12の下方及びドレイン電極13下方に含まれるSiの方が、ゲート電極15の近傍に含まれるSiよりも濃度が大きくなるように、Si添加量を漸減させながら成長形成される。

(もっと読む)

電界効果トランジスタ、半導体基板及び電界効果トランジスタの製造方法

【課題】高いチャネル移動度を有する電界効果トランジスタを提供する。

【解決手段】ゲート絶縁層と、前記ゲート絶縁層に接する第1半導体結晶層と、第1半導体結晶層に格子整合または擬格子整合する第2半導体結晶層とを有し、前記ゲート絶縁層、前記第1半導体結晶層および前記第2半導体結晶層が、ゲート絶縁層、第1半導体結晶層、第2半導体結晶層の順に配置されており、前記第1半導体結晶層がInx1Ga1−x1Asy1P1−y1(0<x1≦1、0≦y1≦1)であり、前記第2半導体結晶層がInx2Ga1−x2Asy2P1−y2(0≦x2≦1、0≦y2≦1、y2≠y1)であり、前記第1半導体結晶層の電子親和力Ea1が前記第2半導体結晶層の電子親和力Ea2より小さい電界効果トランジスタを提供する。

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】ノーマリオフでオン抵抗の低いHFETを実現すること。

【解決手段】HFET100は、第1キャリア走行層103上の互いに離間した2つの領域上に、2つに分離して形成されたノンドープのGaNからなる第2キャリア走行層104と、2つの分離した第2キャリア走行層104上にそれぞれ位置するAlGaNからなるキャリア供給層105を有している。第2キャリア走行層104とキャリア供給層105は、第1キャリア走行層103上に選択的に再成長させて形成した層である。第2キャリア走行層104とキャリア供給層105のヘテロ接合界面110は平坦性が高く、そのヘテロ接合界面110近傍は再成長に伴って混入した不純物はほとんど見られないため、2DEGの移動度を低下させることがなく、オン抵抗が低減されている。

(もっと読む)

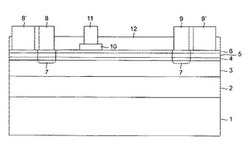

半導体装置及びその製造方法

【課題】ゲート電極のテーパ形状の傾斜度を緩やかにすることができるようにして、ゲート電極の破損が起こらないようにしながら、確実にさらなる微細化を実現した下部電極を形成できるようにする。

【解決手段】ソース電極2及びドレイン電極3を有する半導体領域1上に絶縁膜4を形成し、絶縁膜4上に複数のレジスト層5,6,7を含む積層レジスト8を形成し、積層レジスト8の最下層以外のレジスト層6,7に開口9を形成し、最下層のレジスト層5にリフロー用開口10を形成し、熱処理を施してリフロー用開口10に露出している最下層のレジスト層5の一部PTcをリフローさせ、リフローさせることによって最下層のレジスト層5の表面に形成された傾斜面11に連なるように最下層のレジスト層5に第1ゲート下部開口12Aを形成し、開口9、傾斜面11及び第1ゲート下部開口12Aの形状に応じた形状を持つゲート電極13を形成する。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプス現象およびゲートリーク電流を抑制することが可能な電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ1は、基板10と、チャネル層11と、キャリア供給層12と、ソース電極21と、ドレイン電極22と、ゲート電極23と、ソース電極21とドレイン電極22との間でキャリア供給層12に積層されて電流コラプス現象を抑制する第1絶縁層31と、ドレイン電極22に対向する第1絶縁層31の端とドレイン電極22との間に形成された開口部40と、開口部40に露出したキャリア供給層12に積層された第2絶縁層32とを備える。

(もっと読む)

半導体装置

【課題】インパクトイオン化現象によって発生した電子・正孔を効率よく吸収することが可能で正常な動作特性と高い信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置20は、基板21に対して順次積層されたバッファ層22、下地化合物半導体層23f(下地化合物半導体層23)、インパクトイオン制御層24、下地化合物半導体層23s(下地化合物半導体層23)、チャネル画定化合物半導体層26f(チャネル画定化合物半導体層26)、チャネル画定化合物半導体層26s(チャネル画定化合物半導体層26)、AlGaN(窒化アルミニウムガリウム)層28、GaN(窒化ガリウム)層29を備えている。インパクトイオン制御層24は、下地化合物半導体層23の積層範囲(積層範囲の厚さTst)内に積層されてインパクトイオン化現象の発生位置を制御する。

(もっと読む)

窒化物半導体装置および窒化物半導体装置製造方法

【課題】窒素不足に起因する移動度の低下を抑制し、窒素不足に起因するリーク電流を低減することができる窒化物半導体装置、その製造方法を提供する。

【解決手段】窒化物半導体装置1は、基板10と、バッファ層11と、窒化物半導体層(第1窒化物半導体層12、第2窒化物半導体層13、第3窒化物半導体層14)と、第1電極22と、第2電極23と、制御電極25とを備える。第1電極22と第2電極23との間で第3窒化物半導体層14の表面から第2窒化物半導体層13に渡って凹状に形成されたリセス部16を備え、リセス部16は、絶縁性窒化物で形成された窒化物絶縁膜17を備え、制御電極25は、導電性窒化物で形成され窒化物絶縁膜17(ゲート絶縁膜)に重ねて配置されている。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板と、前記基板上に形成されたバッファ層と、前記バッファ層上に形成された高抵抗層又は下地層と、前記高抵抗層又は下地層上に形成された、炭素を含有するキャリア濃度制御層と、前記キャリア濃度制御層上に形成されたキャリア走行層と、前記キャリア走行層上に形成された、前記キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層と、前記キャリア供給層から所定の深さに到るまで形成されたリセス部と、前記キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記キャリア供給層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備える。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法

【課題】低いオン抵抗と高い耐圧性とを有する電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法を提供する。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板101と、前記基板上に形成された高抵抗層103と、前記高抵抗層上に形成された、炭素濃度が1×1018cm−3以下であり層厚が10nmより厚く、100nm以下であるチャネル層104を含む半導体動作層106と、前記半導体動作層に前記チャネル層の内部に到る深さまで形成されたリセス部107と、前記半導体動作層上に前記リセス部を挟んで形成されたソース電極108およびドレイン電極109と、前記半導体動作層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜110と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極111と、を備える。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】量産性に優れた実用的なプロセスを用いて、炭化珪素基板と二酸化珪素膜との間の界面準位を大幅に低減することができ、デバイスとしての信頼性と電気特性が優れた炭化珪素半導体装置を提供する。

【解決手段】二酸化珪素膜51の形成後、CVD法により、二酸化珪素膜51上に酸窒化珪素膜61を形成する。その後、酸窒化珪素膜61が堆積された炭化珪素基体10を窒化処理反応炉に導入し、窒素酸化物ガス雰囲気中で窒化処理を行う。

(もっと読む)

GaN系電界効果トランジスタ

【課題】低オン抵抗・高耐圧で動作可能なGaN系化合物半導体デバイスを提供する。

【解決手段】基板上に形成されたバッファ層、チャネル層と、前記チャネル層上に形成され、ドリフト層と、前記ドリフト層上に配置されたソース電極およびドレイン電極と、ドリフト層に形成されたリセス部の内表面および前記ドリフト層の表面に形成された絶縁膜と、前記絶縁膜上に形成されたフィールドプレート部を有するゲート電極とを備えたGaN系電界効果トランジスタにおいて、前記ドリフト層は、前記リセス部と前記ドレイン電極との間に、シートキャリア密度が5×1013cm−2以上、1×1014cm−2以下のn型GaN系化合物半導体からなる電界緩和領域を有し、前記ドリフト層の前記電界緩和領域上に形成された前記絶縁膜の厚さが300nm以上であることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ(MOSFET)100は、基板101上に、p−GaNからなるチャネル層104、電子供給層106、電子供給層よりもバンドギャップエネルギーが小さい表面層107を順次積層し、電子供給層および表面層の一部をチャネル層に到る深さまで除去してリセス部108を形成したものである。表面層上には、リセス部を挟んでソース電極109およびドレイン電極110が形成され、表面層上およびチャネル層表面を含むリセス部内表面上にゲート絶縁膜111が形成され、さらにリセス部においてゲート絶縁膜上にはゲート電極112が形成されている。

(もっと読む)

81 - 100 / 193

[ Back to top ]