Fターム[5F140CE13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 露光 (102) | マスク工程 (75)

Fターム[5F140CE13]の下位に属するFターム

マスク材料 (44)

Fターム[5F140CE13]に分類される特許

1 - 20 / 31

半導体装置の製造方法及び半導体基板の洗浄方法

【課題】半導体基板の洗浄をより効率的に行うことができる半導体装置の製造方法及び半導体基板の洗浄方法等を提供する。

【解決手段】半導体基板20をその主面を鉛直方向及び水平方向から傾斜させて保持し、酸を含む洗浄液26に半導体基板20を浸漬する。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

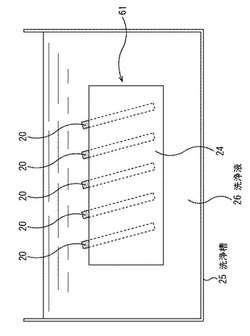

フォトマスクおよびこれを用いたトランジスタの製造方法

【課題】各トランジスタの特性を均一化することができるフォトマスクを提供する。

【解決手段】フォトマスク100には、複数のチャネルパターン101と、配線パターン102と、補助パターン103とが形成されている。複数のチャネルパターン101は、半導体基板上に形成された拡散層211の2つの縁部に跨って延ばされ、互いに並列に配された複数のチャネル部を形成するために、並列に配されている。配線パターン102は、チャネル部から延びたゲート配線部を形成するために、チャネルパターン101から延びている。補助パターン103は、各々のチャネル部の、拡散層の縁部212から一定の距離だけ離れた部分を、該チャネル部が延びている方向と直交する方向T2に広げるように、各々のチャネルパターン101に対して設けられている。各々のチャネルパターンに対して設けられた補助パターン103は、互いに同一形状になっている。

(もっと読む)

フォトマスクの製造方法及びプログラム

【課題】多重露光技術において、マスクパタン形成時における工程の複雑化を防止し、設計データに従った均一な形状を形成するためのマスクパタンを効率的に生成する。

【解決手段】目的となる設計データ101において、先端部分103a,104aで所定の離間距離をおいて対向する一対の線状設計パタン103,104について、設計データ上で仮想的に先端部分103a,104a間を接続する補助パタン105を配する処理を行い多重露光用マスクパタンを生成する。

(もっと読む)

半導体素子のトリプルゲート形成方法

【課題】プラズマのエッチング工程によって発生する素子特性および信頼性の劣化を防止することのできる半導体素子のゲート形成方法と、プラズマのエッチング工程によって発生する上部の隅部における電界の集中現象を防止することのできる半導体素子のゲート形成方法を提供すること。

【解決手段】支持基板と、埋め込み絶縁層および半導体層からなる基板を備えるステップと、蒸気エッチング工程で前記半導体層をエッチングして互いに離隔した第1トレンチおよび第2トレンチを形成するステップと、前記第1トレンチおよび第2トレンチを備える前記基板の上面にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上にゲート導電膜を形成するステップとを含む半導体素子のトリプルゲート形成方法を提供する。

(もっと読む)

サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【課題】 サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【解決手段】 直線端部を有する突出構造体を基板(8)上に形成する。突出構造体は電界効果トランジスタのゲートラインとすることができる。応力誘起ライナを基板(8)上に堆積させる。少なくとも2つの不混和性のポリマブロック成分を含む非感光性自己組織化ブロックコポリマ層を応力誘起ライナ(50)の上に堆積させ、アニールして不混和性成分を相分離させる。ポリマレジストを現像して少なくとも2つのポリマブロック成分のうちの少なくとも1つを除去し、突出構造体の直線端部(41)により入れ子になったラインのパターンを形成する。直線型のナノスケール・ストライプが、自己配列及び自己組織化のポリマレジスト内に形成される。応力誘起層は、サブリソグラフィック幅を有する直線型応力誘起ストライプにパターン化される。直線型応力誘起ストライプ(50)は主にそれらの縦方向に沿った一軸性応力をもたらし、下層の半導体デバイスに異方性応力を加える。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】ソース及びドレイン領域の幅を確保しつつ、フィンチャネルの幅のみを狭く形成できる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Fin型トランジスタの製造方法であって、シリコン基板1上に形成されたマスク層8をマスクとして、STI領域2を形成する工程と、マスク層8をウエットエッチングで縮退させて縮退マスク層8aを形成する工程と、縮退マスク層8aの表面にストッパ酸化膜16を形成し、全面にポリシリコン17を堆積した後、反射防止膜18、フォトレジスト19を形成する工程と、ワード線部分のフォトレジスト19を開口し、当該部分の反射防止膜18とポリシリコン17とを除去して、縮退マスク層8aを露出させた後に、フォトレジスト19を除去する工程と、縮退マスク層8aをマスクとして、縮退マスク層8aの下部両側のシリコン基板1をエッチングして、フィンチャネル30を形成する工程と、を備える。

(もっと読む)

半導体素子及びその製造方法

【課題】LDD領域がゲート電極の下部とオーバーラップするのを防止し、素子のパフォーマンスを向上させるようにした半導体素子及びその製造方法を提供する。

【解決手段】STI領域及びゲート領域が定義された下部構造物において、前記STI領域の内部に素子隔離膜を、前記ゲート領域の内部に犠牲層を形成する段階と、前記素子隔離膜及び前記犠牲層をバリア(barrier)とし、前記素子隔離膜と前記犠牲層との間にLDD領域を形成する段階と、前記ゲート領域の内部に形成された前記犠牲層を選択的に除去する段階と、前記犠牲層が除去された前記ゲート領域の内部側壁にスペーサを形成する段階と、前記犠牲層が除去された前記ゲート領域の内部下側にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜の上部にゲート電極を形成する段階と、前記LDD領域の上部に接合領域を形成する段階と、前記LDD領域を前記ゲート領域の下部両側端まで拡散させる段階と、を含む。

(もっと読む)

半導体素子及びその製造方法

【課題】チャネルが上下方向に形成されるトランジスタアレイ内における各トランジスタの駆動電圧の伝達効率を増大させるための半導体素子及びその製造方法を提供すること。

【解決手段】本発明の半導体素子は、複数の柱パターンと、各々の前記柱パターンを囲むゲート絶縁膜と、各々の前記ゲート絶縁膜を囲み、かつ、隣接する前記ゲート絶縁膜間を連接する導電膜とを備え、該導電膜は、ゲート電極及び配線として機能することを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、FIN状の半導体部やゲート電極を精度良く形成すること、又は素子間の特性バラツキを改善することで、特性の優れたFIN型トランジスタを備える半導体装置を提供することを目的とする。

【解決手段】本発明は、一方にソース領域、他方にドレイン領域が形成されたFIN状の半導体部10と、ソース領域とドレイン領域との間で、FIN状の半導体部10をゲート絶縁膜を介して囲むように形成されたゲート電極17とを備える半導体装置である。そして、本発明に係る1つ解決手段は、ゲート電極17が、ウェットエッチング可能なメタル材料又はシリサイド材料を用いている。

(もっと読む)

半導体装置のリセスゲート製造方法

【課題】リセスゲート工程中にリセス領域のエッチング工程で尖状のホーン(Horn)が発生することを抑制できる半導体装置のリセスゲート製造方法を提供すること。

【解決手段】シリコン基板21をエッチングし、活性領域を画定するトレンチ22を形成するステップと、該トレンチをギャップフィルする素子分離膜23を形成するステップと、前記活性領域のチャネル予定領域を開口させ、酸化膜と非晶質カーボン膜とが積層されたハードマスク膜を前記シリコン基板上に形成するステップと、前記ハードマスク膜をエッチング障壁(エッチングマスク)として前記チャネル予定領域を1次エッチングおよび2次エッチング(前記2次エッチングは前記非晶質カーボン膜を取除いた後に行う)の順序でエッチングし、デュアルプロファイルを有するリセス領域100を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【目的】レベンソン型マスクを用いた場合でもくびれ部分を形成せずにコンパクトな膜パターンを形成する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に被加工膜を形成する工程(S104)と、前記被加工膜上に非最細膜パターンを形成する工程(S114)と、前記非最細膜パターンが形成された後、レベンソン型マスクを用いて端部の位置が前記非最細膜パターンと重なるように最細パターンを露光する工程(S116)と、前記最細パターンが露光された後、前記最細パターン幅の最細膜パターンを形成する工程(S118−S122)と、前記非最細膜パターンと前記最細膜パターンとが転写されるように前記被加工膜をエッチングする工程(S126)と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】一方のゲート電極中の不純物が他方のゲート電極に拡散することを抑制するとともに、当該ゲート電極とコンタクトプラグとの接触抵抗を低減することが可能な技術を提供する。

【解決手段】ゲート電極30は、N型ゲート部分30NとP型ゲート部分30Pとを有している。ゲート電極30の側面31には、N型及びP型ゲート部分の境界領域BRに切り欠き部33が設けられている。N型ゲート部分30Nの側面31Nにおける切り欠き部33が形成されている領域31NNと、N型ゲート部分30Nの側面32Nとの間の最短距離は、N型ゲート部分30Nにおける第1活性領域の直上の部分の幅よりも小さく設定されている。コンタクトプラグ40は、N型及びP型ゲート部分の上面と、ゲート電極30の側面31の切り欠き部33が形成されている領域とに接触している。

(もっと読む)

自己整合方式でリセスゲートMOSトランジスタ素子を製作する方法

【課題】自己整合方式でリセスゲートMOSトランジスタ素子を製作する方法を提供する。

【解決手段】本発明による方法で製作されたMOSトランジスタ素子は、側壁と底部を有するゲート溝を備える基板と、ゲート溝の側壁に設けられるドレイン/ソースドープ領域と、ゲート溝の底部に設けられるゲートチャネル領域と、ゲート溝の側壁と底部に設けられ、ゲート溝の側壁における第一膜厚とゲート溝の底部における第二膜厚が相違するゲート酸化膜と、ゲート溝に埋め込まれるゲート導体とを含む。

(もっと読む)

半導体装置の製造方法

【課題】p−MOSトランジスタとn−MOSトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板11の第1領域13、第2領域、14にn型、p型ゲート電極膜34、37を形成する工程と、ゲート電極膜34、37上に第1保護膜38および第2保護膜39を形成する工程と、第2保護膜39に、ゲート電極サイズL1、L2より大きいサイズL3のゲート電極パターンを形成する工程と、第2保護膜39bに選択的に燐イオンを注入し、熱酸化速度が第2保護膜39aより大きくなるようにする工程と、第2保護膜39a、39bを熱酸化し、生成した第1および第2酸化膜42、43を選択的にエッチングして、ゲート電極パターンをスリム化する工程と、スリム化された第2保護膜39a、39bを用いてサイズL1、L2のゲート電極18、23を形成する工程と、を具備する。

(もっと読む)

リセスゲート及びその製造方法

【課題】バルブ型リセスパターンのボールパターン内に残留するボイドの大きさを小さくすることができる半導体素子のリセスゲート及びその製造方法を提供すること。

【解決手段】リセスゲートは、第1直径を有する第1ボールパターン部25A及び第2直径を有する第2ボールパターン部27からなり、第1ボールパターン部25Aが基板21の表面側に位置するバルブ型リセスパターン100を有する基板21と、バルブ型リセスパターン100の内面及び基板21の表面に形成されたゲート絶縁膜28と、ゲート絶縁膜28上に形成され、バルブ型リセスパターン100内に埋め込まれた導電膜29とを備える。バルブ型リセスパターン100が、断面形状及び直径が異なる第1と第2のボールパターン部25A、27からなるひょうたん形であるので、導電層(例えば、ポリシリコン)内に残留するボイドの大きさを小さくすることができる。

(もっと読む)

半導体製造方法およびエッチングシステム

【課題】疎パターン領域と密パターン領域を有する半導体の製造方法において、再現性良く疎パターンと密パターン寸法の独立制御を可能とし、各パターンの露光完の寸法及びゲート電極寸法の長期変動を抑制する。

【解決手段】マスクパターンが疎に形成された領域と密に形成された領域とを有する半導体基板上に積層膜を成膜する成膜工程とマスクパターンを形成するリソグラフィ工程S1と装置内の堆積物を除去するクリーニング工程S11Cとマスクパターンを細線化するトリミング工程S3とマスクパターンを積層膜に転写するドライエッチング工程S4、S5から成る半導体製造方法において、トリミング工程S3の前もしくは後に、シーズニング工程S11Sに続いて堆積ステップ工程S2を導入する。

(もっと読む)

ゲートパターンを形成するための二重露光二重レジスト層プロセス

【課題】ゲートパターンを形成するための二重露光二重レジスト層方法を提供する。

【解決手段】プレーナCMOSトランジスタを形成する方法は、ゲート層を形成する工程を、ゲート層パターンの第一の部分でレジスト層をパターン形成し、次にゲートのパターンで多結晶シリコンをエッチングする第一の工程に分割する。第二の工程で、ゲートパッドと局所相互接続との画像で第二のレジスト層をパターン形成し、次にゲートパッドと局所相互接続とのパターンで多結晶シリコンをエッチングし、それによって異なる露光区域からの回折およびその他のクロストークの数を減らす。

(もっと読む)

半導体装置の製造方法

【課題】段差部に近接した領域に導電体パターン(例えばゲート電極)が形成される場合に、導電体パターンの寸法精度を高くすることができる半導体装置の製造方法を提供する。

【解決手段】本半導体装置の製造方法は、素子分離膜2上、絶縁膜12上、及びゲート絶縁膜3b〜3d上に導電膜4を形成する工程と、絶縁膜12とゲート絶縁膜3bの間に位置する導電膜4に開口部4eを形成する工程と、導電膜4上及び開口部4e内にフォトレジスト膜51を形成し、その後露光及び現像することにより、ゲート絶縁膜3bから3dそれぞれの上方に位置するレジストパターン51b〜51d、及び絶縁膜12の上方に位置するレジストパターン51aを形成する工程と、レジストパターン51a〜51dをマスクとして導電膜4をエッチングすることにより、ゲート電極4b〜4d及び上部導電膜4aを形成する工程とを具備する。

(もっと読む)

パターンレイアウト及びレイアウトデータの生成方法

【課題】拡散領域あるいはゲート配線の角部内側に発生する丸まりとマスクの位置合わせ誤差とに起因するトランジスタ特性の変動を防止し得るパターンレイアウトを提供する。

【解決手段】ゲート配線12に直交する方向にレイアウトされる拡散領域11に、該ゲート配線12の一側でL字形に屈曲する屈曲部13を備えたパターンレイアウトであって、ゲート配線12の他側において、該ゲート配線12との間隔が屈曲部13とゲート配線12との間隔と同一となる補助パターン14を拡散領域11に備えた。

(もっと読む)

1 - 20 / 31

[ Back to top ]