Fターム[5F152BB04]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,062) | トランジスタ、ダイオード (1,748) | バイポーラトランジスタ (30)

Fターム[5F152BB04]に分類される特許

1 - 20 / 30

半導体装置の製造方法

【課題】半導体基板の主面に形成した溝部表面へのイオン注入量やイオン注入深さのバラつきを抑え、イオンが注入されたドーパンド領域を活性化して、厚み、イオンドープ量、活性化状態がほぼ均一なドーパンド層を形成できる半導体装置の製造方法を提供する。

【解決手段】半導体基板の主面に溝部を形成し、該溝部を形成した半導体基板の主面側にイオンを注入した後、イオンが注入されたドーパンド領域にレーザを照射してアニール処理を行う半導体装置の製造方法であって、前記ドーパンド領域にイオンを注入する前に、前記溝部の側面にレーザを照射して、該溝部の側面の表面段差を平滑化する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ソース領域に3C−SiC構造のSiCを用いて低い寄生抵抗を実現し、高い性能を備える半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、第1のn型炭化珪素層と、第1のn型炭化珪素層よりもn型不物濃度の低い第2のn型炭化珪素層を有する半導体基板と、第2のn型炭化珪素層に形成される第1のp型不純物領域と、第2のn型炭化珪素層に形成される4H−SiC構造の第1のn型不純物領域と、第2のn型炭化珪素層に形成され、第1のn型不純物領域よりも深さの浅い3C−SiC構造の第2のn型不純物領域と、第2のn型炭化珪素層、第1のp型不純物領域、第1のn型不純物領域の表面にまたがるゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、第1のn型不純物領域上に形成され、底面部と側面部を備え、少なくとも側面部で第1のn型不純物領域との間に第2のn型不純物領域を挟む金属シリサイド層と、を備える。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体装置の製造方法

【課題】良好な電気特性を有する半導体装置の製造方法を提供する。

【解決手段】電極層の上に希土類金属シリサイド膜とアモルファスシリコン膜とを形成し、希土類金属シリサイド膜とアモルファスシリコン膜とをマイクロ波を用いて加熱することにより、希土類金属シリサイド膜の結晶構造に応じた結晶配向を持つように、アモルファスシリコン膜を結晶化させる。

(もっと読む)

IGBTの製造方法及びIGBT

【課題】従来のIGBTの製造方法によって製造されるIGBTよりもオン抵抗の低いIGBTを、安価な製造コストで製造することが可能なIGBTの製造方法を提供する。

【解決手段】パンチスルー型のIGBTを製造するためのIGBTの製造方法。n−型シリコン基板112を準備する第1工程と、n−型シリコン基板112の第1主面側表面にMOS構造120を形成する第2工程と、n−型シリコン基板112を研削・研磨してn−型シリコン基板112を薄くする第3工程と、n−型シリコン基板112の第2主面側からn−型シリコン基板112の内部にn型不純物を導入する第4工程と、n−型シリコン基板112の第2主面側の表面上にp型不純物を含有する多結晶シリコン層116”を形成する第5工程と、n−型シリコン基板112の第2主面側からレーザー光を照射して多結晶シリコン層116”を溶融させる第6工程とをこの順序で含む。

(もっと読む)

半導体装置の製造方法

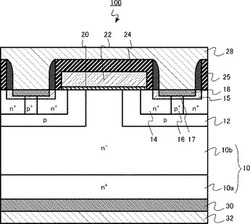

【課題】IGBTの耐圧及びリーク電流を改善する。

【解決手段】半導体装置70では、N+バッファ層2上のN−高抵抗層3の表面領域にPベース層4、P+コンタクト層5、N+ソース層6を形成し、N−高抵抗層3上にゲート絶縁膜7及びゲート電極8を積層形成する。ゲート電極8上に絶縁膜9を形成後、N+バッファ層2の裏面に第1のレーザを照射して裏面を平坦化する。次に、N+バッファ層2の裏面にイオン注入と第2のレーザ照射によりP+ドレイン層1を形成する。

(もっと読む)

半導体材料の熱処理方法及び半導体レーザ光遮蔽板

【課題】連続発振型の半導体レーザ光を使用して、光エネルギーの損失を抑制し、短時間で安定した、効率のよい半導体材料の加熱方法及び加熱装置を提供するものである。

【解決手段】

半導体レーザ光1を、発熱層2に照射してこの発熱層2を発熱させ、この発熱層2と接する半導体材料4を熱処理する方法において、半導体レーザ光1を発熱層2上をスキャン操作を行わせ、半導体材料4を熱処理するに際し、半導体レーザ光1の折り返し操作が行われる部位Pに対応する発熱層2の表面に半導体レーザ光遮蔽板8を配置すると共に、半導体レーザ光遮蔽板8に於けるスキャンされる半導体レーザ光1と対向している端縁部9に沿ってテーパー部10を設ける半導体材料の熱処理方法。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置の作製方法

【課題】量産に適した半導体基板、及び当該半導体基板を用いた半導体装置を作製することを目的の一とする。

【解決手段】支持基板上に絶縁層、第1の電極、第1の不純物半導体層を少なくとも有する積層体を形成し、第1の不純物半導体層上に一導電型を付与する不純物元素が添加された第1の半導体層を形成し、第1の半導体層上に、一導電型を付与する不純物元素が添加された第2の半導体層を、第1の半導体層とは異なる条件により形成し、固相成長法により、第1の半導体層及び第2の半導体層の結晶性を向上させて、第2の不純物半導体層を形成し、第2の不純物半導体層に、一導電型を付与する不純物元素を添加し、一導電型とは異なる導電型を付与する不純物元素を添加し、ゲート絶縁層を介してゲート電極層を形成し、ソース電極層又はドレイン電極層を形成する。

(もっと読む)

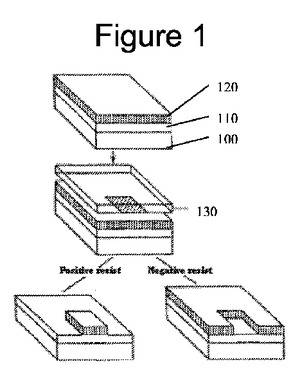

均一な結晶シリコン薄膜を製造するリソグラフィ方法

位置が制御される結晶粒の領域を備える結晶半導体膜と、位置が制御される結晶粒の位置を基準として規定される位置にある結晶半導体膜の中に位置するデバイスとを含む、結晶膜の中の既知の位置に位置付けられる電子デバイスに関係する方法および装置が説明される。この方法は、各照射ステップが、膜のリソグラフィで画成される領域を少なくとも部分的に融解させ、横方向に結晶化させ、横方向成長長さに垂直である少なくとも1つの長い粒子境界を有する横方向に成長した結晶粒の領域を得る、3つ以上の重複する照射ステップを使用して半導体膜の少なくとも一部を照射することと、少なくとも1つの長い粒子境界の位置を識別することと、長い粒子境界の位置を基準にして規定される位置にある半導体膜の中に電子デバイスを製造することとを含む。  (もっと読む)

(もっと読む)

半導体膜の製造方法、半導体装置の製造方法、電子機器の製造方法、半導体膜、半導体装置および電子機器

【課題】特性を向上させた炭化シリコン膜(半導体膜)の製造方法を提供する。

【解決手段】第1シリコン膜S1上に炭素源ガスを供給することにより前記シリコン膜上に第1炭化シリコン膜3を形成する第1工程と、前記第1炭化シリコン膜上に、第2シリコン膜5を形成する第2工程と、前記第2シリコン膜上にレーザを照射する第3工程と、前記第3工程後の前記第1炭化シリコン膜上に炭素源ガスおよび珪素源ガスを供給することにより第2炭化シリコン膜を形成する第4工程と、を有する。かかる方法によれば、レーザ照射により、第1炭化シリコン膜3を改質でき、当該膜上に成長する第2炭化シリコン膜の特性が良好となる。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、低温下で結晶性の良好な単結晶および多結晶を提供することを目的とする。また、本発明は、固相成長法を用い、信頼性の高い半導体装置を提供することを目的とする。

【解決手段】

本発明では、非晶質半導体薄膜を基板あるいは絶縁膜上に堆積するにあたり、特に、その膜を構成する主元素からなる非晶質膜の平均原子間隔分布が、単結晶の平均原子間隔分布にほぼ一致するように形成し、これに再結晶化エネルギーを付与し固相成長を行い単結晶半導体薄膜3を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた酸化物半導体膜と、を備えるトランジスタを有し、酸化物半導体膜の少なくともチャネル形成領域となる領域に対して加熱処理が行われている。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 ガラスやプラスチックなどの単結晶でない基体上に単結晶半導体薄膜を形成することで、任意の基体上に十分に動作速度の速いトランジスタを作製することを可能とする。また、それにより任意の基体上に集積回路を形成することを可能にする。

【解決手段】 基体上に基体全面に渡って結晶方位が揃った配向中間層を形成し、その上にアモルファス状態もしくは多結晶状態の半導体薄膜を形成し、その半導体薄膜を適切な条件でアニールすることによって、基体全面に渡って結晶方位が揃った半導体薄膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル層の結晶性を良好にして、漏れ電流の減少とオン電圧の低減を図ることができる半導体装置の製造方法を提供する。

【解決手段】開口部5を有する酸化膜4上にn+エピタキシャル成長層9を形成した後で、レーザアニールして結晶欠陥を消滅させたn+エピタキシャル成長層9とし、このn+エピタキシャル成長層9にn+バッファ層(n+エピタキシャル成長層9の一部)やp+ベース層13およびn++エミッタ層14(ソース層)を形成して半導体装置(IGBTやMOSFETなど)を製作することで、漏れ電流とオン電圧(オン抵抗)の低減を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】簡便な製造プロセスにより、量産対象である大型のガラス基板に、信

頼性が高く、集積度の高い高性能半導体装置を得る。

【解決手段】結晶化を促進する微量の触媒元素であるニッケル105が導入さ

れたa−Si膜103を加熱処理して結晶化された結晶性のケイ素膜108の一

部の領域(高濃度不純物領域)108bに選択的に5族Bから選択された不純物

であるリン117を導入し、第2の加熱処理を行って、結晶性のケイ素膜108

のリン117が導入されていない領域(能動領域)108aに含まれるニッケル

105を高濃度不純物領域に移動させる。この第2の加熱処理は、能動領域10

8aに含まれるニッケル105の濃度と高濃度不純物領域108bに含まれるニ

ッケル105の濃度とが少なくとも熱平衡状態の偏析状態に達しないように行う

。

(もっと読む)

半導体装置の接合形成方法およびそれにより作製された半導体装置

【課題】半導体装置の所望のソース/ドレイン接合深さの近傍にある、エンドオブレンジ(EOR)領域の存在の、負の影響を低減する。

【解決手段】装置とその装置の製造方法が記載され、それにより、装置がエンドオブレンジ欠陥から離れた浅い接合深さを有する。方法は、シリコンのような結晶半導体中に、第1深さまで、アモルファス領域を形成する工程と、これに続いて、例えば炭素のような置換型元素を、第1深さより浅い深さまで注入する工程とを含む。続いて領域は例えばリンやボロンのような適当なドーパントでドープされ、熱処理工程によりアモルファス領域が再結晶化される。

(もっと読む)

電子装置、表示装置、インターフェイス回路、差動増幅装置

【課題】表示装置を含む絶縁基板上に、MOSトランジスタとバイポーラトランジスタを同時に集積してなる画素制御回路を形成する。

【解決手段】絶縁基板(101)上に設けられ所定の方向に結晶化された半導体薄膜(105)に形成された半導体薄膜を用いて形成された複数の半導体素子を有する電子装置または表示装置であって、複数の半導体素子は、MOSトランジスタ(300)と、少なくともラテラルバイポーラ薄膜トランジスタ(100)またはMOS−バイポーラハイブリッド薄膜トランジスタ(200)のいずれかを含む電子装置または表示装置。

(もっと読む)

1 - 20 / 30

[ Back to top ]