Fターム[5F152LL18]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 固相 (58)

Fターム[5F152LL18]に分類される特許

1 - 20 / 58

単結晶の半導体層を支持基板上に転写する方法

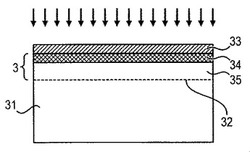

【課題】単結晶の半導体層を支持基板上に転写し、転写された層がもはや脆化注入によって生成される可能性のある結晶欠陥を含まない方法を提供する。

【解決手段】単結晶の半導体層3を支持基板上に転写する方法に関し、(a)ドナー基板31に注入種を注入するステップと、(b)ドナー基板31を支持基板に接合するステップと、(c)層3を支持基板上に転写するためにドナー基板31を破壊するステップと、前記単結晶の層3の第2の部分35の結晶格子の秩序を乱すことなしに、転写されるべき単結晶の層3の部分34が非晶質にされるステップであり、部分34、35が、それぞれ、単結晶の層3の表面部分および埋め込み部分であるステップと、非晶質の部分34が500℃未満の温度で再結晶化されるステップであり、第2の部分35の結晶格子が再結晶化のための種結晶として働くステップとを含む。

(もっと読む)

多層膜構造体及びその形成方法

【課題】新規な多層膜構造体及びその形成方法を提供すること。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

(もっと読む)

シリコン−オン−インシュレーター構造及びバルク基板に対するSiGeの堆積

【課題】欠陥を最小限としながら、SiGe−オン−インシュレーター構造を製造するため及びシリコン上に歪み緩和SiGe層を製造するための方法を提供する。

【解決手段】アモルファスSiGe層600が、トリシラン及びGeH4からCVDによって、ドーパントの1以下のモノレイヤー上に堆積される。これらのアモルファスSiGe層600は、融解または固相エピタキシー(SPE)プロセスによってシリコン上に再結晶される。融解プロセスは、好ましくは、全体のゲルマニウム含量を希釈するようなゲルマニウムの拡散も引き起こし、そして絶縁体の上層のシリコン500を実質的に消費する。SPEプロセスは、下地のシリコン500中へのゲルマニウムの拡散を用いてまたは用いずに実際され得、従って、SOI及び従来の半導体基板に適用可能である。

(もっと読む)

半導体基板の作製方法

【課題】SOI基板等の単結晶半導体層を有する半導体基板において、該単結晶半導体層を厚膜化することを課題の一とする。また、半導体基板の量産性を向上させることを課題の一とする。

【解決手段】単結晶半導体基板上に非晶質半導体層を形成した後、絶縁層を介して支持基板と貼り合わせ、該単結晶半導体基板の一部を、非晶質半導体層とともに支持基板上に転載する。そして、非晶質半導体層を固相エピタキシャル成長させることで、支持基板上に厚い単結晶半導体層を形成するものである。

(もっと読む)

半導体基板の作製方法及び光電変換装置の作製方法

【課題】低温での固相エピタキシャル成長法を用いて、結晶性の高いシリコン層を厚く形成した半導体基板を提供することを課題の一とする。その際、従来の気相エピタキシャル成長法と比べ、結晶成長速度を大きくすることを課題の一とする。

【解決手段】絶縁層を介してベース基板に設けられた単結晶シリコン層上に、堆積初期の一部で、単結晶シリコン層と結晶面の配列の揃った針状シリコン層が気相エピタキシャル成長するようにシリコン層を形成し、針状シリコン層を種結晶として、シリコン層の他部を固相エピタキシャル成長させて、単結晶及び前記結晶シリコン層の厚さが厚い半導体基板を作製する。

(もっと読む)

SOI基板の作製方法

【課題】低温での固相エピタキシャル成長法を用いて、単結晶半導体層の膜厚の厚いSOI基板を提供することを課題の一とする。その際に、予めシード層となる単結晶半導体層の結晶欠陥を修復しなくとも、良好にエピタキシャル成長が進む方法を提供することを課題の一とする。また、シード層の結晶欠陥を修復する工程を別に設けなくとも、固相エピタキシャル成長によりシード層である単結晶半導体層の結晶性が回復したSOI基板を提供することを課題の一とする。

【解決手段】絶縁層を介して基板に設けられた第1単結晶半導体層上に、非晶質半導体層を形成する。非晶質半導体層は、成膜温度100℃以上275℃以下、シラン系ガスを希釈しないで用いるCVD法により形成する。熱処理を行って、非晶質半導体層を固相エピタキシャル成長させて、単結晶半導体層の膜厚の厚いSOI基板を作製する。

(もっと読む)

半導体装置の製造方法

【課題】 格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、シリコン基板21の一部に絶縁膜22を形成し、シリコン基板21と絶縁膜22上にアモルファスSiGe層23を形成し、シリコン基板を熱処理し、アモルファスSiGe層23を絶縁膜22上に横方向に固相若しくは液相成長させて結晶化し、シリコン基板22と絶縁膜22上に格子定数が後に形成される材料層の格子定数に整合されたSiGe層23bを形成する。

(もっと読む)

部分SOIウェーハの製造方法

【課題】活性層からバルク層に達した孔部で堆積中のアモルファスもしくは多結晶シリコンを単結晶化させる際に埋め込み酸化膜の領域での欠陥発生を抑制させる部分SOIウェーハの製造方法を提供する。

【解決手段】活性層を被う保護膜の一部に形成された窓部を通して、活性層と埋め込み酸化膜との各一部をエッチングして孔部を形成後、孔部にアモルファスシリコンを堆積させる。孔部内のアモルファスシリコンを、単結晶化させる場合に高エネルギ光の照射を行うことでエピタキシャル成長速度を速め、埋め込み酸化膜の領域を通過する際に発生する欠陥密度を抑制できる。

(もっと読む)

半導体基板の作製方法

【課題】炭化シリコンを含む半導体基板の新たな作製方法を提供することを目的の一とする。

【解決手段】シリコン基板表面に炭化処理を施して炭化シリコン層を形成し、シリコン基板にイオンを添加することにより、シリコン基板中に脆化領域を形成し、シリコン基板とベース基板とを絶縁層を介して貼り合わせ、シリコン基板を加熱して、脆化領域においてシリコン基板を分離することにより、ベース基板上に絶縁層を介して炭化シリコン層とシリコン層の積層構造を形成し、シリコン層を除去して炭化シリコン層の表面を露出させることにより半導体基板を作製する。

(もっと読む)

SOIウェーハの製造方法

【課題】 容易な方法により低コストで部分SOI構造を有するSOIウェーハを製造する方法等を提供する。

【解決手段】 シリコン単結晶ウェーハの表面に第1絶縁膜を形成する工程、該第1絶縁膜の表面に非単結晶シリコン膜を形成する工程、非単結晶シリコン膜の表面からシリコン単結晶ウェーハの表面まで達する開口部を形成することにより、第1絶縁膜及び非単結晶シリコン膜が部分的に表面上に積層されたシリコン単結晶ウェーハを得る工程、このシリコン単結晶ウェーハに対し水素ガス若しくは不活性ガス又はこれらの混合ガス雰囲気下でRTA処理を行うことにより、非単結晶シリコン膜を開口部のシリコン単結晶ウェーハが露出された部分に接するようにマイグレーションさせ、非単結晶シリコン膜を単結晶化して、第1絶縁膜を埋め込み絶縁膜とする部分SOI構造を形成する工程を含む、部分SOI構造を有するSOIウェーハを製造する方法。

(もっと読む)

貼り合わせウェーハの製造方法

【課題】貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成可能な貼り合わせウェーハの製造方法を提供する。

【解決手段】高エネルギ光を、活性層用ウェーハの素材は溶融しないが、吸光係数が高いアモルファスシリコンは溶融する条件で貼り合わせ基板の活性層用ウェーハ側の面に照射し、この窓部内のシリコンを溶融させて固化させる。このとき、アモルファスシリコンを単結晶シリコンに液相エピタキシーにより変質させれば、貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成できる。

(もっと読む)

シリコン膜の形成方法、pn接合の形成方法、及びこれを用いて形成されたpn接合

【課題】マイクロヒーターを利用して、多結晶シリコンからなるシリコン膜を形成する方法、pn接合を形成する方法、及びこれを用いて形成されたpn接合を提供する。

【解決手段】シリコン膜は、基板10及び基板と離間した金属パターン30を含むマイクロヒーターを利用して形成されうる。マイクロヒーターの金属パターンに電圧を印加して金属パターンを加熱し、シリコンを含むソース気体にマイクロヒーターを露出させて金属パターン上にシリコン膜100を形成することができる。シリコン膜は、多結晶シリコンからなりうる。pn接合は、基板10、基板上の導電層20、及び基板と離間した金属パターン30を含むマイクロヒーターを利用して形成されうる。マイクロヒーターの金属パターンに電圧を印加して金属パターンを加熱することで、金属パターンと導電層との間にpn接合を形成することができる。pn接合は、多結晶シリコンを含みうる。

(もっと読む)

基板上に単結晶半導体層を作製する方法

【課題】基板上に高品質の単結晶半導体層を形成する。

【解決手段】基板上に単結晶の半導体材料の層を形成する方法に関し、この方法は、基板1を準備する工程と、基板上に少なくとも1つの半導体材料の単分子層2を含むテンプレートをエピタキシャル成長する工程と、テンプレート上に半導体材料のアモルファス層3を堆積する工程と、熱処理またはレーザアニールを行い、半導体材料のアモルファス層を、半導体材料の単結晶層に完全に変える工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体部材が単結晶の半導体材料からなり、特性が良好な半導体装置及びその製造方法を提供する。

【解決手段】単結晶のシリコンからなるシリコン基板11上に絶縁膜12を形成し、絶縁膜12に開口部12aを形成し、絶縁膜12上に開口部12aを介してシリコン基板11と接触するようにアモルファスシリコン膜を形成し、このアモルファスシリコン膜をシリコン基板11を起点として固相エピタキシャル成長させて、その後パターニングする。これにより、開口部12aの直上域から外れた領域の一部に、単結晶のシリコンからなるシード層を形成する。次に、このシード層を覆うようにアモルファスシリコン膜を堆積させ、このアモルファスシリコン膜をシード層を起点として固相エピタキシャル成長させて、単結晶シリコン膜を形成する。そして、この単結晶シリコン膜をパターニングすることにより、シリコンピラー33を形成する。

(もっと読む)

SOI基板の作製方法

【課題】単結晶半導体層とベース基板との密着性を向上させ、貼り合わせ不良を低減することを目的の一とする。

【解決手段】半導体基板の表面にラジカル処理を行うことにより、半導体基板に第1の絶縁膜を形成し、第1の絶縁膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板に脆化領域を形成し、第1の絶縁膜上に第2の絶縁膜を形成し、第2の絶縁膜の表面とベース基板の表面とを接合させた後に熱処理を行い、脆化領域において分離することにより、ベース基板上に第1及び第2の絶縁膜を介して半導体層を形成し、半導体層にエッチング処理を行い、エッチング処理が行われた半導体層にレーザビームを照射する。

(もっと読む)

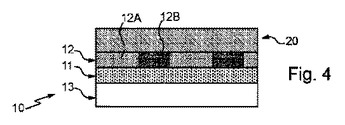

埋め込み電気絶縁連続層を備えたハイブリッド基板を製造する方法

本発明は、次の工程を含むハイブリッド基板を製造する方法に関する:第1の単結晶領域(12A)およびアモルファス材料の第2の隣接領域(12B)から構成された下位電気絶縁連続層(11)によって延在された混合層を含み、上記第2の領域は、上記第1の基板の自由表面の少なくとも一部を構成する第1の基板(10)が準備され;その表面で、所定の結晶配向を備えた基準層を含む第2の基板(20)が、少なくとも上記アモルファス領域上に、疎水性分子結合によって上記第1の基板に結合され;固相へのアモルファス領域の少なくとも一部の再結晶が、基準層の結晶配向に従って実行され、2つの基板は結合界面で分離される。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】量産に適した半導体基板、及び当該半導体基板を用いた半導体装置を作製することを目的の一とする。

【解決手段】支持基板上に絶縁層、第1の電極、第1の不純物半導体層を少なくとも有する積層体を形成し、第1の不純物半導体層上に一導電型を付与する不純物元素が添加された第1の半導体層を形成し、第1の半導体層上に、一導電型を付与する不純物元素が添加された第2の半導体層を、第1の半導体層とは異なる条件により形成し、固相成長法により、第1の半導体層及び第2の半導体層の結晶性を向上させて、第2の不純物半導体層を形成し、第2の不純物半導体層に、一導電型を付与する不純物元素を添加し、一導電型とは異なる導電型を付与する不純物元素を添加し、ゲート絶縁層を介してゲート電極層を形成し、ソース電極層又はドレイン電極層を形成する。

(もっと読む)

エピタキシャルウェーハおよびその製造方法

【課題】エピタキシャル膜の表面欠陥と、この膜の外周部のスリップとの発生を防止でき、ゲッタリングサイトを有して製造コストも低減可能なエピタキシャルウェーハおよびその製造方法を提供する。

【解決手段】シリコンウェーハ11の表層への酸素のイオン注入量を低減し、イオン注入層15を低温のエピタキシャル成長時に熱処理し、表層に不完全埋め込み酸化膜12を形成する。そのため、ウェーハ11の低コスト化が図れる。また、イオン注入の不具合で酸化膜が途切れても、エピタキシャル膜14のピットの発生が抑制され、膜14の表面欠陥が低減される。また、膜14の外周部の厚肉化を防ぎ、ウェーハ外周部のスリップを抑制できる。しかも、不完全埋め込み酸化膜12はゲッタリングサイトも兼ねるので、エピタキシャルウェーハ10の金属汚染を防げる。

(もっと読む)

半導体基板の作製方法

【課題】量産に適した方法で半導体基板を提供することを目的の一とする。または、資源を有効に活用しつつ、優れた特性の半導体基板を提供することを目的の一とする。

【解決手段】単結晶半導体基板にイオンを照射して単結晶半導体基板中に損傷領域を形成し、単結晶半導体基板上に絶縁層を形成し、絶縁層と支持基板を密着させて単結晶半導体基板と支持基板を貼り合わせ、損傷領域において単結晶半導体基板を分離させることにより、支持基板上に第1の単結晶半導体層を形成し、第1の単結晶半導体層上に第1の半導体層を形成し、第1の半導体層上に、第1の半導体層とは異なる条件により第2の半導体層を形成し、固相成長法により、第1の半導体層及び第2の半導体層の結晶性を向上させて、第2の単結晶半導体層を形成する。

(もっと読む)

1 - 20 / 58

[ Back to top ]