Fターム[5F152MM06]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | 電子素子 (1,201) | トランジスタ (962) | JFET (21)

Fターム[5F152MM06]に分類される特許

1 - 20 / 21

炭化珪素基板の製造方法および炭化珪素半導体装置の製造方法

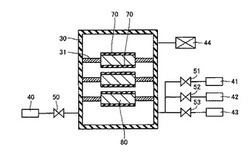

【課題】炭化珪素基板の表面を保護することができる方法を提供する。

【解決手段】炭化珪素基板80が準備される。2μg/m3以上の二酸化窒素濃度を有する雰囲気に炭化珪素基板80をさらすことによって、炭化珪素基板80上に酸化膜70が形成される。

(もっと読む)

複合基板およびその製造方法

【課題】複数の炭化珪素単結晶を有する複合基板およびその製造方法を提供する。

【解決手段】炭化珪素と異なる材料から作られた支持層31と、支持層31上に形成された炭化珪素層32とを有するベース部30が準備され、前記ベース部30の炭化珪素層32上に第1および第2の炭化珪素単結晶11、12の各々が接合される。前記接合する工程は、前記炭化珪素層32に前記第1および第2の炭化珪素単結晶11,12の各々を対向させる工程と、前記炭化珪素層11,12のうち前記第1および第2の炭化珪素単結晶11,12に対向する部分のそれぞれを、前記第1および第2の炭化珪素単結晶11,12上に昇華および再結晶させることによって、前記第1および第2の炭化珪素単結晶11,12の各々に前記炭化珪素層32を接合する工程とを含む複合基板の製造方法。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、単結晶炭化珪素からなるSiC基板20を準備する工程と、坩堝80内においてSiC基板20の一方の主面20Bに面するようにベース基板10を配置する工程と、坩堝80内において、ベース基板10を、ベース基板10を構成する炭化珪素の昇華温度よりも高い温度域に加熱することにより、SiC基板20の一方の主面20Bに接触するように炭化珪素からなるベース層10を形成する工程とを備えている。そして、ベース層10を形成する工程では、坩堝80内に珪素を含有するガスが導入される。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、炭化珪素からなるベース基板10および単結晶炭化珪素からなるSiC基板20を準備する工程と、ベース基板10の主面10A上に接触するようにSiC基板20を載置して、積層基板を作製する工程と、積層基板を、SiC基板20よりもベース基板10の温度が高くなるように加熱することにより、ベース基板10とSiC基板20とを接合する工程と、SiC基板20が接合されたベース基板10の、SiC基板20とは反対側の主面10B上にエピタキシャル成長層30を形成する工程とを備えている。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、単結晶炭化珪素からなるSiC基板20を準備する工程と、坩堝70内においてSiC基板20の一方の主面20Bに面するようにベース基板10を配置する工程と、坩堝70内において、ベース基板10を、ベース基板10を構成する炭化珪素の昇華温度以上の温度域に加熱することによりSiC基板20の一方の主面20Bに接触するように炭化珪素からなるベース層10を形成する工程とを備えている。そして、ベース層10を形成する工程では、坩堝70内に、SiC基板20およびベース基板10とは別の、珪素を含む物質からなる珪素発生源91が配置される。

(もっと読む)

炭化珪素基板の製造方法

【課題】結晶性に優れた大口径の炭化珪素基板の製造方法を提供する。

【解決手段】炭化珪素基板の製造方法は、単結晶炭化珪素からなる複数のSiC基板20が平面的に見て複数並べて配置された状態で、複数のSiC基板20の一方の主面20C側が支持層10により接続された複合基板2を準備する工程と、複合基板2において隣り合う複数のSiC基板20の端面20B同士を接合する工程とを備えている。そして、複数のSiC基板20の端面20B同士を接合する工程では、隣接するSiC基板20の端面20B同士が互いに対向する領域に面する支持層10の表面を含む領域である接続部が加熱される工程と、当該接続部が冷却される工程とが繰り返して実施される。

(もっと読む)

半導体基板の製造方法

【課題】大型であって、かつ半導体装置を高い歩留りで製造することができる半導体基板の製造方法を提供する。

【解決手段】第1の炭化珪素基板11の第1の側面S1と、第2の炭化珪素基板12の側面S2とが互いに面するように、処理室60内にベース部30および第1および第2の炭化珪素基板11、12が配置される。処理室60内に、炭素元素と化合することができる固体材料からなる吸収部51が設けられる。第1および第2の側面S1、S2を互いに接合するために、炭化珪素が昇華し得る温度以上に処理室60内の温度が高められる。温度を高める工程において吸収部51が炭化される。

(もっと読む)

ガラスボンディング層を使用して半導体構造及び半導体素子を製造する方法並びにかかる方法によって形成した半導体構造及び半導体素子

半導体構造及び半導体素子を製造する方法は、ガラスを使用して基板にシード構造をボンディングするステップを含む。シード構造は、半導体材料の結晶を含むことができる。ガラスを使用して基板にボンディングされたシード構造の熱処理を利用して、シード構造内部の歪状態を制御することができる。シード構造を、室温において圧縮歪の状態に置くことができる。ガラスにボンディングされたシード構造を、半導体材料の成長用に使用することができる、又は、さらなる方法では、シード構造を、ガラスを使用して第1の基板にボンディングすることができ、熱処理してシード構造内部の歪状態を制御することができ、第2の基板を、非ガラス質材料を使用してシード構造の反対側の面にボンディングすることができる。 (もっと読む)

半導体基板、半導体デバイス、半導体基板の製造方法および半導体デバイスの製造方法

【課題】窒化物層上にエピタキシャル層を形成したときにクラックが発生することを抑制でき、かつエピタキシャル層が半導体基板から剥がれることを抑制できる半導体基板および半導体基板の製造方法を提供する。

【解決手段】半導体基板10aは、窒化物層12の主面12a上にエピタキシャル層を形成するための半導体基板であって、異種基板11と、異種基板11上に形成された窒化物層12とを備え、窒化物層12は応力緩和領域を有する。

(もっと読む)

III−V族加工基板の製造方法およびそのIII−V族加工基板

【課題】パッシベーション層を備え、改善した性能を持つデバイスを実現できるIII−V族加工基板およびその製造方法を提供する。

【解決手段】III−V族加工基板の製造方法は、<110>または<111>の結晶方位を持つ第1のIII−V化合物からなる上側層(2)を備えたベース基板(I)を用意すること、第2のIII−V化合物からなるバッファ層(3)を少なくとも形成することを含んだ、中間層(II)を形成することであって、中間層(II)は、ベース基板の上側層(2)の上に位置し、これと接触するようにすること、IV族半導体材料からなる擬似格子整合パッシベーション層(4)を成長させることであって、擬似格子整合パッシベーション層は、中間層(II)の上に位置し、これと接触するようにすることを含む。

(もっと読む)

GaN単結晶体およびその製造方法、ならびに半導体デバイスおよびその製造方法

【課題】GaN単結晶体を成長させる際および成長させたGaN単結晶体を基板状などに加工する際、ならびに基板状のGaN単結晶体上に少なくとも1層の半導体層を形成して半導体デバイスを製造する際に、クラックの発生が抑制されるGaN単結晶体およびその製造方法ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本GaN単結晶体10は、ウルツ型結晶構造を有し、30℃において、弾性定数C11が348GPa以上365GPa以下かつ弾性定数C13が90GPa以上98GPa以下、または、弾性定数C11が352GPa以上362GPa以下である。

(もっと読む)

半導体基板の製造方法、半導体デバイスの製造方法、半導体基板および半導体デバイス

【課題】低抵抗な窒化物層を基板へ貼り合わせた半導体基板の製造方法、半導体デバイスの製造方法、半導体基板および半導体デバイスを提供する。

【解決手段】半導体基板10の製造方法は、以下の工程を備えている。主面と、主面と反対側の裏面とを有する窒化物基板を準備する。窒化物基板の裏面に、気相のイオンを注入する。窒化物基板の裏面と、異種基板11とを貼り合わせることにより、貼り合わせ基板を形成する。貼り合せ基板から窒化物基板の一部を剥離する。700℃を超える温度で熱処理する。

(もっと読む)

III族窒化物系化合物半導体基板とその製造方法

【課題】平面視したときに限定された範囲にp型領域が形成されているIII族窒化物系化合物半導体基板であり、p型領域とその周囲の領域との間に段差がない基板を提供する。

【解決手段】 III族窒化物系化合物半導体下層6の表面にIII族窒化物系化合物半導体を結晶成長させるに先立って、p型領域12を形成したい範囲に相当する範囲内の下層6の表面近傍にマグネシウムとアルミニウムの双方を含ませておく。下層6の限られた範囲の表面近傍にマグネシウムとアルミニウムの双方が含まれていると、その上に上層16を結晶成長したときに、結晶成長する上層16の限られた範囲にマグネシウムが移動してp型領域12になるともに、下層6に含まれているアルミニウムがマグネシウムの移動範囲を制約し、下層6におけるマグネシウムの含有範囲10と上層16におけるマグネシウムの含有範囲12をよく一致させる。

(もっと読む)

選択エピタキシャル成長を用いた横型接合型電界効果トランジスタの製造方法

接合型電界効果トランジスタ(JFET)などの半導体素子を製造する方法が記載される。方法は、自己整合であり、素子のゲート又はソース/ドレイン領域を形成するために、再成長マスク物質を用いた、選択的エピタキシャル成長に関する。方法は、イオン注入の必要性を除去する。素子は、SiCなどのワイドギャップ半導体物質から形成される。再成長マスク物質は、TaCである。素子は、放射線及び/または高温にさらされることを含む過酷な環境において使用される。 (もっと読む)

半導体装置の製造方法

【課題】Si基板上に、AlN及びGaNを成長させるにあたり、Si基板の抵抗値の低下を抑制する。

【解決手段】成長装置内にシリコン基板を導入して、成長装置内でシリコン基板を水素雰囲気中でクリーニングする。次に、成長装置内を不活性ガス雰囲気にした後、成長装置内を減圧し、さらに、シリコン基板の温度を成長温度まで昇温する。次に、成長装置内に原料ガスを導入して、シリコン基板上に有機金属気相成長法によりバッファ層として窒化アルミニウム層を形成する。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 ガラスやプラスチックなどの単結晶でない基体上に単結晶半導体薄膜を形成することで、任意の基体上に十分に動作速度の速いトランジスタを作製することを可能とする。また、それにより任意の基体上に集積回路を形成することを可能にする。

【解決手段】 基体上に基体全面に渡って結晶方位が揃った配向中間層を形成し、その上にアモルファス状態もしくは多結晶状態の半導体薄膜を形成し、その半導体薄膜を適切な条件でアニールすることによって、基体全面に渡って結晶方位が揃った半導体薄膜を形成する。

(もっと読む)

n型炭化ケイ素基板を少なくとも部分的に除去することによって炭化ケイ素パワーデバイスを作製する方法、およびそのように作製された炭化ケイ素パワーデバイス

炭化ケイ素パワーデバイスが、n型炭化ケイ素基板上でp型炭化ケイ素エピタキシャル層を形成すること、および、そのp型炭化ケイ素エピタキシャル層上で炭化ケイ素パワーデバイス構造を形成することによって作製される。n型炭化ケイ素基板は、p型炭化ケイ素エピタキシャル層を露出するように、少なくとも部分的に除去される。オーミック接触部が、露出されているp型炭化ケイ素エピタキシャル層の少なくとも一部の上で形成される。n型炭化ケイ素基板を少なくとも部分的に除去すること、および、p型炭化ケイ素エピタキシャル層上でオーミック接触部を形成することによって、p型基板を使用することの欠点を低減する、または解消することができる。関連の構造もまた述べられている。  (もっと読む)

(もっと読む)

p型のIII族窒化物半導体の形成方法

【課題】所望の領域にp型のIII 族窒化物半導体を形成すること。

【解決手段】n- −GaN層11上にSiO2 膜12を形成し、p−GaNを形成したい領域上のSiO2 膜12を除去する(図1a)。SiO2 膜12をマスクとして、高濃度にMgがドープされたp−GaN層13をMOCVD法によって選択成長させ(図1b)、そのあとSiO2 膜12を除去する(図1c)。n- −GaN層11の上面、および、p−GaN層13の上面に、n- −GaN層11をMOCVD法により再成長させる。このとき、n- −GaN層11の再成長とともに、下層のp−GaN層13からその上方のn- −GaN層11の領域中にMgが拡散する。その結果、p−GaN層13上層のn- −GaN層11の領域には、p型領域14が形成される(図1d)。

(もっと読む)

半導体電子デバイス

【課題】異種基板上のバッファ層の結晶性を向上させた窒化物系化合物半導体を有する半導体電子デバイスを提供する。

【解決手段】窒化物系化合物半導体を有する半導体電子デバイスにおいて、基板10上に窒化物系化合物半導体からなるバッファ層20及び半導体動作層30を順次積層してなり、前記バッファ層20は、第1の層22と第2の層23が積層された複合層を1層以上有し、第1の層22と第2の層23との各格子定数の差は0.2%以上であり、第1の層22の厚さは、100nm以上、1000nm以下である。

(もっと読む)

半導体積層体の形成方法

【課題】本願の目的は、Si基板上に結晶性と表面モフォロジーの良い単結晶SiC層を形成することにある。

【解決手段】本願の骨子は、Si層上にSiやSiCよりも融点の低いSiGe層と非晶質SiCを形成し、これら積層構造をSiGeの融点以上に加熱することにより、SiCとSi基板の間の歪みを緩和し、同時に非晶質SiCからの結晶化を行うことで、結晶性と表面諸フォジーが良好な単結晶SiC層を形成する。

(もっと読む)

1 - 20 / 21

[ Back to top ]