Fターム[5F152MM08]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | 発光素子 (415)

Fターム[5F152MM08]の下位に属するFターム

Fターム[5F152MM08]に分類される特許

21 - 40 / 51

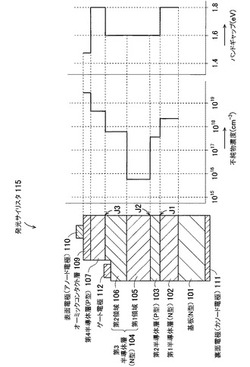

発光サイリスタ、発光素子アレイ、発光装置および画像形成装置

【課題】 ベース層のキャリア濃度および厚み寸法を大きく設定することなく、発光強度に対する電流増幅率βの影響を抑制することのできる発光サイリスタ、発光素子アレイ、発光装置および画像形成装置を提供することである。

【解決手段】 発光サイリスタは、基板上に第1半導体層、第1半導体層と反対導電型の第2半導体層、第1半導体層と同じ導電型の第3半導体層、および第1半導体層と反対導電型の第4半導体層がこの順に積層されており、第3半導体層のバンドギャップは、第2半導体層のバンドギャップと略同一、かつ、第1および第4半導体層のバンドギャップより狭幅であり、第3半導体層は、基板側の第1領域と基板と反対側の第2領域とからなり、かつ、第1領域の不純物濃度は1×1016(cm−3)未満である。

(もっと読む)

半導体材料を形成するためのエピタキシャル方法および構造

改良された特性を備えた半導体材料、基板、およびデバイスの製造方法および構造が開示される。歪みが低減された構造を形成するための構造および方法が、複数の実質的に歪み緩和されたアイランド構造を形成し、半導体材料の歪み緩和された実質的に連続した層を引き続きさらに成長するために、このようなアイランド構造を利用することを含む。 (もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】基板と当該基板に形成される化合物半導体とを電気的に絶縁しつつ、結晶性に優れた化合物半導体を備えた半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたシード結晶と、シード結晶の上方に設けられた化合物半導体と、シード結晶と化合物半導体との間に設けられ、シード結晶よりも大きな抵抗率を有する高抵抗層とを備え、シード結晶と化合物半導体とが格子整合または擬格子整合している半導体基板を提供する。

(もっと読む)

グラフェン層が成長された基板およびそれを用いた電子・光集積回路装置

【課題】グラフェン層成膜の大面積化や基板材質の選択自由度の拡大、製造の低コスト化を実現するグラフェン層が成長された基板およびそれを用いた電子・光集積回路装置を提供する。

【解決手段】本発明に係るグラフェン層が成長された基板は、単層または複数層からなるグラフェン層が成長された基板であって、前記グラフェン層は前記基板の表面に対して略平行に成長しており、前記グラフェン層に対向する前記基板の最表面には金属酸化物の原子層が存在し、前記グラフェン層の前記基板に隣接する層と前記金属酸化物の原子層との層間距離が0.34 nm以下であることを特徴とする。また、前記金属酸化物の原子層の算術平均表面粗さRaが1 nm以下であることが好ましい。

(もっと読む)

ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置

【課題】格子定数が広範囲にわたり可変であり、且つ結晶性に優れた基板およびその製造方法を提供する。また上記基板上に形成された半導体素子を提供する。

【解決手段】6回対称軸をを有する結晶からなる第1の層11と、該結晶上に形成される金属酸窒化物結晶からなる第2の層12を有し、第2の層12が、In、Ga、Si、Ge及びAlからなる群から選択される少なくとも1つの元素と、NとOとZnとを主要元素として含み、且つ第2の層12が面内配向性を有する積層構造体を備えたウルツ鉱型結晶成長用基板。

(もっと読む)

半導体基板及びその製造方法

【課題】化合物半導体素子を同一Si基板上に既に形成されているSi−LSI素子と電気的に接続された構造を有する半導体基板及びその製造方法を提供すること。

【解決手段】Si単結晶基板上に、Si−LSIを最上層保護膜なしの状態で形成し、Si−LSI全体をSiO2層で覆う。所望のエリアのSiO2層間膜を除去し、所望のエリアのSi基板表面のみを露出させる。Si−LSIを保護膜する役目を担うSiN膜をSi−LSIの上部及び側面に形成する。SiN膜を除去して露出しているSi基板表面を水素原子で終端せしめた後に、露出していたSi基板上に化合物半導体膜を直接形成する。更に化合物半導体膜を所望の形状に加工して素子を作り、この素子の保護膜を形成し、Si−LSIと前記化合物半導体素子とを電気的に接続するためのコンタクトと金属配線を設ける。

(もっと読む)

歪み層緩和のための硬化層

【課題】 歪み材料層を緩和する方法を提供する。

【解決手段】 歪み材料層と、歪み材料層の第1の面上に形成された低粘度層とを準備するステップと、該第1の面と反対側の該歪み材料層の第2の面の少なくとも一部分上に硬化層を形成し、それによって多層スタックを形成するステップと、該多層スタックを加熱処理し、それによって該歪み材料層を少なくとも部分的に緩和させるステップと、を含む。

(もっと読む)

窒素化合物半導体基板の製造方法および窒素化合物半導体基板

【課題】結晶性のよい窒素化合物半導体層が得られ、しかも低コストで生産性のよい窒素化合物半導体基板の製造方法を提供する。

【解決手段】所定厚さの表面Si層3と埋め込み絶縁層4とを有するSi基板1を準備する工程と、上記Si基板1を炭素系ガス雰囲気中で加熱して上記表面Si層3を単結晶SiC層6に変成させる際に、上記埋め込み絶縁層4との界面8近傍のSi層を残存Si層5として残す工程と、表面の単結晶SiCに対してさらに窒素化合物半導体層15をエピタキシャル成長させる工程とを行なう。

(もっと読む)

III−V族化合物半導体の結晶成長方法と結晶成長装置

【課題】 III-V族化合物半導体の結晶成長方法において、半導体下地層と半導体層の界面に高濃度なn型領域が形成されることを抑制する技術を提供すること。

【解決手段】 シリコンをエッチング可能なエッチング材を利用して半導体下地層の表面を洗浄する工程と、洗浄後の半導体下地層をアルコールに浸漬する工程と、浸漬された状態で半導体下地層をガス置換室に搬入する工程と、ガス置換室内を大気から置換ガスに置換する工程と、ガス置換室に連結する反応室に液体から取り出した半導体下地層を搬入する工程と、反応室内で半導体下地層の表面に前記半導体層を結晶成長させる工程を備えている。置換ガスは、シリコン濃度が0.2ppm以下である。

(もっと読む)

結晶成長シミュレーター

【課題】次世代の光半導体デバイス開発の基礎になるものと期待されている、量子ドットの形成過程について、従来の静的な計算結果ではなく、動的過程を解明するための有効な計算方法を提供する。

【解決手段】対象を三領域に分割し、そのそれぞれで別系統の計算手法を適用することにより、マルチスケールかつハイブリッドな計算機シミュレーションの方法を実現している。それらのうち、最上部の表面層領域における原子拡散により引き起こされた歪みの効果を、中間部のサブメッシュ上の分離力学計算領域に伝え、この領域で緩和をおこなった結果を、下部領域にある有限要素法の計算部分に伝達することにより、隔たった領域間の歪みの相互作用の効果を、中間部を通じて表面領域にフィードバックさせるようなアルゴリズムが構成できる。また、そのアルゴリズムを実現するシステムを構築する。

(もっと読む)

窒化物半導体厚膜基板

【課題】複数の窒化物半導体層を含む発光素子構造を成長させるために望ましい窒化物半導体厚膜基板を提供し、ひいてはその基板を用いて優れた特性を有する窒化物半導体発光装置を提供する。

【解決手段】複数の窒化物半導体層を含む発光素子構造を成長させるための窒化物半導体厚膜基板であって、基板は対向する第1と第2の主面を有し、基板の第1主面は3×1018cm-3以上1×1019cm-3以下の高不純物濃度の第1の層領域で形成されており、基板は3×1018cm-3以下1×1017cm-3以上でかつ第1層領域より低い低不純物濃度の第2の層領域をも少なくとも含み、基板の第1主面はその上に前記発光素子構造を成長させるための面であり、発光素子構造の形成後に第1主面の側で部分的に露出される基板の領域が電極を形成するための領域として使用されることを特徴とする。

(もっと読む)

膜移し変えプロセス

【課題】エピタキシャル成長の表面にできた欠陥を貼りあわせ基板に持ち込まない製造方法を提供する。

【解決手段】表面近傍の域に欠陥を有する第一基板4から、第二材料でできたホスト基板20上に、第一材料の層を移し変えるプロセスであって:a)第一の薄化基板24を形成するために、第一基板を薄化する段階;b)注入面6を形成するために前記第一基板にイオンまたは原子注入し、移し変えるべき層を画定する段階;c)注入面に沿って基板を破断することにより、ホスト基板20上に前記層を移し変える段階;を含むプロセスによって欠陥をなくした貼りあわせ基板を作ることができる。

(もっと読む)

サファイア単結晶基板及びその製造方法

【課題】窒化物系化合物半導体素子、SOS(silicn−on−sapphire)デバイス等を作製する際のエピタキシャル成長法に好適な均一なステップ−テラス構造を有するサファイア単結晶基板をその傾斜角度に関わらず効率的に製造する方法を提供する。

【解決手段】(0001)面からの傾斜角度4が調整された主面を有し、かつ表面研磨されたサファイア単結晶基板を、不活性ガス雰囲気下、又は10容量%以下の酸素分圧を有する酸素ガス及び不活性ガスからなる混合ガス雰囲気下に熱処理を行う。

(もっと読む)

半導体素子、半導体素子の製造方法、発光素子及び電子素子

【課題】幅広い用途に対応することができ、製造コストが低く、大面積化が可能な半導体素子、半導体素子の製造方法、発光素子及び電子素子を提供すること。

【解決手段】半導体素子の基板が金属を主成分とするので、大面積の単結晶基板を安価に得ることができる。しかも、金属にはフレキシブル性があるため、例えば基板を曲げて使用することが可能である。これにより、スペースに応じて曲げて使用するなどの幅広い用途に対応することができ、製造コストが低く、大面積化が可能な半導体素子を得ることができる。

(もっと読む)

薄膜半導体、太陽電池および発光素子の製造方法

【課題】フレキシブルで、各種基板と一体化できる結晶性にすぐれたシリコン等の薄膜半導体を安価に製造することができ、これにより太陽電池を安価に製造することができるようにする。

【解決手段】半導体基体の表面を陽極酸化することにより多孔質度が異なる2層以上の層から構成される多孔質層12を形成し、多孔質層12の表面に太陽電池などの半導体膜13を成膜し、この半導体膜13を、多孔質層12を介して半導体基体から剥離する。陽極酸化する工程は、通電量の選定と、連続通電か間欠通電かの選定とにより、多孔質の異なる多孔質層のうち、比較的低多孔率の低多孔率層に対して、比較的高多孔率の高多孔率層の形成位置を制御する工程を含む。

(もっと読む)

シリコンベースの領域及びGaAsベースの領域を関連付けるSOI基板の製造方法

【課題】本発明は、誘電体層及びシリコン薄層を支持するシリコン支持体を備えるSOI基板の薄層において、シリコンベース領域及びGaAsベース材料領域を関連付けるSOI基板の製造方法を提供する。

【解決手段】2°から10°の角度で不整合にされたシリコン支持体と、例えば(001)面に対して平行に配向させたシリコンベース薄層とを備えたSOI基板を提供する段階、シリコンベースの薄層の少なくとも一つの領域を保存する段階と、誘電体層が露出されるまでシリコンの薄層の少なくとも一つの保存されない領域を除去する段階、シリコン支持体が露出されるまで保存されない領域において誘電体層に開口部を設ける段階、エピタキシによって、開口部によって露出された支持体のシリコンから、露出された誘電体層上に、不整合にされたゲルマニウムを成長させる段階、得られた不整合にされたゲルマニウムからGaAsベースの材料を成長させる段階を備える。

(もっと読む)

AlN系III族窒化物単結晶厚膜の作製方法

【課題】結晶品質に優れ、かつクラックのないAlN系III族窒化物単結晶厚膜を作製する方法を提供する。

【解決手段】エピタキシャル基板上に、HVPE法によってAlN系III族窒化物厚膜を得る場合に、通常の成長条件で厚膜層の形成を行う第1の工程と、その時点で形成されている厚膜層を第1の工程における厚膜層の形成温度T1以上の高温状態T2で保持することを主目的とする第2の工程とを適宜のタイミングで切り替えつつ繰り返し行うようにする。これにより、それぞれの第1の工程において厚膜層に内在する歪を第2の工程で逐次に緩和させつつ厚膜層を形成することができる。厚膜層の形成後に面内方向に作用する引張応力を、あらかじめ緩和させた状態の厚膜層を形成することができるので、厚膜層におけるクラックの発生を抑制することができる。

(もっと読む)

単結晶窒化アルミニウム積層基板の製造方法

【課題】サファイア等単結晶α−Al2O3基板表面から内部に向かってアルミナ成分を窒化アルミニウムに変換して単結晶窒化アルミニウム膜を生成する単結晶窒化アルミニウム積層基板の製造方法においてその製造効率が改善される方法を提供する。

【解決手段】1600〜1750℃の温度条件で単結晶α−Al2O3基板を窒化処理して単結晶窒化アルミニウム膜を生成し、単結晶窒化アルミニウム積層基板を製造する方法であって、窒化処理の前段階において800〜1400℃のH2雰囲気下で単結晶α−Al2O3基板表面を活性化処理することを特徴とする。この活性化処理により、その後に行われる窒化反応の反応速度が著しく向上するため、単結晶窒化アルミニウム積層基板の製造効率を飛躍的に改善させることが可能となる。

(もっと読む)

堆積途中でアニーリングを行うことによってバンドが設計された超格子を有する半導体素子の作製方法

半導体素子の作製方法は、各々が複数の層からなる複数の群を積層した状態で有する超格子を作製する工程を有して良い。複数の層からなる群の各々は、基礎となる半導体部分を画定する、複数の積層された基礎となる半導体分子層、及び隣接する基礎となる半導体部分の結晶格子の内部に束縛された少なくとも1の非半導体分子層を有して良い。当該方法はまた、その超格子が完全に形成される前に少なくとも1回のアニーリングを行う工程をも有して良い。  (もっと読む)

(もっと読む)

磁性半導体薄膜及び磁性半導体薄膜の製造方法

【課題】半導体プロセスの整合性に優れており、基板と磁性半導体薄膜とが格子整合し、Tcが300K付近でバラツキが少ないII−IV−V2族の磁性半導体薄膜及び磁性半導体薄膜の製造方法を提供する

【解決手段】加熱した基板上に緩衝層を形成した後に、該緩衝層上に磁性半導体層として遷移金属元素を添加したZnSnAs2をエピタキシャル成長させる。

(もっと読む)

21 - 40 / 51

[ Back to top ]