Fターム[5F152MM19]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | SOI基板 (257)

Fターム[5F152MM19]に分類される特許

1 - 20 / 257

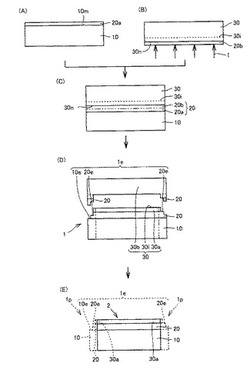

III族窒化物複合基板の製造方法

【課題】支持基板とIII族窒化物層との接合が良好なIII族窒化物複合基板の製造方法を提供する。

【解決手段】本III族窒化物複合基板の製造方法は、目標とする基板径より大きい径の主面10mを有する支持基板10と、目標とする基板径より大きい径の主面30nを有しその主面30nから所定の深さの位置にイオン注入領域30iが形成されたIII族窒化物基板30とを、中間層20を介在させて貼り合わせ、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合された第1のIII族窒化物複合基板1を形成し、第1のIII族窒化物複合基板1の外周部を除去することにより目標とする基板径に等しい径の主面を有する第2のIII族窒化物複合基板2を得る。

(もっと読む)

素子形成用基板及びその製造方法

【課題】貼り合わせ界面における界面準位密度を低減することができ、LSIの更なる低消費電力化及び高速化等に寄与する。

【解決手段】絶縁膜上にGe層やSiGe層を形成した素子形成用基板の製造方法であって、Ge基板11の表面上にSi膜12を形成する工程と、Si膜12上に高誘電率絶縁膜13を形成する工程と、Si膜12及び高誘電率絶縁膜13が形成されたGe基板11と表面に酸化膜22が形成された支持基板21とを、高誘電率絶縁膜13と酸化膜22とを接触させて接着する工程と、支持基板21に接着された前記Ge基板11を、該Ge基板11の裏面側から研磨して薄くする工程とを含む。

(もっと読む)

半導体ウェハ

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

III族窒化物複合基板

【課題】支持基板と酸化物膜との接合強度および酸化物膜とIII族窒化物層との接合強度が高いIII族窒化物複合基板を提供する。

【解決手段】本III族窒化物複合基板1は、支持基板10と酸化物膜20とIII族窒化物層30aとを含み、支持基板10は多結晶で形成され、III族窒化物層30aは少なくともc軸方向に配向しているIII族窒化物結晶で形成され、酸化物膜20は不純物が添加され、不純物の濃度は、酸化物膜20において支持基板10側の第1主面20sからIII族窒化物層30a側の第2主面20tにかけて膜厚方向で変化し、第1主面20sにおける不純物の濃度は第2主面20tにおける不純物の濃度よりも高い。

(もっと読む)

貼り合わせSOIウェーハの製造方法

【課題】 本発明は、SOI層の膜厚の面内均一性の良好なSOIウェーハを製造する方法を提供することを目的とする。

【解決手段】 イオン注入層が形成されたボンドウェーハのイオン注入された側の表面とベースウェーハの表面とを絶縁膜を介して貼り合わせた後、前記ボンドウェーハの一部を前記イオン注入層で剥離して、貼り合わせSOIウェーハを作製し、その後、平坦化処理を行う貼り合わせSOIウェーハの製造方法であって、

前記剥離後の貼り合わせSOIウェーハに対し、前記SOI層表面の周辺部の自然酸化膜が除去され、中央部の自然酸化膜が残存するように、水素ガスを含む雰囲気でRTA処理を行い、前記中央部に自然酸化膜が残存した貼り合わせSOIウェーハに対し、前記SOI層の面内膜厚レンジが1.5nm以下となるように前記平坦化処理を行うことを特徴とする貼り合わせSOIウェーハの製造方法。

(もっと読む)

複合基板の製造方法および複合基板

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成し、転写先基板に接することとなる前記半導体結晶層形成基板の第1表面と、前記第1表面に接することとなる前記転写先基板の第2表面と、が向かい合うように、前記半導体結晶層形成基板と前記転写先基板とを貼り合わせ、前記半導体結晶層形成基板および前記転写先基板の全部または一部をエッチング液に浸漬して前記犠牲層をエッチングし、前記半導体結晶層を前記転写先基板側に残した状態で、前記転写先基板と前記半導体結晶層形成基板とを分離する。ここで、前記転写先基板が、非可撓性基板と有機物層とを有し、前記有機物層の表面が、前記第2表面であるものとする。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

薄膜製造方法、それを用いた半導体デバイスの製造方法およびそれらに用いられる半導体薄膜部品

【課題】高品質な半導体薄膜を製造する薄膜製造方法を提供する。

【解決手段】薄膜製造方法は、a−Si膜等の半導体薄膜を第1の基板上に堆積する工程S1と、第1の基板をエッチングして第1の基板と半導体薄膜との間に中空部を形成する工程S2と、半導体薄膜に第2の基板を接触させる工程S3と、半導体薄膜に第2の基板を押し付け、または半導体薄膜が溶融する強度を有するレーザ光を半導体薄膜に照射する工程S4と、第1の基板を半導体薄膜から引き離す工程S5とを備える。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、及びSOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供する。

【解決手段】損傷半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層を除去するエッチング処理と、硝酸、硝酸によって酸化された半導体基板を構成する半導体材料を溶解する物質、半導体材料の酸化速度及び酸化された半導体材料の溶解速度を制御する物質、及び亜硝酸を含み、亜硝酸の濃度が10mg/l以上1000mg/l以下である混合液を用いて、未損傷の半導体領域に対して損傷半導体領域を選択的に除去するエッチング処理と、を行うことで半導体基板を再生する。

(もっと読む)

単結晶の半導体層を支持基板上に転写する方法

【課題】単結晶の半導体層を支持基板上に転写し、転写された層がもはや脆化注入によって生成される可能性のある結晶欠陥を含まない方法を提供する。

【解決手段】単結晶の半導体層3を支持基板上に転写する方法に関し、(a)ドナー基板31に注入種を注入するステップと、(b)ドナー基板31を支持基板に接合するステップと、(c)層3を支持基板上に転写するためにドナー基板31を破壊するステップと、前記単結晶の層3の第2の部分35の結晶格子の秩序を乱すことなしに、転写されるべき単結晶の層3の部分34が非晶質にされるステップであり、部分34、35が、それぞれ、単結晶の層3の表面部分および埋め込み部分であるステップと、非晶質の部分34が500℃未満の温度で再結晶化されるステップであり、第2の部分35の結晶格子が再結晶化のための種結晶として働くステップとを含む。

(もっと読む)

多層膜構造体及びその形成方法

【課題】新規な多層膜構造体及びその形成方法を提供すること。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

(もっと読む)

半導体基板及びその製造方法

【課題】絶縁層埋め込み型半導体の炭化珪素基板において、電子デバイス作製に不可避である、低抵抗p型不純物層を形成するための工業的な方法を提案すること。

【解決手段】絶縁層埋め込み型半導体炭化珪素基板に、例えば、アルミニウムイオンを注入しp型不純物層を形成させ、次いで熱処理することからなる、p型不純物層を有する絶縁層埋め込み型半導体炭化珪素基板の製造方法。

(もっと読む)

シリコン−オン−インシュレーター構造及びバルク基板に対するSiGeの堆積

【課題】欠陥を最小限としながら、SiGe−オン−インシュレーター構造を製造するため及びシリコン上に歪み緩和SiGe層を製造するための方法を提供する。

【解決手段】アモルファスSiGe層600が、トリシラン及びGeH4からCVDによって、ドーパントの1以下のモノレイヤー上に堆積される。これらのアモルファスSiGe層600は、融解または固相エピタキシー(SPE)プロセスによってシリコン上に再結晶される。融解プロセスは、好ましくは、全体のゲルマニウム含量を希釈するようなゲルマニウムの拡散も引き起こし、そして絶縁体の上層のシリコン500を実質的に消費する。SPEプロセスは、下地のシリコン500中へのゲルマニウムの拡散を用いてまたは用いずに実際され得、従って、SOI及び従来の半導体基板に適用可能である。

(もっと読む)

真性半導体層を備えたウェーハ

【課題】ウェーハを製造するための新規な方法を提供する。

【解決手段】本発明は、ウェーハを製造するための方法に関し、この方法は、半導体基板上にドープト層を設けるステップと、ドープト層上に第1の半導体層を設けるステップと、第1の半導体層上に埋込み酸化物層を設けるステップと、埋込み酸化物層上に第2の半導体層を設けるステップと、を備える。

(もっと読む)

半導体装置

【課題】シリコンなどの基板上に形成した高品質な結晶を有する半導体装置を提供する。

【解決手段】実施形態によれば、GaNを含む下地層と、窒化物半導体を含む機能部と、前記下地層と前記機能部との間に設けられ、AlNを含む層を含む中間層と、を備えた半導体装置が提供される。前記下地層のうちの前記中間層とは反対側の第1領域におけるシリコン原子の濃度は、前記下地層のうちの前記中間層の側の第2領域におけるシリコン原子の濃度よりも高く、前記下地層の前記中間層とは反対側の第1面は、複数の凹部を有する。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】シリコンウェーハとエピタキシャル層との界面における不純物濃度の低下を防止する。

【解決手段】シリコンウェーハを反応炉内で水素ベークする第1の工程(ステップS3)と、反応炉にシリコン原料ガス及びドーパントガスを導入することにより、水素ベークされたシリコンウェーハの表面にエピタキシャル層を形成する第2の工程(ステップS4)とを備える。第1の工程においては、反応炉内にドーパントガスを導入し、外方拡散により低下するシリコンウェーハ表層の不純物濃度を補う。これにより、シリコンウェーハとエピタキシャル層との界面における不純物濃度の低下が抑制されたエピタキシャルウェーハを製造することが可能となる。

(もっと読む)

SOI基板の作製方法

【課題】欠陥の少ない半導体層を得ること、及び信頼性の高い半導体装置を得る。

【解決手段】半導体基板中に、H2O+が水素イオン(H3+)に対して3%以下、好ましくは0.3%以下であるイオンビームを照射することにより、前記半導体基板中に脆化領域を形成し、前記半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、前記半導体基板及び前記ベース基板を貼り合わせ、貼り合わせた前記半導体基板及び前記ベース基板を加熱し、前記脆化領域において分離させることにより、前記ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

SOI基板の作製方法

【課題】膜厚の均一な半導体層を有するSOI基板を得る。

【解決手段】半導体基板の第1の面を研磨して、当該第1の面を平坦化し、当該半導体基板の当該第1の面と反対側の面である第2の面にイオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の第2の面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。当該SOI基板の作製においては、当該半導体層の膜厚の標準偏差をσとし、3σが1.5nm以下である。

(もっと読む)

SOIウェーハの製造方法

【課題】イオン注入剥法により作製されたテラス部にシリコン酸化膜のないSOIウェーハに、渓谷状の段差を発生させることなくエピタキシャル成長を行い、所望のSOI層厚を有するSOIウェーハを製造できる方法を提供することを目的とする

【解決手段】SOIウェーハのSOI層の外周端が、埋め込み酸化膜の外周端よりも外側に位置した構造となるように、該埋め込み酸化膜の外周部を除去する処理を行い、その後、SOIウェーハに水素を含む還元性雰囲気もしくは塩化水素ガスを含む雰囲気で熱処理を行った後、SOI層の表面にエピタキシャル層を形成するSOIウェーハの製造方法。

(もっと読む)

1 - 20 / 257

[ Back to top ]