Fターム[5F152NN16]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 絶縁体 (1,429) | SiO (409) | 石英 (241)

Fターム[5F152NN16]に分類される特許

1 - 20 / 241

装置の作製方法

【課題】剥離前の形状及び特性を保った良好な状態で転置工程を行えるような、剥離工程

を用いて半導体装置及び表示装置を作製できる技術を提供する。よって、より高信頼性の

半導体装置及び表示装置を装置や工程を複雑化することなく、歩留まりよく作製できる技

術を提供することも目的とする。

【解決手段】透光性を有する第1の基板上に光触媒物質を有する有機化合物層を形成し、

光触媒物質を有する有機化合物層上に素子層を形成し、光を第1の基板を通過させて、光

触媒物質を有する有機化合物層に照射し、素子層を前記第1の基板より剥離する。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置、電気光学装置、電力変換装置及び電子機器

【課題】素子特性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】シリコン基板11と、シリコン基板11の表面に形成された炭化シリコン膜12と、炭化シリコン膜12の表面に形成された、開口部13hを有するマスク材13と、開口部13hにおいて露出した炭化シリコン膜12を基点としてエピタキシャル成長された、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14と、単結晶炭化シリコン膜14の表面に形成された半導体素子20と、を含み、マスク材13の上には、単結晶炭化シリコン膜14が会合して形成された会合部12Sbが存在しており、半導体素子20はボディコンタクト領域21を有しており、ボディコンタクト領域21は、シリコン基板11の表面と直交する方向から見て会合部12Sbと重なる位置に配置されている。

(もっと読む)

薄膜製造方法、それを用いた半導体デバイスの製造方法およびそれらに用いられる半導体薄膜部品

【課題】高品質な半導体薄膜を製造する薄膜製造方法を提供する。

【解決手段】薄膜製造方法は、a−Si膜等の半導体薄膜を第1の基板上に堆積する工程S1と、第1の基板をエッチングして第1の基板と半導体薄膜との間に中空部を形成する工程S2と、半導体薄膜に第2の基板を接触させる工程S3と、半導体薄膜に第2の基板を押し付け、または半導体薄膜が溶融する強度を有するレーザ光を半導体薄膜に照射する工程S4と、第1の基板を半導体薄膜から引き離す工程S5とを備える。

(もっと読む)

単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法

【課題】結晶欠陥の少ない高品質なエピタキシャル膜を得ることが可能な単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法を提供する。

【解決手段】シリコン基板11上に単結晶炭化シリコン膜14を形成する単結晶炭化シリコン膜14の製造方法であって、シリコン基板11の表面に炭化シリコン膜12を形成する第1の工程と、炭化シリコン膜12の表面にマスク材13を形成する第2の工程と、マスク材13に開口部13hを形成し、炭化シリコン膜12の一部を露出させる第3の工程と、原料ガスを含むガス雰囲気中でシリコン基板11を加熱し、炭化シリコン膜12を基点として単結晶炭化シリコンをエピタキシャル成長させ、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14を形成する第4の工程と、を含み、原料ガスを含むガス雰囲気の圧力は、5.0×10−4Pa以上かつ0.5Pa以下である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

窒化物半導体結晶層の製造方法及び窒化物半導体結晶層

【課題】より良質な窒化物半導体結晶層を製造する方法及び窒化物半導体結晶層を提供する。

【解決手段】実施形態によれば、表面にシリコン酸化膜が形成された基体の上に設けられた20μm以下の厚さのシリコン結晶層の上に、1μm以上の厚さの窒化物半導体結晶層を形成する。シリコン結晶層の上に、窒化物半導体結晶層のうちの第1の部分を形成した後、第1の部分よりも高い温度で第2の部分を形成する。シリコン結晶層は、シリコン結晶層の層面に対して平行な面内において、0.5mm以上、10mm以下の特性長さを持つ島状に区分されている。区分されたシリコン結晶層のそれぞれの上に選択的に互いに離間した複数の窒化物半導体結晶層を形成する。シリコン結晶層の少なくとも一部を窒化物半導体結晶層に取り込ませ、シリコン結晶層の厚さを減少させる。

(もっと読む)

GaN薄膜貼り合わせ基板およびその製造方法、ならびにGaN系高電子移動度トランジスタおよびその製造方法

【課題】バッファリーク電流およびゲートリーク電流が抑制された高性能のHEMTを提供する。

【解決手段】本GaN薄膜貼り合わせ基板の製造方法は、GaNバルク結晶10の主表面から0.1μm以上100μm以下の深さの面10iへの平均注入量が1×1014cm-2以上3×1017cm-2以下の水素イオン注入工程と、水素イオン注入されたGaNバルク結晶10の上記主表面へのGaNと化学組成が異なる異組成基板20の貼り合わせ工程と、GaNバルク結晶10の熱処理によりGaNバルク結晶10を水素イオンが注入された深さの面10iにおいて分離することによる異組成基板20上に貼り合わされたGaN薄膜10aの形成工程と、を含む。GaN系HEMTの製造方法は、上記GaN薄膜貼り合わせ基板1のGaN薄膜10a上への少なくとも1層のGaN系半導体層30の成長工程を含む。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】より安定した電気的特性の酸化インジウム亜鉛でなる酸化物半導体膜を提供する。また、当該酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】酸化インジウム亜鉛でなる酸化物半導体膜において、当該酸化物半導体膜は、a−b面が酸化物半導体膜表面に概略平行である六方晶の結晶構造と、a−b面が該酸化物半導体膜表面に概略平行である菱面体晶の結晶構造と、を有する酸化物半導体膜である。

(もっと読む)

半導体材料、半導体材料の製造方法及び半導体素子

【課題】pn接合のI−V特性を向上させる半導体材料を提供すること。

【解決手段】本発明に係る半導体材料は、酸化亜鉛の結晶を含有する粒子を備え、酸化亜鉛の結晶子の大きさが5〜50nmであり、酸化亜鉛の結晶における窒素の含有率が500〜10000質量ppmである。

(もっと読む)

SOI基板、およびSOI基板の作製方法

【課題】単結晶シリコン膜などの半導体膜が、支持基板から剥がれることを防止するSOI基板の作製方法を提供する。また、当該方法を用いることで、SOI基板作製における歩留まりを向上させ、生産コストを削減する。

【解決手段】半導体基板に絶縁膜を形成し、加速されたイオンを半導体基板に照射することにより、半導体基板中に脆化領域を形成し、半導体基板と支持基板とを、絶縁膜を介して貼り合わせ、脆化領域において、半導体基板を分離して、支持基板上に絶縁膜を介して半導体膜を形成し、半導体膜上にマスクを形成し、半導体膜の一部及び絶縁膜の一部をエッチングすることにより、半導体膜の周端部が、絶縁膜の周端部の内側に位置するように、半導体膜及び絶縁膜を形成する、SOI基板の作製方法である。

(もっと読む)

SOI基板の作製方法

【課題】欠陥の少ない半導体層を得ること、及び信頼性の高い半導体装置を得る。

【解決手段】半導体基板中に、H2O+が水素イオン(H3+)に対して3%以下、好ましくは0.3%以下であるイオンビームを照射することにより、前記半導体基板中に脆化領域を形成し、前記半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、前記半導体基板及び前記ベース基板を貼り合わせ、貼り合わせた前記半導体基板及び前記ベース基板を加熱し、前記脆化領域において分離させることにより、前記ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけられた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとして機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面を有するディスプレイを実現するものである。

(もっと読む)

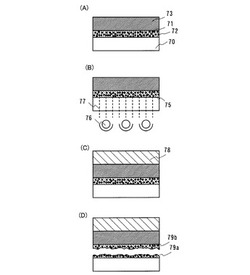

発光装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 水分に起因するTFT特性の変化を抑制した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタは、基板上に、少なくともゲート電極、ゲート絶縁膜、活性層、ソース電極、およびドレイン電極が設けられ、活性層上にソース電極およびドレイン電極が設けられたものである。活性層は、アモルファス酸化物半導体により構成されており、ゲート絶縁膜内に存在する第1の水分量が活性層に存在する第2の水分量よりも少ない。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】絶縁表面上に膜厚が1nm以上10nm以下の第1の材料膜(六方晶の結晶構造を有する膜)を形成し、第1の材料膜を核として、六方晶の結晶構造を有する第2の材料膜(結晶性酸化物半導体膜)を形成し、第1の材料膜と第2の材料膜の積層を形成する。第1の材料膜としては、ウルツ鉱型結晶構造を有する材料膜(例えば窒化ガリウム、或いは窒化アルミニウム)、或いはコランダム型結晶構造を有する材料膜(α−Al2O3、α−Ga2O3、In2O3、Ti2O3、V2O3、Cr2O3、或いはα−Fe2O3)を用いる。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

1 - 20 / 241

[ Back to top ]