Fターム[5F152NP09]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 3−5族 (413) | 窒化物 (252)

Fターム[5F152NP09]に分類される特許

141 - 160 / 252

窒化物半導体厚膜基板

【課題】複数の窒化物半導体層を含む発光素子構造を成長させるために望ましい窒化物半導体厚膜基板を提供し、ひいてはその基板を用いて優れた特性を有する窒化物半導体発光装置を提供する。

【解決手段】複数の窒化物半導体層を含む発光素子構造を成長させるための窒化物半導体厚膜基板であって、基板は対向する第1と第2の主面を有し、基板の第1主面は3×1018cm-3以上1×1019cm-3以下の高不純物濃度の第1の層領域で形成されており、基板は3×1018cm-3以下1×1017cm-3以上でかつ第1層領域より低い低不純物濃度の第2の層領域をも少なくとも含み、基板の第1主面はその上に前記発光素子構造を成長させるための面であり、発光素子構造の形成後に第1主面の側で部分的に露出される基板の領域が電極を形成するための領域として使用されることを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】III 族窒化物半導体からなる半導体装置の製造方法において、p型のIII 族窒化物半導体の正孔濃度を減少しないようにすること。

【解決手段】III 族窒化物半導体からなる半導体素子の製造方法であって、MgをドープしたIII 族窒化物半導体層の形成後に、400度以上の温度での熱処理工程を複数有した半導体素子の製造方法において、最終以外の400度以上の温度での熱処理工程では、アンモニア雰囲気中において熱処理を行い、最終の400度以上の温度での熱処理工程では、窒素雰囲気中において熱処理を行う。このように熱処理を行えば、p型のIII 族窒化物半導体層の正孔濃度を減少させずに半導体素子を製造することができる。

(もっと読む)

高表面品質GaNウェーハおよびその製造方法

【課題】優れた表面品質をGa側にて有するAlxGayInzN半導体ウェーハおよびそのようなウェーハの製造方法を実現する。

【解決手段】ウェーハのGa側における10×10μm2面積内で1nm未満の根二乗平均表面粗さを特徴とする、AlxGayInzN(式中、0<y≦1およびx+y+z=1)を含む高品質ウェーハ。このようなウェーハは、例えばシリカまたはアルミナなどの研磨粒子と酸または塩基とを含む化学的機械研磨(CMP)スラリーを用いて、そのGa側にてCMPに付される。このような高品質AlxGayInzNウェーハの製造方法はラッピング工程、機械研磨工程、およびその表面品質を更に高めるための熱アニールまたは化学エッチングによるウェーハの内部応力を低下させる工程を含んでよい。このCMP方法はAlxGayInzNウェーハのGa側における結晶欠陥を強調するために有用に適用される。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】放熱性が極めて良好で、かつ、結晶性が良好なGaN系材料を用いたデバイス、および、その製造方法を提供する。

【解決手段】窒化物半導体装置の製造方法であって、シリコン基板60の表面にダイヤモンド層61を気相成長させるステップと、ダイヤモンド層61の表面にSOI基板62を圧着するステップと、SOI基板62を薄層化する薄層化ステップと、薄層化されたSOI基板62上に、GaN層をエピタキシャル成長させるステップと、シリコン基板60を除去するステップと、シリコン基板60より熱伝導率の大きい材料をダイヤモンド層61の裏面に圧着するステップとを含み、SOI基板62は、最表面層621とシリコン酸化層622とを有し、前記薄層化ステップにおいて、選択的にシリコン酸化層622までを除去し最表面層621のみを残してSOI基板62を薄層化する。

(もっと読む)

化合物半導体基板

【課題】ラマン分光法を用いた簡易な応力測定方法を見出し、これに基づいて、GaN活性層を有する化合物半導体基板において、バッファ層における応力を制御し、全体として応力フリーの化合物半導体基板を提供する。

【解決手段】厚さ100〜1000μmの六方晶SiC、単結晶Si、単結晶Si上に立方晶SiC層が形成されたもののうちのいずれかからなる台基板1上に、バッファ層2、厚さ0.5〜5μmのGaN活性層3を順次積層し、前記バッファ層2を、厚さ3〜250nmのAlxGa1-xN単結晶層(0.5<x≦1)2a‐1の上に、厚さ3〜250nmのAlyGa1-yN単結晶層(0.2≦y≦0.3)2b‐1が形成され、さらに、厚さ3〜250nmのAlxGa1-xN単結晶層2a‐nおよび厚さ3〜250nmのAlzGa1-zN単結晶層(0≦z<0.5)2c‐nの2層を1組としたものが1〜500組積層されている構成とする。

(もっと読む)

化合物半導体基板

【課題】化合物半導体単結晶層に残留するキャリアを抑制することによって、高速および高耐電圧デバイスに好適な窒化物半導体単結晶層を有する化合物半導体基板を提供する。

【解決手段】Si単結晶基板1上に、B,Al,V,Ni,Fe,Mg,Pt,Cr,Mo,W,Ta,Nb,Sc,Ti,Au,Co,Cuのうちの少なくともいずれか1種の不純物元素を1014〜1021/cm3含む、厚さ0.05〜2μmの3C−SiC単結晶バッファー層2と、C,V,Ni,Fe,Mg,Pt,Cr,Mo,W,Ta,Nb,Sc,Ti,Au,Co,Cuのうちの少なくともいずれか1種の不純物元素を1014〜1021/cm3含む、厚さ0.05〜5μmのGaN単結晶層3とが順次積層された構成とする。

(もっと読む)

窒化物半導体の製造方法

【課題】結晶欠陥の発生を低減すると共に反りの発生を防止することにより、品質と生産性に優れた窒化物半導体の製造方法を提供する。

【解決手段】GaNからなる基板1上に第一の窒化物半導体層10を成長させ、その第一の窒化物半導体層10に多数の微細なボイド2aを有する多孔質層2を形成した後、その上に第二の窒化物半導体層を成長させ、上記基板1或いは上記基板1及びボイドを有する多孔質層2を剥離する窒化物半導体の製造方法。

(もっと読む)

相分離が抑制されたIII族窒化物材料系を用いた半導体構造及び光検出器

【課題】レーザダイオード、トランジスタ、光検出器などの半導体構造に使用され、相分離を抑制または解消するとともに発光効率を向上させるIII族窒化物4元及び5元材料系並びに方法を提供する。

【解決手段】典型的な実施形態では、半導体構造は、ほぼ相分離なく形成された第1導電型のBAlGaN材料系を用いた4元材料層と、ほぼ相分離のないBAlGaN材料系を用いた4元材料活性層と、ほぼ相分離なく形成された逆導電型のBAlGaN材料系を用いた別の4元材料層を備えている。

(もっと読む)

半導体素子およびその製造方法

【課題】Nを含む活性層または受光層と、Pを含む半導体層とを備える半導体素子を、量産ベースで製造することができる半導体素子およびその製造方法を提供する。

【解決手段】基板上に、窒素を含むIII−V族化合物半導体層を、MBE法により成長する工程と、その窒素含有半導体層上に、燐を含むIII−V族化合物半導体層を、塩化物気相成長法により成長する工程とを備えることを特徴とする。

(もっと読む)

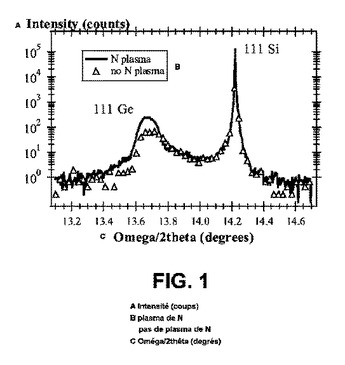

基板上に結晶ゲルマニウム層を形成する方法

本発明は、結晶表面を有する結晶ベース基板の上に結晶ゲルマニウム層を形成する方法を提供する。この方法は、ベース基板を洗浄して表面から汚染物および/または自然酸化物を除去する工程と、水素プラズマ、H2フラックス、またはGeH4の分解で得られる水素のような水素源および/またはN2、He、Ne、Ar、Kr、Xe、Rn、またはそれらの混合物のような非反応性ガス源にベース基板を露出させながら、ベース基板の表面上にアモルファスゲルマニウム層を形成する工程と、ベース基板をアニールしてアモルファスゲルマニウム層を結晶化して、結晶ゲルマニウム層を形成する工程と、を含む。また、この方法は、本発明の具体例にかかる方法を用いて光起電セルまたは光分解セルを形成する方法、またはCMOSデバイスを形成する方法、および本発明の具体例にかかる方法で形成した結晶ゲルマニウム層を含む基板を提供する。  (もっと読む)

(もっと読む)

窒化物半導体素子の製造方法

【課題】結晶性の良い窒化物半導体よりなる窒化物半導体基板を用い裏面に電極を形成した発光素子、受光素子等の窒化物半導体素子を提供する。

【解決手段】窒化物半導体と異なる材料よりなる基板の上に、窒化物半導体を100μm以上の膜厚で成長させ、前記基板を除去することによって得られた窒化物半導体基板であり、該窒化物半導体基板の表面の凹凸差が±1μm以下になるまで表面研磨した研磨面に成長される。好ましくは、前記表面の凹凸差が±0.5μm以下である。前記窒化物半導体基板はn型不純物がドープされている。

(もっと読む)

区割りされた基板に作成された半導体デバイスに対する高品質境界を取得するための方法

個別の多層構造(114)に対する高品質境界を取得するためのプロセスであって、該個別の多層構造は溝区割り基板に作成される、プロセスが提供される。プロセスは以下のステップ、すなわち、溝区割り基板を準備するステップであって、基板表面は、孤立した堆積プラットフォーム(108)の配列に区割りされ、該孤立した堆積プラットフォームは、溝(102)の配列によって分離されている、ステップと、多層構造(114)を形成するステップであって、該多層構造は、堆積プラットフォーム(108)のうちの1つの上に、第1のドープ層(204)、活性層(206)、および第2のドープ層(208)を備えている、ステップと、多層構造(114)の側壁を除去するステップとを包含する。多層構造(114)の側壁を除去することによって取得された高品質境界を有する半導体デバイスも提供される。  (もっと読む)

(もっと読む)

窒化物半導体単結晶

【課題】Si基板上に、半極性面である(10-1m)面(m:自然数)の窒化物半導体膜が厚さ1μm以上で形成され、発光デバイスにも好適に用いることができる窒化物半導体単結晶を提供する。

【解決手段】Si(100)に対して、<100>から<110>方向へのオフカット角度が1〜35°であるSi基板1上に、SiCまたはBPのいずれか1種以上からなるバッファー層2a(2b)およびAlNバッファー層3を介して、GaN(10-1m)、AlN(10-1m)またはInN(10-1m)からなる単結晶膜4、あるいはまた、GaN(10-1m)およびAlN(10-1m)の超格子構造を形成する。

(もっと読む)

シリコン基板及びその製造方法

【課題】半導体素子を形成するためにエピタキシャル成長された半導体層による湾曲を抑制したシリコン基板を提供すること。

【解決手段】シリコン基板1において、窒化物系化合物半導体層2の成長によって凹状に反る方向に加わる圧縮応力と拮抗する応力が、シリコン基板1の窒素不純物濃度分布に対応した密度またはサイズの分布を有する酸素析出物の膨張力によって与えられたことを特徴とする、実質的に平坦な主面を有するシリコン基板、およびその製造方法。

(もっと読む)

半導体デバイス

【課題】低コスト及び簡素な構成で、窒化物化合物半導体層と基板との間の直列抵抗を低減できる半導体デバイスを提供すること。

【解決手段】半導体デバイスは、p型シリコン基板1と、p型シリコン基板1上に設けられ、シリコンに対してp型の不純物として機能する元素を含むバッファ層9と、バッファ層9上に設けられた窒化物化合物半導体層3と、窒化物化合物半導体層3上に設けられた第1の電極4と、p型シリコン基板1下面に設けられた第2の電極8とを有する。

(もっと読む)

窒化物半導体積層構造の形成方法および窒化物半導体素子の製造方法

【課題】パワーデバイスなどへの適用に適したIII族窒化物半導体を用いた窒化物半導体積層構造の形成方法、およびこの形成方法により形成される窒化物半導体積層構造部を有する窒化物半導体素子の製造方法を提供すること。

【解決手段】III族窒化物半導体からなる窒化物半導体積層構造の形成工程において、キャリヤガスをH2とするMOCVD法によって、まず、ウエハの上にn型GaN層(第1層)およびMgを含むp型GaN層(第2層)が形成される。次いで、このp型GaN層(第2層)に対してp型化アニール処理をせずに、p型GaN層(第2層)の上に、さらにn型GaN層(第3層)およびp型GaN層(第4層)が形成される。このように、n型GaN層(第1層)およびn型GaN層(第3層)に挟まれたp型GaN層(第2層)に含まれるMg濃度とH2濃度とを比較すると、Mg濃度の方が大きい値となっている。

(もっと読む)

半導体ウエーハ及び半導体素子及び製造方法

【課題】 シリコン基板上に窒化物半導体領域を設けると、半導体ウエーハに反りが発生する。

【解決手段】 シリコン基板2の上に窒化物半導体から成るバッファ領域3を介してHEMT用の窒化物半導体から成る主半導体領域4を設ける。前記バッファ領域4を、第1の多層構造バッファ領域5と第2の多層構造バッファ領域8とで構成する。第1の多層構造バッファ領域5を複数のサブ多層構造バッファ領域6と複数の単層構造バッファ領域7で構成する。サブ多層構造バッファ領域6を、交互に配置された複数の第1及び第2の層で構成する。第1の層をアルミニウムを第1の割合で含む窒化物半導体で形成する。第2の層をアルミニウムを含まない又は前記第1の割合よりも小さい第2の割合で含む窒化物半導体で形成する。第2の多層構造バッファ領域8を第3及び第4の層で構成する。第3の層のアルミニウム割合を第1の割合よりも低くする。

(もっと読む)

中間層構造を有する窒化物半導体構造、及び中間層構造を有する窒化物半導体構造を製造する方法

半導体構造は、窒化物半導体材料の第1の層、前記窒化物半導体材料の第1の層上の実質的に歪みのない窒化物中間層、及び前記窒化物中間層上の窒化物半導体材料の第2の層を含む。前記窒化物中間層は第1の格子定数を有し、アルミニウム及びガリウムを含むこと、並びにn型ドーパントで導電的にドープすることができる。前記第1の層及び前記第2の層は、全体として少なくとも約0.5μmの厚さを有する。前記窒化物半導体材料は、前記第1の層が前記窒化物中間層の一方の側において、前記第2の層が前記窒化物中間層の他方の側で受け得るより大きい引っ張り歪みを受けることができるような、第2の格子定数を有することが可能である。  (もっと読む)

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】パワーデバイスなどへの適用に適したIII族窒化物半導体素子およびその製造方法を提供すること。

【解決手段】この電界効果トランジスタにおける窒化物半導体積層構造部5には、n型GaN層6、p型GaN層7およびn型GaN層8に跨る壁面16を側面とするメサ状積層部15が形成されている。メサ状積層部15の壁面16には、ゲート絶縁膜9が形成され、このゲート絶縁膜9上にはゲート電極10が形成されている。また、n型GaN層6(引き出し部19)にはドレイン電極12が形成され、n型GaN層8の上面にはソース電極11が形成されている。そして、メサ状積層部15は、窒化物半導体積層構造部5に形成された高転位領域18および低転位領域17のうち、低転位領域17に形成されている。

(もっと読む)

半導体素子

【課題】しきい値電圧を増大させることなくバッファ層を高抵抗化して素子を高耐圧化できること。

【解決手段】電界効果トランジスタ100は、基板1上にバッファ層2,3、半導体動作層4、ゲート絶縁膜5Gaおよびゲート電極5Gbを順次積層して備え、バッファ層3内にあってこのバッファ層3の積層面に平行な所定面内の転位密度は、この転位密度に対するバッファ層3の体積抵抗率が極大値近傍となる密度値とされ、具体敵意は2.0×108cm-2以上、7.0×1010cm-2以下とされている。

(もっと読む)

141 - 160 / 252

[ Back to top ]