Fターム[5F152NP09]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 3−5族 (413) | 窒化物 (252)

Fターム[5F152NP09]に分類される特許

81 - 100 / 252

半導体材料ドーピング

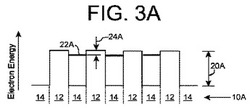

量子井戸及び隣接するバリアを含む構造を設計し及び/又は製造するための解決法が提供される。量子井戸と隣接するバリアとの間の目標バンド不連続性が、量子井戸及び/又はバリア用のドーパントの活性化エネルギーと一致するように選択される。例えば、目標バレンスバンド不連続性は、隣接するバリア中のドーパントのドーパントエネルギーレベルが、量子井戸に関するバレンスエネルギーバンド端及び/又は量子井戸に関するバレンスエネルギーバンド中の自由キャリアについての基底状態エネルギーと一致するように選択されることがある。量子井戸及び隣接するバリアは、実際のバンド不連続性が目標バンド不連続性に対応するように形成されることがある。 (もっと読む)

ガラスボンディング層を使用して半導体構造及び半導体素子を製造する方法並びにかかる方法によって形成した半導体構造及び半導体素子

半導体構造及び半導体素子を製造する方法は、ガラスを使用して基板にシード構造をボンディングするステップを含む。シード構造は、半導体材料の結晶を含むことができる。ガラスを使用して基板にボンディングされたシード構造の熱処理を利用して、シード構造内部の歪状態を制御することができる。シード構造を、室温において圧縮歪の状態に置くことができる。ガラスにボンディングされたシード構造を、半導体材料の成長用に使用することができる、又は、さらなる方法では、シード構造を、ガラスを使用して第1の基板にボンディングすることができ、熱処理してシード構造内部の歪状態を制御することができ、第2の基板を、非ガラス質材料を使用してシード構造の反対側の面にボンディングすることができる。 (もっと読む)

化合物半導体基板

【課題】基板の反りの低減とデバイスの高速性を高いレベルで実現することのできる化合物半導体基板を提供する。

【解決手段】

Si単結晶の基板と、基板の主面上に形成された窒化物半導体の中間層と、中間層の主面上に形成された窒化物半導体の化合物半導体層からなり、基板の酸素濃度が0.2×1018atoms/cm3以上1.4×1018atoms/cm3以下であり、抵抗値が1000Ωcm以上であり、前記中間層と前記化合物半導体層を合計した、主面と垂直方向の膜厚が450nm以上4500nm以下であることを特徴とする化合物半導体基板。

(もっと読む)

半導体素子の製造方法

【課題】 半導体層のエッチング時間の短縮化が望まれている。

【解決手段】 第1の膜及び半導体膜がこの順番に形成された積層基板の前記半導体膜の上に、マスクパターンを形成する。マスクパターンをエッチングマスクとして、半導体膜をエッチングすることにより、凹部を形成するとともに、凹部の底面の一部の領域に第1の膜が露出し、他の領域には、半導体膜の残渣が残っている状態でエッチングを停止させる。凹部の底面に露出した第1の膜を厚さ方向及び横方向にエッチングすることにより、残渣の下に空洞を形成する。積層基板を浸漬させた液体に超音波を印加することにより、空洞の上に残留している残渣を積層基板から脱離させる。

(もっと読む)

半導体素子およびその製造方法

【課題】基板の表面上に積層される半導体素子層に発生する所定の方向の歪みを低減することが可能な半導体素子を提供する。

【解決手段】この半導体素子1は、第1方向(A方向)および第2方向(B方向)に平行な主表面を有するとともに第1方向に沿って延びる段差部2aが形成された窒化物系半導体からなる基板2と、基板2上に形成され、窒化物系半導体からなる下地層3、第1半導体層4および第2半導体層5とを備える。そして、下地層3および第2半導体層5の無歪みの状態における第2方向の格子定数は、それぞれ、基板2の無歪みの状態における第2方向の格子定数よりも大きく、下地層3および第2半導体層5の基板2の主表面上に形成された状態における第2方向の格子定数は、それぞれ、基板2の第2方向の格子定数よりも大きい。

(もっと読む)

半導体デバイス形成方法

基板ウェーハの裏側及び縁部断面をシールするためのシステム及び方法である。第1の方法の実施例によれば、第1導電型のシリコンウェーハにアクセスする。第1導電型のエピタキシャル層をシリコンウェーハの前面上で成長する。エピタキシャル層をインプラントし、逆の導電型の領域を形成する。成長及びインプラントを繰り返し、逆の導電型の垂直カラムを形成する。ウェーハに更にインプラントを行い、垂直カラムと垂直方向で整合した逆の導電型の領域を形成する。  (もっと読む)

(もっと読む)

横方向を電流導通方向とする電子デバイス用エピタキシャル基板およびその製造方法

【課題】HEMTのシート抵抗を非接触で精度良く測定することができる横方向を電流導通方向とする電子デバイス用エピタキシャル基板およびこの電子デバイス用エピタキシャル基板を効率よく製造する方法を提供する。

【解決手段】高抵抗Si単結晶基板の一方の面上に、不純物拡散抑制層を形成する工程と、前記高抵抗Si単結晶基板の他方の面上に、絶縁層としてのバッファを形成する工程と、該バッファ上に、複数層のIII族窒化物層をエピタキシャル成長させて主積層体を形成してエピタキシャル基板を作製する工程と、該エピタキシャル基板の主積層体の抵抗を非接触で測定する工程とを具えることを特徴とする。

(もっと読む)

化合物半導体エピタキシャルウェハおよびその製造方法

【課題】窒化物半導体からなる電子デバイスにおいてバッファ層に生じるリーク電流を抑制できる窒化物半導体エピタキシャルウェハを提供する。

【解決手段】化合物半導体エピタキシャルウェハは、単結晶基板101と、前記単結晶基板上にエピタキシャル成長された核生成層102と、前記核生成層の上に成長された窒化物半導体の単層あるいは複数層からなるバッファ層103と、前記バッファ層の上にエピタキシャル成長された窒化物半導体のチャネル層104と、前記チャネル層の上にエピタキシャル成長された窒化物半導体のキャリヤ供給層105とから成り、かつ前記核生成層からチャネル層までの合計の膜厚が1μm以下であること。

(もっと読む)

Znがドープされた3B族窒化物結晶、その製法及び電子デバイス

【課題】高抵抗且つ低転位密度のZnドープ3B族窒化物結晶を提供する。

【解決手段】本発明のZnドープ3B族窒化物結晶は、比抵抗が1×102Ω・cm以上、3B族窒化物結晶中のZn濃度が1.0×1018atoms/cm3以上2×1019atoms/cm3以下、エッチピット密度が5×106/cm2以下のものである。この結晶は、液相法(Naフラックス法)により得ることができる。

(もっと読む)

センサ、半導体基板、および半導体基板の製造方法

【課題】効率よく光電変換ができる光吸収体を有する半導体基板、半導体基板の製造方法、および当該半導体基板を含む光センサを提供する。

【解決手段】シリコンを含むベース基板と、ベース基板上方に設けられたシード体と、シード体に格子整合または擬格子整合し、光または熱を吸収してキャリアを生成する3−5族化合物半導体からなる光熱吸収体とを備え、光熱吸収体が、光熱吸収体に入射する入射光または光熱吸収体に加わる熱に応じて電気信号を出力するセンサを提供する。また、シリコンを含むベース基板と、ベース基板の上方に形成され、ベース基板の表面を露出する開口を有し、結晶成長を阻害する阻害体と、開口の内部に設けられたシード体と、シード体に格子整合または擬格子整合し、光または熱を吸収してキャリアを生成する3−5族化合物半導体からなる光熱吸収体とを備える半導体基板を提供する。

(もっと読む)

異種基板、それを利用した窒化物系半導体素子及びその製造方法

本発明は、異種基板と、それを利用した窒化物系半導体素子及びその製造方法に関し、異種基板の無極性または半極性面に結晶成長モードを調節し、高品質の無極性または半極性窒化物層を形成するためのものである。無極性または半極性面のうち1つを有するベース基板を準備し、用意したベース基板の面に窒化物系結晶成長核層を形成する。結晶成長核層の上に第1バッファー層を成長させ、且つ、水平方向に比べて垂直方向にさらに速く成長させる。第1バッファー層上に水平成長層を成長させ、且つ、垂直方向に比べて水平方向にさらに速く成長させる。また、水平成長層上に第2バッファー層を成長させる。この際、第1バッファー層上の水平成長層と第2バッファー層との間に複数の孔を有する窒化シリコン層をさらに形成することができる。  (もっと読む)

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分がAlを含むIII族窒化物半導体からなる結晶成長基板と、前記表面部分上に形成されたスカンジウム窒化物膜とを具えることを特徴とする。

(もっと読む)

III族窒化物半導体層貼り合わせ基板およびその製造方法、ならびにIII族窒化物半導体デバイス

【課題】光の取り出し効率が高い半導体デバイスが得られる安価なIII族窒化物半導体層貼り合わせ基板およびその製造方法ならびにIII族窒化物半導体デバイスを提供する。

【解決手段】本III族窒化物半導体層貼り合わせ基板1は、III族窒化物半導体層20aと、III族窒化物半導体層20aと化学組成が異なる基礎基板10と、が貼り合わせられた基板であって、III族窒化物半導体層20aは、基礎基板10と接合する主面20nを有し主面20nに平行な2次元方向に屈折率が周期的に変化するフォトニック結晶構造層20pを含む。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置

【課題】低コストの立方晶炭化ケイ素(3C−SiC)単結晶薄膜を得るための立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置を提供する。

【解決手段】立方晶炭化ケイ素単結晶薄膜の製造方法において、基板101の表面に犠牲層102を形成する第1の工程と、犠牲層の表面に少なくとも表面層が立方晶構造である立方晶半導体層103を形成する第2の工程と、立方晶半導体層の表面に立方晶炭化ケイ素単結晶層104を形成する第3の工程と、犠牲層をエッチング除去して、立方晶半導体層と立方晶炭化ケイ素単結晶層との積層体を剥離する第4の工程とを備える。

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分がAlを含むIII族窒化物半導体からなる結晶成長基板と、前記表面部分上に形成されたスカンジウム窒化物膜とを具えることを特徴とする。

(もっと読む)

GaN系化合物半導体基板とその製造方法

【課題】表層に到達する転位の密度を、簡便かつ効果的に低減することができるGaN系化合物半導体基板とその製造方法を提供する。

【解決手段】基板10と、基板10の主面上に形成される緩衝層20と、緩衝層20上に形成されるGaN系半導体単結晶の活性層30とを備え、基板10の主面に平行な任意の方向に屈曲する屈曲転位が活性層30内における緩衝層20と活性層30との界面近傍に存在することを特徴とするGaN系半導体基板。

(もっと読む)

半導体素子

【課題】バッファ層を介した電極間のリーク電流を抑制した半導体素子を提供する。

【解決手段】本半導体素子は、基板10に形成された第1のAlXGa1−XN層14a及び第1のAlXGa1−XN層14aよりAl組成Xの大きい第2のAlXGa1−XN層14bが交互に積層して形成された超格子バッファ層14を有する。そして、第1のAlXGa1−XN層14a及び第2のAlXGa1−XN層14bのAl組成Xは共に0.3より大きく、かつ第1のAlXGa1−XN層14a及び第2のAlXGa1−XN層14bのAl組成Xの差は0より大きく0.6より小さい。この構成によれば、バッファ層を介したリーク電流を低減することができる。

(もっと読む)

窒化物系化合物半導体層を支持基板上に有する基板生産物を製造する方法、及び半導体デバイスの製造方法

【課題】窒化物系化合物半導体層を支持基板上に有する基板生産物を製造するために、異種基板同士を貼り合わせる工程を含む方法において、所望の半導体デバイスに適した基板を選択可能な方法を提供する。

【解決手段】窒化物系化合物半導体から成る第1の基板10の表層と、窒化物系化合物半導体とは異なる材料から成る第2の基板20の表面20aとを互いに接合させる。第1の基板10のうち表層を含む部分を層状に残して他の部分を除去することにより、窒化物系化合物半導体層30を第2の基板20上に形成する。窒化物系化合物半導体層30の表面30aと、窒化物系化合物半導体層30及び第2の基板20の双方と異なる材料から成る支持基板40の表面40aとを互いに接合させたのち、第2の基板20を窒化物系化合物半導体層30から剥離させる。

(もっと読む)

ダイヤモンド薄膜及びその製造方法

【課題】積層欠陥及び貫通転位の密度が十分に低いダイヤモンド薄膜構造とその製造方法を提供する。

【解決手段】基板101と、基板101の主方位面の一部を覆うマスク材102と、基板101の主方位面の表面からエピタキシャル成長するダイヤモンド薄膜103とで構成されるダイヤモンド薄膜構造であって、ダイヤモンド薄膜103は、マスク材102の上に形成され、ダイヤモンド薄膜103の結晶方位は基板101の結晶方位とそろっている。ダイヤモンド基板101に存在する貫通転位104aは、マスク材102で覆われていない部分のダイヤモンド基板101の主方位面を介してダイヤモンド薄膜103まで貫通するが、貫通転位104bは、マスク材102によってダイヤモンド薄膜103への伝播が遮られるため、ダイヤモンド薄膜103の貫通転位密度は低下し、結晶性が向上する。

(もっと読む)

81 - 100 / 252

[ Back to top ]