Fターム[5F152NQ09]の内容

再結晶化技術 (53,633) | 動作層、活性層、素子構成層の材料 (2,604) | 半導体 (2,300) | 3−5族 (966) | 窒化物 (383)

Fターム[5F152NQ09]に分類される特許

41 - 60 / 383

半導体装置の製造方法

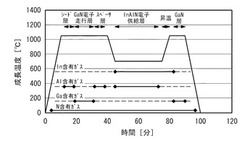

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18を形成した後、In含有ガスを供給しつつ、基板10を昇温させる工程と、昇温が終了した後、InAlN電子供給層18上にGaN層20を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

窒化物半導体結晶層の製造方法及び窒化物半導体結晶層

【課題】より良質な窒化物半導体結晶層を製造する方法及び窒化物半導体結晶層を提供する。

【解決手段】実施形態によれば、表面にシリコン酸化膜が形成された基体の上に設けられた20μm以下の厚さのシリコン結晶層の上に、1μm以上の厚さの窒化物半導体結晶層を形成する。シリコン結晶層の上に、窒化物半導体結晶層のうちの第1の部分を形成した後、第1の部分よりも高い温度で第2の部分を形成する。シリコン結晶層は、シリコン結晶層の層面に対して平行な面内において、0.5mm以上、10mm以下の特性長さを持つ島状に区分されている。区分されたシリコン結晶層のそれぞれの上に選択的に互いに離間した複数の窒化物半導体結晶層を形成する。シリコン結晶層の少なくとも一部を窒化物半導体結晶層に取り込ませ、シリコン結晶層の厚さを減少させる。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

半導体素子及びその製造方法

【課題】転位密度を低減させるバッファ層を有する半導体素子を提供する。

【解決手段】基板と、基板の上方に形成されたバッファ領域と、バッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、バッファ領域は、第1の格子定数を有する第1半導体層と、第1の格子定数と異なる第2の格子定数を有する第2半導体層と、第1の格子定数と第2の格子定数との間の第3の格子定数を有する第3半導体層とが順に積層した複合層を少なくとも一層有する半導体素子。

(もっと読む)

GaN薄膜貼り合わせ基板およびその製造方法、ならびにGaN系高電子移動度トランジスタおよびその製造方法

【課題】バッファリーク電流およびゲートリーク電流が抑制された高性能のHEMTを提供する。

【解決手段】本GaN薄膜貼り合わせ基板の製造方法は、GaNバルク結晶10の主表面から0.1μm以上100μm以下の深さの面10iへの平均注入量が1×1014cm-2以上3×1017cm-2以下の水素イオン注入工程と、水素イオン注入されたGaNバルク結晶10の上記主表面へのGaNと化学組成が異なる異組成基板20の貼り合わせ工程と、GaNバルク結晶10の熱処理によりGaNバルク結晶10を水素イオンが注入された深さの面10iにおいて分離することによる異組成基板20上に貼り合わされたGaN薄膜10aの形成工程と、を含む。GaN系HEMTの製造方法は、上記GaN薄膜貼り合わせ基板1のGaN薄膜10a上への少なくとも1層のGaN系半導体層30の成長工程を含む。

(もっと読む)

半導体素子及びその製造方法

【課題】厚膜化が可能で、反りが小さく、かつリーク電流が小さい半導体素子を提供する。

【解決手段】基板と、基板の上方に形成された第1のバッファ領域と、第1のバッファ領域上に形成された第2のバッファ領域と、第2のバッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、第1のバッファ領域は、第1半導体層と、第2半導体層とが順に積層した複合層を少なくとも一層有し、第2のバッファ領域は、第3半導体層と、第4半導体層と、第5半導体層とが順に積層した複合層を少なくとも一層有し、第4半導体層の格子定数は、第3半導体層と第5半導体層の間の格子定数を有する半導体素子。

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

【課題】ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する。

【解決手段】SiC層10にSiO2層を形成し、次いで、熱伝導率を高めるためにダイアモンド層11を形成する。そして、SiC層10の厚さを低減し、ダイアモンド層11及びSiC層10の向きを逆にしてダイアモンド11を基板とする。次いで、SiC層10上に、バッファ層16、ヘテロ構造層14及び15を形成する。

(もっと読む)

電界効果トランジスタ用窒化物半導体エピタキシャルウェハ、窒化物半導体系電界効果トランジスタ、及び電界効果トランジスタ用窒化物半導体エピタキシャルウェハの製造方法

【課題】電子のトラッピング現象を緩和すると共に、ヘキサゴナル欠陥の発生を抑制可能な窒化物半導体エピタキシャルウェハの製造方法を提供する。

【解決手段】基板1上に核生成層2を形成し、その核生成層2上に第一の窒化物半導体層3を形成し、その第一の窒化物半導体層3上に、前記第一の窒化物半導体層3よりも電子親和力の小さい第二の窒化物半導体層4を形成する窒化物半導体エピタキシャルウェハ10の製造方法において、前記第一の窒化物半導体層3を形成する際の成長温度が、前記第二の窒化物半導体層4を形成する際の成長温度よりも低くするものである。

(もっと読む)

III族窒化物結晶の製造方法およびIII族窒化物結晶

【課題】加工性に優れていて品質が高いIII族窒化物結晶を提供すること。

【解決手段】III族窒化物単結晶を1000℃以上で熱処理することによりIII族元素を含む化合物からなる被膜を形成し、その被膜を除去することによりIII族窒化物結晶を製造する。

(もっと読む)

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

複合基体および複合基板

【課題】焼結基体と半導体結晶層とが貼り合わせられた複合基板およびかかる複合基板に好適に用いられる複合基体を提供する。

【解決手段】本複合基体1は、焼結基体10と、焼結基体10上に配置された基体表面平坦化層12と、を含み、基体表面平坦化層12の表面のRMS粗さが10nm以下である。本複合基板は、複合基体1と、複合基体1の基体表面平坦化層12側に配置された半導体結晶層と、を含み、焼結基体10の熱膨張係数と半導体結晶層の熱膨張係数との差が4.5×10-6K-1以下である。

(もっと読む)

炭化珪素単結晶ウェハ

【課題】デバイス作製に供用可能なウェハ面積部分を増大し、かつ大口径化に伴って増大する加工負荷を回避できる炭化珪素単結晶ウェハを提供する。

【解決手段】ウェハの特定の方位端に総面積の小さい加工欠損部、あるいは非対称な形状を有するノッチ状の加工欠損部を有する炭化珪素単結晶ウェハ。

(もっと読む)

半導体ウエハの製造方法、複合基体および複合基板

【課題】半導体デバイスを効率よく製造するために、基体の種類の如何を問わずに効率よく半導体ウエハを製造することができる半導体ウエハの製造方法、ならびにかかる製造方法に好適に用いられる複合基体および複合基板を提供する。

【解決手段】本半導体ウエハの製造方法は、基体10上に、表面のRMS粗さが10nm以下の基体表面平坦化層12を形成して複合基体1を得る工程と、複合基体1の基体表面平坦化層12側に半導体結晶層20aを貼り合わせて複合基板3A,3B,3Cを得る工程と、複合基板3A,3B,3Cの半導体結晶層20a上に少なくとも1層の半導体層30を成長させる工程と、基体表面平坦化層12をウェットエッチングで除去することにより、基体10から半導体結晶層20aを分離して、半導体結晶層20aおよび半導体層30を含む半導体ウエハ5を得る工程と、を含む。

(もっと読む)

歪吸収中間層遷移モジュールを有するIII族窒化物半導体構造

【課題】歪み吸収III族窒化物中間層モジュールを有する種々の半導体構造を提供する。

【解決手段】基板および当該基板の上方の第一遷移本体を有する。前記第一遷移本体は、第一表面において第一の格子パラメータを有し、前記第一表面とは反対側の第二表面において第二の格子パラメータを有する。前記典型的な実施では、遷移モジュール等の第二遷移本体をさらに有し、この第二遷移本体は前記第一遷移本体の前記第二表面に重層する下表面においてより小さい格子パラメータを有し、前記第二遷移本体の上表面においてより大きい格子パラメータを有し、前記第二遷移本体の上方のIII族窒化物半導体層も同様である。前記第二遷移本体は2以上の遷移モジュールからなっていてもよく、各遷移モジュールは2以上の中間層を有していてもよい。前記第一遷移本体および前記第二遷移本体は前記半導体構造の歪みを減少させる。

(もっと読む)

窒化ガリウム基板

【課題】量産に用い得る厚さと面積を確保しながら、容易な生産方法でかけやわれの発生を抑制してオリエンテーションフラットを形成することを目的とする。

【解決手段】窒化ガリウム結晶体27から、ファセット15を有する硬質の立体構造物14を陵線等に平行に除去することで、欠けや割れの発生を抑制した窒化ガリウム基板を提供できる。しかも、ファセット15を有する硬質の立体構造物14の陵線等は特有の結晶方位を有し、かつ、明瞭であるので、立体構造物14の陵線等に平行に切断加工した窒化ガリウム結晶体27の切断線21をデバイス加工の基準線となるオリエンテーションフラットに用いることができる。

(もっと読む)

半導体装置

【課題】シリコンなどの基板上に形成した高品質な結晶を有する半導体装置を提供する。

【解決手段】実施形態によれば、GaNを含む下地層と、窒化物半導体を含む機能部と、前記下地層と前記機能部との間に設けられ、AlNを含む層を含む中間層と、を備えた半導体装置が提供される。前記下地層のうちの前記中間層とは反対側の第1領域におけるシリコン原子の濃度は、前記下地層のうちの前記中間層の側の第2領域におけるシリコン原子の濃度よりも高く、前記下地層の前記中間層とは反対側の第1面は、複数の凹部を有する。

(もっと読む)

エピタキシャル基板

【課題】シリコン基板を下地基板とし、基板サイズに比して問題ない程度に反りが抑制され、半導体素子の作製に好適なエピタキシャル基板を提供する。

【解決手段】エピタキシャル基板10が、シリコン単結晶からなる下地基板1と、下地基板1の上に形成された複数のIII族窒化物層2,3,4からなるIII族窒化物層群と、を備えており、下地基板1が、ボロンが添加されてなることでp型の導電性を有し、かつ、比抵抗が0.01Ω・cm以上0.1Ω・cm以下であり、複数のIII族窒化物層2,3,4がそれぞれ、少なくともAlまたはGaを含み、エピタキシャル基板の反り量をSR(単位:μm)、窒化物層群の総膜厚をte(単位:μm)、下地基板1の膜厚をts(単位:mm)、下地基板1の直径をds(単位:mm)とするときに、規格化反り指数KがK={(SR/te)×(ts/ds)2}≦1×10-3なる関係式をみたすようにする。

(もっと読む)

III/V族半導体材料を形成する方法及びそのような方法を用いて形成された半導体構造体

【課題】内部の欠陥数がより少なく且つ/又は減少したIII/V族半導体材料を形成する方法、並びに欠陥数がより少なく且つ/又は減少したそのようなIII/V族半導体材料を含む半導体構造体及び素子が必要である。

【解決手段】三元III族窒化物材料を形成する方法は、チャンバー内で基板上に三元III族窒化物材料をエピタキシャル成長させるステップを含む。エピタキシャル成長は、チャンバー中の窒素前駆体の分圧と1つ又は複数のIII族前駆体の分圧との比較的に高い比を含む前駆体ガス混合物をチャンバー内に準備するステップを含む。少なくとも一部は比較的に高い比のため、三元III族窒化物材料の層は、小さいVピット欠陥をその中に含む高い最終厚さに成長させることができる。そのような三元III族窒化物材料の層を含む半導体構造体をそのような方法を用いて作製する。

(もっと読む)

化合物半導体装置及び化合物半導体装置の製造方法

【課題】トレンチを用いて素子分離され、且つ、隣接素子の動作による影響が抑制された化合物半導体装置及び化合物半導体装置の製造方法を提供する。

【解決手段】半導体基板10と、キャリア走行層21とキャリア供給層22を有し、半導体基板上に配置された窒化物半導体層20と、上端部がキャリア走行層とキャリア供給層との界面よりも上方に位置する空洞40を内部に有する、窒化物半導体層の周囲を囲んで配置された素子分離絶縁膜30とを備える。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

41 - 60 / 383

[ Back to top ]