Fターム[5H740KK04]の内容

電力変換一般 (12,896) | 主回路スイッチング素子への制御信号の伝達 (818) | 光によるもの (86)

Fターム[5H740KK04]の下位に属するFターム

光ファイバを用いるもの (15)

ミラーを用いるもの (2)

ゲート用発光回路を冗長化したもの (3)

制御入力に光を用いたもの (16)

Fターム[5H740KK04]に分類される特許

1 - 20 / 50

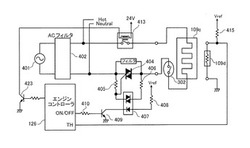

加熱定着装置及び画像形成装置

【課題】商用交流電源に重畳するノイズや電圧波形歪みの影響を受けず、正確にゼロクロスタイミングを検知する。

【解決手段】交流電源401から電力供給されるセラミックヒータ109cと、交流電源からセラミックヒータへの給電制御を行うエンジンコントローラ126と、交流電源の電流値を検知し、電流検知信号を出力するフォトカプラ510と、交流電源の電圧のゼロクロスを検知し、ゼロクロス検知信号を出力するフォトカプラ518を備え、エンジンコントローラは、電流検知信号に基づいて、ゼロクロス検知信号のエッジの検出を行わないマスキング区間と前記ゼロクロス検知信号のエッジの検出を行う非マスキング区間を有するマスクパターンを生成し、マスクパターンの非マスキング区間におけるゼロクロス検知信号のエッジをゼロクロスタイミングとして、給電制御を行う。

(もっと読む)

スイッチング電源回路および電動機の制御装置

【課題】スイッチング電源で、電流検出回路を設けずに、負荷変動に伴う電圧上昇の抑制を可能とする。

【解決手段】スイッチング電源回路14は、一次巻線と二次巻線とを有するトランス41と、スイッチング信号を一次巻線に入力してトランス41を駆動する一次側回路40と、二次巻線に接続され、一次側回路40とは電気的に絶縁されているゲートドライブ回路20−nとを具備している。ゲートドライブ回路20−nは、モータECU100からのPWM信号によって駆動されるゲート駆動回路21−nと、ゲートドライブ回路20−nに流れる電流を増大させるブリーダ抵抗R20−nとを有し、モータECU100からのPWM信号を検出した場合に、ブリーダ抵抗R20−nに流れる電流値を減少させる。

(もっと読む)

インバータ駆動装置

【課題】電気的に絶縁された回路間で電力伝達と信号伝達を行う構成を有していても、回路基板の小型化を容易に実現できる、インバータ駆動装置の提供をすること。

【解決手段】PWM信号S1を互いに相補する2つの波形信号S3A,S3Bに変換する変換回路と、下アーム素子47Aに駆動信号S7Aを伝達する下アーム回路212と,上アーム素子47Bに駆動信号S7Bを伝達する上アーム回路213と、下アーム回路212と上アーム回路213に給電を行うトランス36とを備え、トランス36が、2つの波形信号S3A,S3Bのうち、波形信号S3Aを下アーム回路212に伝達し、波形信号S3Bを上アーム回路213に伝達する、インバータ駆動装置。

(もっと読む)

電力変換装置

【課題】IGBTモジュールを並列接続した構成で、VCEを検出して過電流保護(遮断)する場合、配線インダクタンスの影響で、高速で、確実な保護ができない課題がある。

【解決手段】並列接続されたIGBTモジュール内のIGBTのVCE検出用のダイオードを各IGBT毎又は複数個に対して1個の割合で接続し、過電流時いずれかのVCEが上昇した場合には並列接続された全てのIGBTのゲート信号を強制遮断する。

(もっと読む)

電力変換装置

【課題】冗長システムの中で待機系を構成する場合であっても光発光素子の寿命を短縮させない監視回路を有する電力変換装置を提供する。

【解決手段】電力変換器1を構成するパワーデバイス11と、第1の光絶縁回路を介して第1の電気信号に変換してパワーデバイス11にオンオフ信号を与えるゲート回路2と、パワーデバイス11のGE間電圧からパワーデバイスの健全性を監視する監視回路3とで構成する。監視回路3は、装置の運転モードが運転系であるときは、GE間電圧を光信号に変換し、第2の光絶縁回路を介して電気信号に変換して異常検出回路41に与えるようにし、運転モードが待機系であるときは、GE間電圧をパルス信号に変換し、これを光信号に変換して第2の光絶縁回路を介して第2の電気信号に変換し、その出力を復元手段40によって復元した後異常検出回路41に与えてパワーデバイス11の健全性を監視する。

(もっと読む)

サイリスタ直列回路の故障検出回路

【課題】 複数のサイリスタが直列に接続されたサイリスタ直列回路において、サイリスタがある程度のインピーダンスを保持して短絡した場合でも、故障として検出することができる故障検出回路を提供することにある。

【解決手段】 サイリスタTH1〜THNが直列に接続されたサイリスタ直列回路のサイリスタの故障を検出するゲート制御装置2において、サイリスタTH1〜THNのそれぞれの順電圧信号FV1〜FVNを検出する電圧検出器DV1〜DVNを備え、電圧検出器DV1〜DVNのうち3つの電圧検出器DV1〜DV3は、逆電圧信号RV1〜RV3を検出し、逆電圧信号RV1〜RV3が検出されている期間に、順電圧信号FV1〜FVNを検出した場合、順電圧信号を検出したサイリスタを故障と判断する。

(もっと読む)

双方向スイッチのゲート駆動回路およびそれを用いたインバータあるいはマトリックスコンバータ

【課題】ダブルゲートを有したGaN双方向スイッチに使用されるゲート駆動回路において、何れか一方向にのみ通電可能な逆阻止モード(第一モードおよび第二モード)への移行の高速化を図ることを目的とする。

【解決手段】第一ソース端子4あるいは第二ソース端子5の少なくとも何れか一方と第一ゲート抵抗18A、18B、第二ゲート抵抗19A、19Bを各直列に接続し、第一ゲート抵抗18A、18Bと第二ゲート抵抗19A、19Bの接続点20A、20Bとの間にソース電位の変動が発生した際に、接続点20A、20Bへ電流を流すことのできるバイパス手段としてのダイオード21A、21Bを設ける構成にしたことにより、第一ソース端子4あるいは第二ソース端子5の何れかの電位が上昇した際にダイオード21A、21Bを介してゲート電流を流し、高速に逆阻止モードでの導通を可能としたゲート駆動回路を得られる。

(もっと読む)

ゲートドライバのためのオプトカプラ回路

オプトカプラ回路10は、フォトLED20と並列接続するスイッチ22を含み、フォトLED20はアノード及びカソードを有する。アノードは減結合コンデンサ28を介して電源に接続される。オプトカプラ回路は、スイッチが開放位置にあるときフォトLEDをオンにするよう構成される。スイッチが閉じているときは、スイッチ22は電流の流れの向きを、直列抵抗器32を経由して接地へ向けるようにし、電流の流れを分流してフォトLEDから離すことでフォトLEDをオフにする。第2のコンデンサ38は、フォトLEDのカソードへ接続される。第2のコンデンサは、第2のスイッチ40及び接地へ接続された電流制限抵抗器42と直列に配線される。第1のスイッチ22及び第2のスイッチ40は、カソードが接続されたコンデンサ38の放電を回避するために相補状態で動作する。開示されるオプトカプラ回路10は、より高レベルのコモンモード電圧過渡現象で機能する性能を提供する。  (もっと読む)

(もっと読む)

スイッチの制御を簡略化するための方法と装置

【課題】スイッチの制御を簡略化するための技法を提供する。

【解決手段】実施の一形態では、スイッチの両端の電圧の関数としてスイッチを制御する方法を提供する。実施の一形態では、スイッチの両端の電圧の傾斜の関数としてスイッチを制御する方法を提供する。実施の一形態では、スイッチがオフになっている間のスイッチの両端の電圧に応答して実質的に固定されたオン時間中スイッチをオンに切り替えている。実施の一形態では、スイッチがオフになっている間のスイッチの両端の電圧の傾斜に応答して実質的に固定されたオン時間中スイッチをオンに切り替えている。

(もっと読む)

半導体電力変換装置

【課題】半導体スイッチ素子の動作状態の情報を外部装置へ伝送するにあたって、情報の数を減らすことなく絶縁素子の使用個数を低減し、装置の小型化と低コスト化、及び、故障率の低減を実現する。

【解決手段】異なる基準電位に基づいてスイッチング動作を行う半導体スイッチ素子(1a、1b)を2個以上直列接続して構成された半導体電力変換装置(100)であって、それぞれの半導体スイッチ素子の異常検出要因および所定の物理量を状態検知情報として検知し、外部装置へ伝送する情報伝送回路部(4b)を備え、情報伝送回路部(4b)は、検知した状態検知情報に応じて、異常検出要因および所定の物理量を識別可能な二値論理信号を生成し、生成した二値論理信号を単一の絶縁素子(7b)を介して外部装置へ伝送する。

(もっと読む)

負荷制御装置

【課題】負荷への電力投入時における突入電流による素子の破壊又は劣化を防止しうる負荷制御装置を提供する。

【解決手段】操作スイッチ4から起動信号を受信したときに、制御部13は、第1電源部14への電力を供給する電源が第2電源部15から第3電源部16に切り替わる前に、主開閉部11に対して主スイッチ素子11aを導通させるための初期駆動信号を出力する。

(もっと読む)

負荷制御装置

【課題】スイッチ素子の発熱を抑制して小型化を図りつつ、開閉タイミングを正確に制御して、調光制御等の高度な負荷制御を行うことができる負荷制御装置を提供する

【解決手段】操作部28に入力された操作に応じて、制御部13が交流電源の1/2周期のうちトランジスタ構造の主開閉部11を導通させるために計数される主開閉部導通時間を設定し、電圧検出部18が第3電源部16に入力される電圧が所定の閾値に達したときから計数される第1所定時間と、主開閉部導通時間とが重複している時間だけ、主開閉部11を導通させることにより調光制御する。

(もっと読む)

ドライブ回路

【課題】連続通弧により半導体スイッチが故障に至るような誤動作を回避するドライブ回路を提供する。

【解決手段】外部から入力された駆動信号に基づいて半導体スイッチ20を駆動させるドライブ回路10bであって、駆動信号に基づいて半導体スイッチ20の駆動制御を行うゲートドライバ16と、ゲートドライバ16による制御の状態にかかわらず、駆動信号の立ち上がりのタイミングに基づいて半導体スイッチ20のスイッチング周期の終了時までの所定期間に強制的に半導体スイッチ20をオフさせる強制オフ回路18とを備える。

(もっと読む)

電力変換装置

【課題】遮過電圧保護機能付きサイリスタにスナバ回路が設けられた電力変換装置において、過電圧保護機能付きサイリスタがブレークオーバ電圧を超えることにより自己点弧する場合、より長く運転を継続させて、スナバ回路を保護することのできる電力変換装置を提供することにある。

【解決手段】直列に接続されたVBOフリーサイリスタ21A,21B,21Cにスナバ回路22A,22B,22Cが設けられたサイリスタバルブ2を備えた電力変換装置10において、VBO点弧を検出した場合、カウンタ14をカウントアップさせ、VBO点弧を検出していない間は、クロック13によるパルス信号に応じて、カウンタ14をカウントダウンさせ、カウンタ14のカウント値が設定値NT以上になると、保護装置4が保護動作する。

(もっと読む)

ドライバ装置

【課題】UVLO機能を内蔵したドライバ装置を提供する。

【解決手段】電源に接続された第1のスイッチ素子と、前記第1のスイッチ素子と直列接続された第2と、第3と、前記第3のスイッチ素子と並列接続された第4のスイッチ素子と、一端が前記第3及び第4のスイッチ素子に接続され、他端が前記第1のスイッチ素子の制御電極に接続された第1の抵抗と、前記第1の抵抗を介して前記第3のスイッチ素子の負荷となるカレントミラーと、前記カレントミラーに電流を流す放電回路と、外部から入力信号を受けて、前記第2と第3のスイッチ素子を介して前記第1のスイッチ素子と、を交互にオン、オフするように制御し、かつ、前記放電回路及び前記第4のスイッチ素子を、前記電源が立ち上がるときにオンさせて前記カレントミラーに電流を流すことにより、電源が立ち上がった後は前記第4のスイッチ素子をオフする制御回路を備える。

(もっと読む)

車両用インバータ装置

【課題】インバータ回路のスイッチング損失の増大を抑制しつつ、インバータ回路のスイッチング速度を調整する際のパラメータの値を取得するための検出回路を不要とする。

【解決手段】車両用インバータ装置は、IGBT11a〜11fを3相ブリッジ接続したインバータ回路を備えたインバータ部1と、インバータ部1の各IGBTのゲート端子を制御する駆動指令回路2とを備える。駆動指令回路2は、モータ5に印加すべき要求トルクに基づいて、インバータ部1に備えられたIGBT11a〜11fのオン・オフ期間およびIGBT11a〜11fのスイッチング速度をスイッチ制御回路13a〜13fを介して制御する。

(もっと読む)

電流制御装置及び画像形成装置

【課題】負荷に供給する電力デューティを、周波数、位相角の変動量の情報に基づき歪量補正を行うことでより高精度な電流制御を行う電流制御装置及びそれを具備した画像形成装置を提供することを目的とする。

【解決手段】負荷に供給される電力を位相制御する位相制御手段12と、前記負荷に流れる電流の経路に設置される電流検出トランス25と、前記電流検出トランスの出力電圧が入力されることにより、前記負荷に流れる電流値を検知する電流検知手段27と、前記電流検知手段で検知した電流値を、前記位相制御手段で制御した位相角に基づき補正する歪量補正手段を有することを特徴とする電流制御装置。

(もっと読む)

過電圧保護機能付きサイリスタの直列回路

【課題】負荷電流が断続する運転状態が生じても誤検出によって過電圧保護機能を動作させることのない過電圧保護機能付きサイリスタの直列回路を提供する。

【解決手段】直列リアクトル12を介して直列接続され、夫々スナバ回路13、14を備えた複数個の過電圧保護機能付きサイリスタ11と、過電圧保護機能付きサイリスタ11の主電極間の電圧を夫々検出する順電圧検出回路16と、位相制御装置3からの点弧タイミング信号により過電圧保護機能付きサイリスタ11にゲートパルスを供給するゲート制御手段2とで構成する。ゲート制御手段2は、位相制御装置3が点弧タイミング信号を発生してから第1の所定時間が経過するまでの間で、且つ前記ゲートパルスを供給して第2の所定時間経過後の期間に、何れかの順電圧検出回路16が所定の閾値以上の電圧を検出したとき、装置を停止するための保護停止指令を出力する。

(もっと読む)

スイッチ制御装置及びこれを用いたモータ駆動装置

【課題】本発明は、コストの低減や信頼性の向上を実現することが可能なスイッチ制御装置、及び、これを用いたモータ駆動装置を提供することを目的とする。

【解決手段】本発明に係るスイッチ制御装置1は、入力信号INに基づいてスイッチ制御信号を生成するコントローラが集積化された第1半導体チップ10と、前記スイッチ制御信号に基づいてスイッチNUの駆動制御を行うドライバが集積化された第2半導体チップ20と、第1半導体チップ10と第2半導体チップ20との間を直流的に絶縁しながら前記スイッチ制御信号などの受け渡しを行う直流絶縁素子が集積化された第3半導体チップ30と、を一のパッケージに封止して成る構成とされている。

(もっと読む)

サイリスタのゲートドライブ回路

【課題】瞬低装置に備えられたサイリスタのゲートドライブ回路においては、通常運転時における信頼性をさらに向上させることが要求される。

【解決手段】瞬低装置に備えられたサイリスタS1,S2を制御するサイリスタのゲートドライブ回路に、1次側が制御用電源3に接続され、2次側が前記サイリスタS1,S2と並列に接続されたフォトカプラPC1,PC2を設ける。前記サイリスタS1,S2の制御方法としては、前記サイリスタS1,S2をオン状態とする場合、前記フォトカプラPC1,PC2をオフにし、商用電源1から出力された電流をサイリスタS1,S2のゲートに印加する。一方、前記サイリスタS1,S2をオフとする場合、前記フォトカプラPC1,PC2をオンにし、商用電源1から出力された電流をサイリスタのゲートに印加させないようにする。

(もっと読む)

1 - 20 / 50

[ Back to top ]