Fターム[5J001AA00]の内容

パルス回路 (4,711) | 素子 (747)

Fターム[5J001AA00]の下位に属するFターム

バイポーラトランジスタ (19)

ダイオード (8)

ツェナーダイオード (2)

ユニポーラ (340)

SCR

PUT

UJT

四層、五層ダイオード

リレー

遅延線 (355)

CCD,BBD (1)

エサキダイオード

電解時限素子 (2)

Fターム[5J001AA00]に分類される特許

1 - 20 / 20

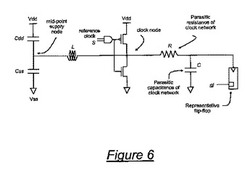

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

インダクタオーバーヘッドなしで共振クロック分配ネットワークの固有周波数を選択する方法

共振クロック分配ネットワークのためのインダクタアーキテクチャが提示される。このアーキテクチャにより、選択的にインダクタを切り離すことによって共振クロック分配ネットワークの固有周波数の調整が可能になり、複数のクロック周波数でエネルギ効率の良い作動が実現する。提示されたアーキテクチャは、主として統合されたインダクタを備える共振クロックネットワーク設計を対象としており、面積オーバヘッドが現れない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

半導体装置

【課題】保護回路において、所望の遅延時間を実現する。また、遅延回路の小型化を図り、消費電力を低減させる。

【解決手段】遅延回路100は、第1のインバータ101〜第3のインバータ103、第4のpチャネルMOSFET7、第4のnチャネルMOSFET8、遅延抵抗121およびキャパシタ122で構成されている。遅延抵抗121は、第1のインバータ101の出力端子と第2のインバータ102の入力端子の間に接続されている。第4のnチャネルMOSFET8のゲート端子は、遅延抵抗121と第2のインバータ102の入力端子の間のノード113に接続されている。第4のnチャネルMOSFET8のゲート端子とドレイン端子の間には、キャパシタ122が接続されている。第4のnチャネルMOSFET8の帰還容量を用いることで、キャパシタ122の容量を、キャパシタ122の物理的な静電容量よりも擬似的に大きくする。

(もっと読む)

移相回路

【課題】入力信号の周波数に依存せずに入力信号に対して所定の位相差を有する出力信号を生成する。

【解決手段】VDDから定電流を供給する定電流回路201aと、入力電流に対してn倍の出力電流を流すカレントミラー回路204a、205aと、矩形波の入力信号1Aaの論理レベルによって定電流回路に流れる電流をカレントミラー回路に流すか、出力端子1Baに流すか切り替えるスイッチ回路202a、203aとを備えた波形生成回路102aにより、立ち上がり勾配1に対してn倍の立ち下がり勾配波形を有する三角波を生成する。これと反転信号1Abを入力した波形生成回路102bにより生成した三角波の電圧をコンパレータ103で比較し出力信号を生成する。入力信号のデューティー比が50%である場合には、1/(2+2n)周期遅延した出力信号が得られる。

(もっと読む)

パルス発生回路

【課題】発振周波数が数MHz〜GHzの高周波用に適用可能であり、かつ消費電力が少ない、定電流回路を用いたパルス発生回路を提供すること。

【解決手段】パルス発生回路は、電源間に定電圧回路1を有し、電流制御素子7と波形発生部9とを直列に接続して、それらを定電圧回路1と並列に接続して構成されている。そして、波形発生部9は、平滑回路2と、水晶発振回路4と、水晶発振回路4からの出力を受けて最終出力波形のデューティ比を調整する出力デューティ調整回路5と、水晶発振回路4の発振波形と最終出力波形との位相差を調整する位相調整回路6と、を並列に接続して構成されている。使用する水晶振動子の周波数によっては、位相調整回路6の替わりに分周回路を並列に接続して構成されている。

(もっと読む)

ジッタ低減回路

【課題】本発明は、高い信号周波数においても、消費電力、回路規模、及びコストの観点から効率的に信号レベルとタイミングとを回復可能なジッタ低減回路を提供することを目的とする。

【解決手段】ジッタ低減回路は、第1の信号が伝搬する複数の区間からなる信号線と、信号線の複数の区間に対応して設けられ第2の信号を伝搬させる複数の遅延線を含み、複数の遅延線の各遅延線における第2の信号の遅延量は、複数の区間のうちの対応する1つの区間における第1の信号のレベルが第1のレベルの場合に第1の遅延量となり、当該1つの区間における第1の信号のレベルが第2のレベルの場合に第2の遅延量となるように複数の遅延線が構成されることを特徴とする。

(もっと読む)

遅延回路

【課題】遅延時間を所望の値に容易に設定することが可能な遅延回路を提供する。

【解決手段】遅延回路100は、入力端子1に入力が接続された第1のインバータ3と、この第1のインバータ3の出力に一端が接続された抵抗4と、この抵抗4の他端と接地電位VSSとの間に接続された容量5と、抵抗4の他端に入力が接続され、出力端子2に出力が接続された第2のインバータ6と、を備える。第2のインバータ6は、切り替え可能な2つの異なる回路しきい値を有する。

(もっと読む)

遅延回路

【課題】遅延時間を精度よく調整することができる遅延回路を得る。

【解決手段】入力信号に所望の遅延を付加して出力する遅延回路であって、直列接続した複数の単位回路と、最も出力側の単位回路の出力信号と入力信号の何れか一方を選択する第1のセレクタとを有し、各単位回路は、自身よりも一段入力側の単位回路の出力信号と入力信号の何れか一方を選択する第2のセレクタと、第2のセレクタの出力信号を遅延させる遅延部と、遅延部による遅延時間を調整する遅延調整部とを有する。

(もっと読む)

遅延回路、及び試験装置

【課題】所望の遅延量、所望の遅延分解能、及び所望の可変遅延範囲を生成する遅延回路を提供する。

【解決手段】入力信号を所望の時間遅延させた遅延信号を出力する遅延回路であって、入力信号に応じて発光し、遅延信号を出力する発光素子と、第1発光素子の発光閾電流より小さいバイアス電流を、第1発光素子に予め供給するバイアス電流源と、所望の遅延時間に基づいて、バイアス電流を制御するバイアス電流制御部と、入力信号に応じて、発光素子を発光させるための変調電流を発光素子に供給する変調電流源と、遅延回路における遅延分解能に基づいて、変調電流を制御する変調電流制御部とを備える。変調電流制御部は、遅延回路における可変遅延範囲に更に基づいて、変調電流を制御する。

(もっと読む)

遅延回路

【課題】不必要なスイッチ素子の寄生容量を付加することなく容量値の変更を実現することで、広い可変範囲を持ちながら最小遅延が大きくならない遅延回路の提供。

【解決手段】この発明は、差動対となるN型のMOSトランジスタMN1,MN2と、電流源1と、遅延量を設定するための一対の遅延量設定部2、3とを備えている。遅延量設定部2は、キャパシタC0,C1,C2からなるキャパシタ群21と、このキャパシタ群21との間で電荷の充放電を行う抵抗として機能する2つのP型のトランジスタMP0,MP1と、スイッチSW0〜SW2と、スイッチSSW3,SW4とを備えている。スイッチSW0〜SW2は、MOSトランジスタMP0,MP1のうちの1つを選択的に有効化させる。スイッチSW3、SW4は、キャパシタC0に対して、キャパシタC1,C2を選択的に接続可能とするものである。

(もっと読む)

遅延ロックループ、および、遅延鎖の設定方法

【課題】過渡回復を出来る限り速く行う。

【解決手段】遅延ロックループは、入力部(9)と直列接続遅延セル(30,50,70,90)と出力部(10)とを有し、出力部では、遅延鎖(1)により遅延時間(Tk)だけ遅延された信号(PreStrobe)が供給される。遅延ロックループは位相検出器構造(2)を含み、位相検出器構造は入力側において遅延鎖(1)の出力部(10)と遅延鎖(1)の遅延セル(30,50,70,90)のうちの1つの出力部とに結合される第2位相検出器セル(31,51,71,91)と、遅延鎖(1)の出力部(10)と遅延鎖(1)の入力部(9)とに結合された位相検出器とを備える。位相検出器構造(2)、位相検出器(3)は制御ユニット(4)に接続される。制御ユニット(4)は遅延セル(30,50,70,90)のうちの個数Zを、遅延を行うように起動することにより遅延鎖(1)の遅延時間(Tk)を設定する。

(もっと読む)

半導体記憶装置

【課題】駆動電源電圧を低下させながら、セルコア部のアクセスを高速化させることで、低電圧化された電源電圧に対して、セルコア部と周辺回路との総合的なアクセス速度の低下を抑止した半導体記憶装置の提供。

【解決手段】セルコア部20、周辺回路10を、電源電圧VDDで駆動し、セルコア部20のワード線等の制御信号に供給される昇圧電圧VBOOSTは、電源電圧VDDに依存しない定電圧が供給され、周辺回路10からセルコア部20への制御信号の遷移タイミング、及び/又は、前記制御信号のパルス幅を規定する信号を生成する回路が、信号の遅延を、供給される電源電圧の低下に対して遅延時間が短縮するという特性を有する遅延回路11を用いて行う。

(もっと読む)

比較器

【課題】小面積で計算速度が速い比較器を提供する。

【解決手段】比較器は、各々の入力端にクロック信号が共通して入力される第1及び第2遅延回路と各々の第1入力端に第1遅延回路の出力信号及び第2遅延端の出力信号が各々入力される第1及び第2論理ゲートを含む第1ラッチ回路、及び第1論理ゲートの出力端から出力される信号及び前記第2論理ゲートの出力端から出力される信号をラッチする第2ラッチ回路を備える。第1遅延回路の遅延時間は外部から入力される第1デジタル信号により制御される可変の遅延時間であり、前記第2遅延回路の遅延時間は外部から入力される第2デジタル信号により制御される可変の遅延時間である。

(もっと読む)

発光素子駆動回路及び大型映像表示装置

【課題】温度の変化や経年に伴う劣化が生じた場合であっても、駆動パルスのパルス幅と同じパルス幅の駆動回路出力を出力できる発光素子駆動回路、及びその発光素子駆動回路を備えた大型映像表示装置を提供する。

【解決手段】LED3の発光・消光を指示するMPU駆動パルス11と、駆動回路出力12が駆動パルス補正回路8に入力される。駆動パルス補正回路8は、MPU駆動パルス11のパルス幅と駆動回路出力12のパルス幅とが等しくなるように、MPU駆動パルス11を補正した補正駆動パルス1を出力する。駆動回路2は、補正駆動パルス1に基づいて駆動回路出力12を出力する。そのため、駆動回路2に劣化が生じて駆動回路出力12のパルス幅に変化が生じた場合であっても、その変化に応じてMPU駆動パルス11のパルス幅を補正し、MPU駆動パルス11と同じパルス幅の駆動回路出力12を出力することができる。

(もっと読む)

遅延回路及び発振回路

【課題】 本発明の課題は、電流源の設定電流が小さい場合でも高精度な遅延時間を得ることができる遅延回路及び発振回路を提供することである。

【解決手段】 電流値が設定可能な電流源(I1)と、電流源によって充電されるコンデンサ(C1)と、コンデンサに蓄積されたの電荷を放電するスイッチング素子(M1〜M10)と、コンデンサの充電電圧と基準電圧とを比較するコンパレータ(CMP1)とを備え、スイッチング素子がオフしてコンデンサの充電を開始し、コンデンサの電圧が基準電圧に達するまでの時間を遅延時間として出力する遅延回路において、電流源の設定電流値が小さい場合は、スイッチング素子のリーク電流を少なくしている。

(もっと読む)

容量装置及び半導体装置並びにそれを用いたマルチバイブレータ

【課題】二端子間に接続されて用いられる容量装置及び半導体装置並びにそれを用いたマルチバイブレータに関し、寄生容量の影響を低減できる容量装置及び半導体装置並びにそれを用いたマルチバイブレータを提供することを目的とする。

【解決手段】 本発明は、二端子(a、b)間に接続される容量装置(C100、C200)において、複数の容量素子(C10、C20)を、二端子(a、b)の両方の端子から見た素子容量(C11、C21)及び寄生容量(C12、C22)の配置が対称となるように接続したことを特徴とする。

(もっと読む)

システムLSI

【課題】 製造プロセスのばらつきによるシステムLSIの製品不良を回避する。

【解決手段】 ROM等の特定ブロック20へのクロック供給経路上に、縦続接続された複数の遅延素子31a〜31cとセレクタ32で構成されて遅延制御信号DCNに従って遅延クロック信号DCKを選択出力するクロック遅延回路30を設ける。製品試験時に、セレクタ43を介して遅延調整端子51から遅延制御信号DCNを与えて特定ブロック20の動作試験を行い、正常動作が得られる遅延制御信号DCNの値を調べる。製品試験で得られた適正な遅延制御信号の値を、ヒューズ回路またはPROMで構成される遅延設定回路40に記憶させる。通常動作時には、遅延設定回路40の記憶内容をセレクタ43を介してクロック遅延回路30に与える。

(もっと読む)

多電源半導体装置

複数のブロック31、32により構成され、各ブロック31、32が独立したクロック回路41、42を有し、可変電源101により動作する多電源半導体装置において、クロック生成回路10から複数のブロック32に供給されるクロック信号に、可変電源101の電圧値に基づいて遅延量が変化する可変遅延回路20を設ける。このことにより、可変電源101の電源電圧を変化させた場合でも、ブロック間のクロックスキューが低減される。 (もっと読む)

1 - 20 / 20

[ Back to top ]