Fターム[5J001AA04]の内容

Fターム[5J001AA04]の下位に属するFターム

CMOS (179)

Fターム[5J001AA04]に分類される特許

1 - 20 / 161

データドライバ、表示パネル駆動装置及び表示装置

パルス幅調整回路および方法

パルス幅延長回路および方法

遅延回路及びそれを用いた半導体装置

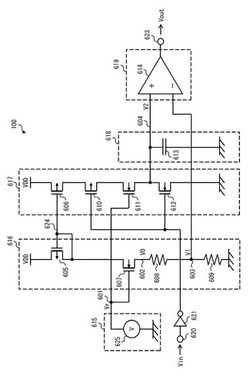

【課題】入力信号に精度の高い遅延を付加した出力信号を生成することが可能な遅延回路を提供すること。

【解決手段】本発明にかかる遅延回路は、第1電流I0及び第1電流I0と略同一の第2電流I0を生成する電流ミラー回路と、ゲートに基準電圧Vrが印加されソース−ドレイン間に第1電流I0が流れることにより電圧V0を生成するトランジスタ607と、電圧V0に応じた参照電圧V1を生成する抵抗素子608,609と、コンデンサ613と、第2電流I0の電荷をコンデンサ613に蓄積し、又は、コンデンサ613に蓄積された電荷を放出する充放電部と、充放電部とコンデンサ613との間に設けられ、ゲートに基準電圧Vrが印加されソース−ドレイン間に第2電流I0が流れることにより、比較電圧V2を生成するトランジスタ611と、比較電圧V2と参照電圧V1とを比較し比較結果を出力信号Voutとして出力する電圧比較部619と、を備える。

(もっと読む)

遅延ロックドループを内蔵する半導体集積回路およびその動作方法

【課題】擬似ロックを防止するための論理回路の回路規模を低減する。

【解決手段】遅延ロックドループ(DLL)は、複数の可変遅延回路DL0〜8の電圧制御遅延回路1と位相周波数比較器2とチャージポンプ3を具備する。初段の出力PH[0]と最終段の出力PH[8]は、比較器2に供給される。比較器2のアップ信号とダウン信号は、チャージポンプ3に供給される。擬似ロック防止回路4は、第M段の出力PH[1]と第M+1段の出力PH[2]に応答して、可変遅延リセット信号RST_VDL_T、Bを生成する。初段の回路DL0から第M+1段の回路DL2に、クロック入力信号CLKとクロック反転入力信号がリセット信号RST_B、Tとして供給される。第M+2段の回路DL3から最終段の回路DL8に、可変遅延リセット信号RST_VDL_T、Bがリセット信号RST_B、Tとして供給される。

(もっと読む)

半導体装置及びデータ処理システム

【課題】外部電圧VDDの変動に伴うレイテンシカウンタのラッチマージンの低下を抑制する。

【解決手段】半導体装置は、外部クロック信号に基づいて生成される内部クロック信号LCLKOEFTと、外部から供給されるリードコマンドに応じて生成される内部リードコマンドMDRDTとを受け、内部リードコマンドDRCを生成するレイテンシカウンタ55を備え、レイテンシカウンタ55は、出力ゲート信号COT0〜COT7のそれぞれを遅延させることにより入力ゲート信号CIT0〜CIT7を生成する遅延回路部200を有し、遅延回路部200は、外部電圧VDDで動作する遅延素子と、内部電圧VPERIで動作する遅延素子とを含む。

(もっと読む)

半導体装置、シフトレジスタ、表示装置

【課題】非選択期間においてノイズが少なく、且つトランジスタを常時オンすることのない半導体装置、シフトレジスタ回路を提供することを目的とする。

【解決手段】第1〜第4のトランジスタを設け、第1のトランジスタの、ソースとドレインのうち一方を第1の配線に接続し、他方を第2のトランジスタのゲート電極と接続し、ゲート電極を第5の配線に接続し、第2のトランジスタの、ソースとドレインのうち一方を第3の配線に接続し、他方を第6の配線に接続し、第3のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第2のトランジスタのゲート電極に接続し、ゲート電極を第4の配線に接続し、第4のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第6の配線に接続し、ゲート電極を第4の配線に接続する。

(もっと読む)

半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

(もっと読む)

アキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法

【課題】フラクショナル分周器の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制したアキュムレータ型フラクショナルN−PLLおよびその制御方法を実現する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

TDC装置とTDCのキャリブレーション方法

【課題】遅延素子の遅延時間のばらつきに対してTDCの変換特性を一定とし線形性を実現可能なTDCの提供。

【解決手段】第1の信号DATAを順次遅延させる複数段の遅延素子111〜11Nを有するディレイライン10と、第2の信号CLKに応答して複数段の遅延素子の出力をサンプルする複数のフリップフロップ121〜12Nと、相隣るフリップフロップの出力結果が切り替わるエッジ位置を、第1の信号の第2の信号に対する位相差として検出するエッジ検出器13と、を備え、エッジ位置の検出結果に基づき、バイアス制御用の制御コードICNTを生成するキャリブレーション制御回路15と、制御コードに対応する複数段の遅延素子に対して供給するバイアス発生回路14を備え、第1の信号の周波数範囲に対応した段数の遅延素子に、第1の信号のエッジが位置するように遅延素子111〜11Nの遅延時間の校正を行う。

(もっと読む)

遅延回路

【課題】温度や電圧の変動によって遅延回路に生じる遅延時間をキャンセルする。

【解決手段】Nチャンネル型の第1トランジスタ及びPチャンネル型の第2トランジスタが直列接続されてなる複数のインバータINVo,INVeが交互に接続された遅延回路であって、電源配線VDDとインバータINVeの入力ノードinとの間に接続されたPチャンネル型の第3トランジスタを備える。本発明によれば、温度や電圧などの変動が生じた場合であっても、第3トランジスタの存在により、複数のインバータにそれぞれ含まれる第2トランジスタの特性変動が相殺される。これにより、温度や電圧などの変動が生じた場合、遅延回路全体の遅延量変動は、第1トランジスタの特性変動によるものとみなすことが可能となる。

(もっと読む)

半導体装置およびその制御方法

【課題】半導体装置のデータ入力回路における消費電力を削減すること。

【解決手段】半導体装置は、クロック信号の立ち上がりエッジおよび立ち下がりエッジの少なくともいずれか一方の近傍の期間において活性状態となる制御信号を生成して出力する制御信号生成回路と、制御信号が活性状態である期間においてデータ信号を受信可能な活性状態となり、それ以外の期間において非活性状態となるデータ入力回路と、を備えている。

(もっと読む)

差動信号生成回路

【課題】位相差が減少された差動信号を生成するようにした差動信号生成回路を提供する。

【解決手段】入力信号を順次反転させて複数の遅延信号を生成するように構成されたインバータアレイと、複数の遅延信号のうち、第1の遅延信号と第2の遅延信号とを予め設定された混合比で混合して第1の差動信号を生成するように構成された位相混合器とを備え、複数の遅延信号のうち、第1の遅延信号と第2の遅延信号との中間に該当する遅延時間を持つ第3の遅延信号を第2の差動信号として生成するように構成されることを特徴とする。

(もっと読む)

半導体集積回路及び半導体集積回路の電源スイッチ制御方法

【課題】電源スイッチを非導通状態から導通状態に遷移させる時間を最適化できる半導体集積回路及びその電源スイッチ制御方法を提供する。

【解決手段】共通電源配線と、第1の回路と、それぞれ電源スイッチ制御信号に基づいて導通、非導通が制御され共通電源配線と第1の回路との間を並列に接続する複数の電源スイッチと、電源スイッチ制御信号と複数の電源スイッチとの間に接続され電源スイッチ制御信号が非導通状態から導通状態に遷移するときに電源スイッチ制御信号の遷移をそれぞれ異なった遅延時間だけ遅延させて複数の電源スイッチに伝え複数の電源スイッチをそれぞれ時間をずらして非導通状態から導通状態に遷移させる遅延回路と、各遅延回路の遅延時間の増減を制御する遅延時間制御部と、を備える。

(もっと読む)

内部クロック調整回路

【課題】半導体記憶装置の動作テストに際し、ストローブ信号の発生タイミングを適切に設定する。

【解決手段】遅延回路132は、外部クロック信号CLKTを遅延させることにより内部クロック信号DCLKを出力する。位相差判定回路144に含まれる検出電位発生回路は、内部クロック信号RDCLKTのアクティブエッジのタイミングと、目標となる外部クロック信号CLKTのタイミングとの差分に対応する検出電位を第1ノードに発生させる。位相差判定回路144に含まれる基準電位発生回路は、基準電位を第2ノードに発生させる。位相制御回路134は、検出電位にしたがって内部クロック信号DCLKを遅延させる。このとき、検出電位が基準電位よりも大きいときには内部クロック信号DCLKの1回あたりの調整量が変化する。

(もっと読む)

半導体装置

【課題】回路を通常の動作していない状態からスタンバイ状態に変える、及び、回路全体は通常の動作をしていない状態だがバイアス条件を変える、という具合に条件を変化させることでストレスを緩和する。

【解決手段】スタンバイ制御信号が活性状態のとき、前記タイマー回路からのタイマー出力信号に基づき、機能回路部30の論理状態を所定時間毎に変えるMODE制御信号を生成するモード制御回路20と、機能回路部30の出力信号を受け前記出力信号の出力を制御する出力制御回路50と、を備え、出力制御回路50はMODE制御信号をDelay回路40で遅延させて生成されるDelay出力信号に基づき、機能回路部30がMODE制御信号により論理状態を変えている間、前記機能回路部出力信号を出力に伝達せずに、機能回路部30がMODE制御信号によって前記論理状態を変える直前の機能回路部出力信号を保持出力する。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

遅延回路、及び電子機器

【課題】遅延回路のキャパシタの容量を増大させることなく、外来ノイズの影響による出力電圧の誤動作を防止する。

【解決手段】キャパシタと第1のノードを介して接続され、前記キャパシタを充電または放電する定電流源と、入力電圧が第1のレベルに変化したときに前記キャパシタを放電または充電し、入力電圧が第2のレベルに変化したときに前記キャパシタを充電または放電する充放電回路と、前記キャパシタの充放電の開始から、前記第1のノードの電圧が所定の検知電圧を超えるまでの時間遅延して、出力電圧のレベルを第1のレベルから第2のレベルに変化させる電圧検知回路とを有する遅延回路において、前記入力電圧が第2のレベルであって、かつ前記出力電圧が第2のレベルに変化したときに、前記第1のノードの電圧を前記検知電圧を超えるレベルに保持する電圧保持回路を備えることで出力電圧の誤動作を防止する。

(もっと読む)

半導体装置

【課題】 起動時に遅延回路部の遅延時間を調整する半導体装置を提供する。

【解決手段】 半導体装置は、電源立ち上げ動作時に遅延回路部の遅延時間を検出し、検出結果に基づいて遅延調整信号を生成する遅延制御部と、遅延回路部に設けられ、遅延調整信号に応じて遅延回路部の遅延時間を調整する遅延調整部とを備える。

(もっと読む)

1 - 20 / 161

[ Back to top ]