Fターム[5J001AA05]の内容

Fターム[5J001AA05]に分類される特許

1 - 20 / 179

パルス幅延長回路および方法

半導体記憶装置

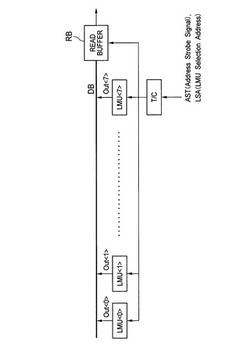

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

遅延回路

【課題】電源電圧が変わっても一定の遅延時間を有する遅延回路を提供する。

【解決手段】遅延回路10では、第1、第2チャネルの第1、第2絶縁ゲート電界効果トランジスタP11〜P1n、N11〜N1nのゲート電極同士および第1電極同士が接続された相補型電界効果トランジスタは、ゲート電極に入力される入力信号Vinを反転した出力信号Voutを出力する。第1チャネルの第3絶縁ゲート電界効果トランジスタP21〜P2nは第1電源電圧Vccが印加される第1電源端子16と第1絶縁ゲート電界効果トランジスタP11〜P1nの第2電極との間に接続され、第1電源電圧Vccをゲート電極に入力される第1制御信号Vcに応じて定まる出力電圧Vccoutに変換して出力する。第1制御信号生成回路13は、第1電源電圧Vccに応じて第1制御信号Vcを生成し第3絶縁ゲート電界効果トランジスタP21〜P2nのゲート電極に出力する。

(もっと読む)

デューティ比補正回路

【課題】入力される外部クロック信号の活性化エッジを用いてデューティ比を補正することができるデューティ比補正回路を提供する。

【解決手段】本発明のデューティ比補正回路は、第1の基準クロック信号及びリセット信号に応じて定義されるデューティ比の内部クロック信号を生成するデューティ調整手段と、第2の基準クロック信号及びフィードバックされる前記内部クロック信号に応答して前記リセット信号を生成するリセット信号生成手段とを備えることを特徴とする。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

半導体装置

【課題】出力クロック信号を生成して出力するまでに要する時間を短縮させる。

【解決手段】半導体装置は、第1のクロック信号のライズエッジ及び第2のクロック信号のライズエッジを合成して第1及び第2のクロック信号のライズエッジの間にライズエッジを有する第3のクロック信号を生成する第1の位相合成回路と、第1のクロック信号のフォールエッジ及び第2のクロック信号のフォールエッジを合成して第1及び第2のクロック信号のフォールエッジの間にフォールエッジを有する第4のクロック信号を生成する第2の位相合成回路と、第3のクロック信号のライズエッジを受けてライズ/フォールエッジの内の一方の位相を、第4のクロック信号のフォールエッジを受けてライズ/フォールエッジの内の他方の位相を其々調整した出力クロック信号を出力する第3の位相合成回路と、を備える。

(もっと読む)

CMOSインバータ

【課題】 入力波形が急峻な場合でも反転電位を用いずに容易にデューティを補正することができるCMOSインバータを提供する。

【解決手段】 PMOSトランジスタP1と、NMOSトランジスタN1と、入力端子NGと、出力端子NDとを具備し、前記PMOSトランジスタ側もしくは前記NMOSトランジスタ側に接続されたスイッチを有している。前記スイッチがPMOSスイッチP2の場合には前記PMOSトランジスタ側に接続され、前記スイッチがNMOSスイッチの場合には前記NMOSトランジスタ側に接続される。入力端子NGに入力信号を入力した後に、前記スイッチに設けられた制御端子G1に制御信号を前記入力信号とずらして入力することによって前記入力信号の電圧を保持させ出力信号のデューティ補正を行う。

(もっと読む)

遅延回路

【課題】遅延時間の精度を向上するとともに、回路面積の小型化を図る。

【解決手段】入力端子INを介して入力される入力信号に応じてオンオフするトランジスタ10と、トランジスタ10と電源端子VBの間に配置された抵抗20と、トランジスタ10と抵抗20の接続点の電位がハイレベルになるとオフするトランジスタ11と、トランジスタ11と接地端子VSS間に配置された抵抗21と、トランジスタ10と抵抗20の接続点の電圧を出力する出力端子OUTと、トランジスタ11と抵抗21の接続点にアノードが接続され、トランジスタ10と抵抗20の接続点にカソードが接続されたダイオード30と、を備えた。

(もっと読む)

遅延回路およびシステム

【課題】 遅延段の数を切り換えるときの遅延時間の増加量および減少量を一定にすることで、高い精度を有する遅延回路を形成する。

【解決手段】 遅延回路は、直列に接続された複数の遅延段、検出回路および調整回路を有する。各遅延段は、前段からの信号を反転して後段に伝達する第1遅延素子と、後段からの信号を反転して前段に伝達し、または前段からの信号を反転した遅延信号を反転して前段に伝達する第2遅延素子とを含む。検出回路は、奇数段目および偶数段目の遅延段において、前段からの信号を受けてから遅延信号を経て第2遅延素子から信号が出力されるまでの伝搬遅延時間をそれぞれ検出する。調整回路は、検出回路の検出結果に基づいて、奇数段目および偶数段目の遅延段の伝搬遅延時間を互いに等しくする。

(もっと読む)

パルス発生回路

【課題】入力信号にジッタが含まれていても安定した時間幅のパルスを出力する。

【解決手段】パルス発生回路は、ゲートが入力端子2に接続され、ソースが電源電圧VDDに接続されたPMOSトランジスタQ1と、ゲートが入力端子2に接続され、ドレインがPMOSトランジスタQ1のドレインに接続され、ソースが出力端子3に接続されたNMOSトランジスタQ2と、一端が出力端子3に接続され、他端が接地電圧VSSに接続された負荷インピーダンスZout1とを有する。

(もっと読む)

誤ロック防止回路、防止方法及びそれを利用した遅延ロックループ

【課題】遅延ロックループにおいて誤ロックが生じた場合、そこから抜け出すために使用される誤ロック防止回路、防止方法及びそれを利用した遅延ロックループを提供する。

【解決手段】誤ロック防止回路はハーモニックロックを検出する検出器とスタックロックを検出する検出器とで構成される。ハーモニックロック検出器は前記遅延クロックを本発明の特徴的な方法でサンプリングする複数個のフリップフロップ及び論理部で構成される。ハーモニックロック検出器では基準クロックと基準クロックから遅延された複数個の遅延クロックの立ち上がりエッジを比較してこれらの立ち上がりエッジが基準クロックの1周期から離れた場合を検出する。スタックロック検出器は位相検出器の出力信号と前記遅延クロックのうち1つを利用した論理回路であり、論理演算の結果で位相検出器をリセットさせる。

(もっと読む)

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

可変遅延回路

【課題】 遅延時間の制御信号に対する線形性の高い可変遅延回路を提供する。

【解決手段】 遅延制御回路100は、インバータINV1およびINV3に与える電源電圧VDD1−VSS1の大きさを一定値VBに保ち、かつ、インバータINV2およびINV4に与える電源電圧VDD2−VSS2の大きさを同じ一定値VBに保った状態で、前者の電源電圧VDD1およびVSS1の各電位に対して後者の電源電圧VDD2およびVSS2の各電位を所望のシフト量ΔVだけ負方向にシフトさせる。この結果、シフト量ΔVとほぼ同じシフト量だけ、インバータINV1およびINV3の論理閾値に対して、インバータINV2およびINV4の論理閾値が負方向にシフトされる。そして、インバータINV1〜INV4からなる遅延回路の遅延時間に論理閾値のシフト量に比例した変化が発生する。

(もっと読む)

可変遅延回路

【課題】1段ごとの遅延時間変化の誤差が小さい高精度の可変遅延回路の実現。

【解決手段】直列に接続された複数個の遅延ユニット20-0,20-iを有し、各遅延ユニットは、第1から第3論理ゲートを有し、第1論理ゲートG1は、前段の出力が後段の一方の入力になるように直列に接続され、他方の入力には、折り返し位置を指示する第1制御データCTN0,CTNiが入力され、第2論理ゲートG2は、一方の入力が第1論理ゲートの入力に接続され、他方の入力には折り返し位置を指示する第2制御データCT0,CTiが入力され、第3論理ゲートSGは、後段の出力が前段の一方の入力になるように直列に接続され、他方の入力には第2論理ゲートの出力が入力され、第3論理ゲートにおいて、一方の入力M1から出力Zまでの経路の遅延時間と、他方の入力M2から前出力Zまでの経路の遅延時間は、等しい可変遅延回路。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

マルチプレクサの選択から出力までの遅延を決定するためのリングオシレータ

【課題】マルチプレクサの選択から出力までの遅延を決定する方法を提供する。

【解決手段】出力リード26、選択入力リード25、第1データ入力リード23および第2データ入力リード24を有する第1のマルチプレクサ21と、出力リード30および選択入力リード29を有する第2のマルチプレクサ22とを備え、前記第1のマルチプレクサおよび前記第2のマルチプレクサは実質上同一の構造を有し、前記第2のマルチプレクサの前記出力リードは前記第1のマルチプレクサの前記選択入力リードに結合され、発振信号は前記第2のマルチプレクサの前記出力リード上に存在し、前記第1のマルチプレクサの前記出力リードは前記第2のマルチプレクサの前記選択入力リードに結合され、第1論理レベルは前記第1のマルチプレクサの前記第1データ入力リード上に常時存在し、第2論理レベルは前記第1のマルチプレクサの前記第2データ入力リード上に常時存在する回路。

(もっと読む)

1 - 20 / 179

[ Back to top ]