Fターム[5J001BB08]の内容

Fターム[5J001BB08]に分類される特許

1 - 20 / 110

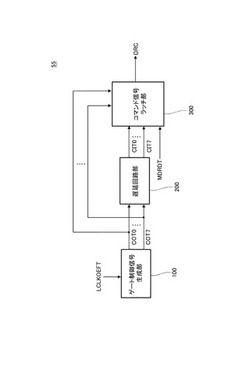

半導体装置及びデータ処理システム

【課題】外部電圧VDDの変動に伴うレイテンシカウンタのラッチマージンの低下を抑制する。

【解決手段】半導体装置は、外部クロック信号に基づいて生成される内部クロック信号LCLKOEFTと、外部から供給されるリードコマンドに応じて生成される内部リードコマンドMDRDTとを受け、内部リードコマンドDRCを生成するレイテンシカウンタ55を備え、レイテンシカウンタ55は、出力ゲート信号COT0〜COT7のそれぞれを遅延させることにより入力ゲート信号CIT0〜CIT7を生成する遅延回路部200を有し、遅延回路部200は、外部電圧VDDで動作する遅延素子と、内部電圧VPERIで動作する遅延素子とを含む。

(もっと読む)

デューティ比補正回路

【課題】入力される外部クロック信号の活性化エッジを用いてデューティ比を補正することができるデューティ比補正回路を提供する。

【解決手段】本発明のデューティ比補正回路は、第1の基準クロック信号及びリセット信号に応じて定義されるデューティ比の内部クロック信号を生成するデューティ調整手段と、第2の基準クロック信号及びフィードバックされる前記内部クロック信号に応答して前記リセット信号を生成するリセット信号生成手段とを備えることを特徴とする。

(もっと読む)

遅延回路およびシステム

【課題】 遅延段の数を切り換えるときの遅延時間の増加量および減少量を一定にすることで、高い精度を有する遅延回路を形成する。

【解決手段】 遅延回路は、直列に接続された複数の遅延段、検出回路および調整回路を有する。各遅延段は、前段からの信号を反転して後段に伝達する第1遅延素子と、後段からの信号を反転して前段に伝達し、または前段からの信号を反転した遅延信号を反転して前段に伝達する第2遅延素子とを含む。検出回路は、奇数段目および偶数段目の遅延段において、前段からの信号を受けてから遅延信号を経て第2遅延素子から信号が出力されるまでの伝搬遅延時間をそれぞれ検出する。調整回路は、検出回路の検出結果に基づいて、奇数段目および偶数段目の遅延段の伝搬遅延時間を互いに等しくする。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

パルス幅制御回路及び半導体メモリ

【課題】トランジスタのプロセス依存と配線幅のばらつきとに応じて適切なパルス幅に制御することが可能なパルス幅制御回路及び半導体メモリを提供すること。

【解決手段】配線による遅延とインバータによる遅延とを比較する比較回路と、インバータ段数によりパルス幅を調整するパルス幅調整回路と、を備える。パルス幅調整回路は、比較回路の比較結果に基づいて、インバータによる遅延が配線による遅延よりも小さくなった場合に、インバータ段数を多くし、パルス幅を増加させる。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の外部に接続される半導体チップのプロセス状態を検出して、マスク解除信号に対する制御信号のセットアップ時間またはホールド時間のマージンを大きくする。

【解決手段】 モニタモード中に、通常より低い参照電位を受信回路に供給して伝送信号の論理レベルを判定することで、半導体集積回路の外部に接続される半導体チップのプロセス状態を検出する。検出したプロセス状態に応じて可変遅延回路を制御し、内部同期信号および外部同期信号の少なくともいずれかの遅延時間を調整する。これにより、内部同期信号に応じて生成されるマスク解除信号に対する半導体チップからの制御信号のセットアップ時間またはホールド時間を、半導体チップのプロセス状態に拘わらず一定にできる。

(もっと読む)

クロックデューティ補正回路

【課題】出力されるクロック信号が発振することなく、デューティが一定になるようにクロック信号を補正することが可能なクロックデューティ補正回路を提供する。

【解決手段】クロックデューティ補正回路100は、クロック信号発生部から出力されたクロック信号が入力され、当該クロック信号の波形の立ち上がりに合わせて波形が立ち上がり、信号の周期が一定となるワンショットパルス信号を生成するワンショットパルス信号生成部110と、ワンショットパルス信号生成部110の出力信号を反転するインバータ113と、インバータ113の出力信号を遅延させる第1遅延回路114と、インバータ113の出力信号と、第1遅延回路114の出力信号との論理積を演算し、出力されるクロック信号のデューティを一定にする論理積回路116とを備える。

(もっと読む)

PWM制御装置及びモータ制御装置

【課題】電圧指令に対する出力電圧の不連続な変化を簡易に解消する。

【解決手段】PWM信号及び反転PWM信号のパルスオン時間をそれぞれ検出するパルス時間検出器40,50と、パルス時間検出器40,50が検出したパルス時間と所定のデッドタイムを比較し、パルスオン時間がデッドタイム未満の時はそのパルスオン時間を、デッドタイム以上の時はデッドタイムをディレイ時間としてそれぞれ出力する比較回路60,70と、比較回路70からのディレイ時間に基づき、PWM信号の立ち上がりをディレイさせて駆動信号(PWM_U信号)を生成する可変ディレイ回路80と、比較回路60からのディレイ時間に基づき、反転PWM信号の立ち上がりをディレイさせて駆動信号(PWM_nU信号)を生成する可変ディレイ回路90とによってPWM制御装置を構成する。

(もっと読む)

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

ディレイ回路及び信号遅延方法

【課題】 安定したディレイ時間を有するディレイ回路を提供する。また、面積を小さく占めるディレイ回路を提供する。

【解決手段】 クロック信号を受信して入力信号を順次所定時間の間隔で遅延させて複数の第1ディレイ信号を生成するディレイ部と、一つ以上の選択信号によって前記複数の第1ディレイ信号のうち一つを選択して第2ディレイ信号として出力するオプション部と、を含むディレイ回路を提供する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】入力クロックの周波数変化に依存して変調プロファイルが変化しないスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、切替信号に応じて入力クロックを遅延し、出力クロックとして出力する遅延ラインと、入力クロックの周期を計測する入力クロック周期計測部と、入力クロック周期計測部の計測結果に応じて、1変調周期当たりの出力クロックのサイクル数、および、あらかじめ設定された変調度に対応する入力クロックの所定サイクル当たりの出力クロックの周期の変調ステップ幅を算出し、算出されたクロックサイクル数および変調ステップ幅に基づいて切替信号を生成する遅延ライン制御部とを備えている。

(もっと読む)

集積回路のメモリインターフェースのためのデューティサイクル補正器回路

集積回路(IC)内のデューティサイクルの歪みを補正するための回路および方法が、開示される。ICは、クロック信号を受信するように連結されるスプリッタ回路を含む。クロック信号は、2つの異なるクロック信号に分割される。クロック信号のうちの1つは、他方の反転したバージョンである。遅延回路は、クロック信号の各々に連結される。遅延回路の各々は、対応するクロック信号の遅延したバージョンを発生させる。補正器回路は、クロック信号の遅延したバージョンの両方を受信するように連結される。補正器回路は、補正されたデューティサイクルを有するクロック出力信号を発生させる。  (もっと読む)

(もっと読む)

クロックジェネレータ

【課題】従来の調節可能な遅延回路と用いることにより、異なるクロック領域のクロック信号のうちの1つが出力される調節可能な遅延回路の時間遅延が変更されても、それらのクロック信号間の同期位相関係を維持することが可能なクロックジェネレータを提供する。

【解決手段】クロックが入力される遅延回路の入力と出力を切り離した後に、遅延回路の遅延時間を変更して遅延回路の入出力を再び接続させる。同期回路は、遅延回路の入力と出力が切り離された状態においても、クロックの位相関係を追跡し、適切なタイミングで遅延回路を再接続させるための指示を与える。

(もっと読む)

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

インダクタオーバーヘッドなしで共振クロック分配ネットワークの固有周波数を選択する方法

共振クロック分配ネットワークのためのインダクタアーキテクチャが提示される。このアーキテクチャにより、選択的にインダクタを切り離すことによって共振クロック分配ネットワークの固有周波数の調整が可能になり、複数のクロック周波数でエネルギ効率の良い作動が実現する。提示されたアーキテクチャは、主として統合されたインダクタを備える共振クロックネットワーク設計を対象としており、面積オーバヘッドが現れない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

ノイズ除去装置

【課題】使用環境状況の影響を受けずに、ノイズを確実に除去する。

【解決手段】n個のD型フリップフロップを直列に接続し、各D型フリップフロップの出力した信号の論理積を出力とするデジタル・フィルタ20と、m×2個のプリミティブ素子を有するインバータを直列に接続したディレイ・フィルタ30を並列に接続する。入力信号INPUTを両フィルタに入力し、AND回路40が各フィルタの出力する信号DELAYと信号ANDの論理積である信号FILTを出力する。発生期間がクロック信号の周期とDFF回路の段数に対応する期間より短いノイズをデジタル・フィルタ20が除去し、インバータ回路の遅延時間より周期の短いノイズをディレイ・フィルタ30が除去する。

(もっと読む)

半導体装置

【課題】半導体装置の面積を増やすことなく、遅延モニタリングを精度良く行い、汎用性のあるモニタ回路を配置する。

【解決手段】複数の素子及び配線でツリー状に構成された遅延回路102と、当該遅延回路102に判定信号を供給するデータ供給回路101と、遅延回路102の終点に接続されて前記判定信号の遅延状態を評価する遅延評価回路103とからなるモニタ回路100を採用し、遅延評価回路103の出力により、半導体回路の電源電圧、基板電圧、クロック周波数のうち少なくとも1つを制御する。モニタ回路100を構成する回路を半導体装置内の隙間にレイアウトツールで配置することで、面積増加を抑制しつつ、精度の高い遅延モニタリングが行えるようにする。

(もっと読む)

遅延装置

【課題】精度良く信号を遅延する。

【解決手段】遅延対象信号を遅延した遅延信号を出力する遅延装置であって、遅延対象信号を遅延させた信号を出力する遅延回路と、少なくとも一部の期間において遅延対象信号とは異なる論理値の信号を遅延回路へと入力させて、遅延回路に入力される信号の論理値毎の割合を基準割合に近付ける調整部と、を備え、調整部は、遅延対象信号および遅延対象信号を論理反転した反転信号を切り替えて遅延回路へと入力させる、遅延装置を提供する。

(もっと読む)

1 - 20 / 110

[ Back to top ]