Fターム[5J001BB12]の内容

Fターム[5J001BB12]に分類される特許

401 - 420 / 420

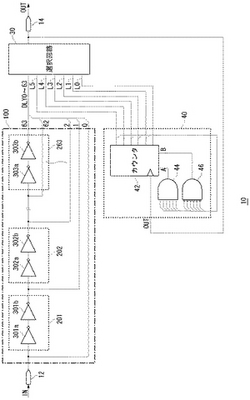

クロック制御回路

【課題】 クロック信号に起因するEMIを低減する際、ハザードやスパイクを回避するための回路設計が面倒になることがある。

【解決手段】 クロック制御回路10において、遅延回路群100は、入力クロック信号INを段階的に遅延せしめる第1〜第63遅延回路201〜263、および入力クロック信号IN自体を出力する仮の第0の遅延回路を含む。選択回路30は、第0から第63の遅延回路それぞれの出力信号DLY0〜DLY63のいずれかを選択する。制御回路40は、選択回路30によって選択された出力信号の立ち下がりや立ち上がりを契機とし、選択回路30によって異なる信号が選択されるよう制御する。これにより、入力クロック信号INに対し段階的に遅延されたクロック信号を順に出力することができ、入力クロック信号INと周期が異なる信号を出力できる。出力される信号の周波数が変化するため、スペクトルを拡散でき、EMIを低減できる。

(もっと読む)

遅延回路、半導体集積回路、位相調整回路、DLL回路およびPLL回路

【課題】 大きな遅延時間を得ることができると共に、遅延時間をきめ細かく制御することが可能な遅延回路を得る。

【解決手段】 インバータ1〜nを複数段直列接続して形成され、各P−chトランジスタ1a〜naの基板電極に電位VDDHを供給し、各P−chトランジスタ1a〜naのソース電極にスイッチ1c〜ncが接続され、そのソース電極に供給する電位として電位VDDHまたは電位VDDLを選択可能にされ、また、電位VDDHおよび電位VDDLのうちの少なくとも一方の電位は調整自在にされたものである。

電位VDDHまたは電位VDDLの電位調整、およびスイッチ1c〜ncによる電位選択に応じて、P−chトランジスタ1a〜naに逆バイアスまたは順バイアスをかけ、大きな遅延時間を得ることができると共に、遅延時間をきめ細かく制御することができる。

(もっと読む)

デジタルオーディオ用の信号伝送装置

【課題】 音質改善のためユーザーが好みに応じてデジタルオーディオ信号のパルス幅を可変できるようにしたデジタルオーディオ用の信号伝送装置を提供する。

【解決手段】 送信機1から送信されるデジタルオーディオ信号をデジタル受信機が備えるDAコンバータ2に伝送するデジタルオーディオ用の信号伝送装置10において、入力バッファ回路110および出力バッファ回路120を含み所定の直流電源130で動作する伝送器本体100と、伝送器本体の出力側から引き出されDAコンバータに接続される出力ケーブル200とを備え、入力バッファ回路110の波形成形回路(インバータ回路)112にて入力パルス波形と所定の閾値電圧との交点を立ち上がり・立ち下がりポイントとして上記デジタルオーディオ信号を立ち上がり・立ち下がり時間が速いパルス波形に波形成形する際、バイアス電圧調整回路115により例えばパルス波形の中心電圧を可変としてパルス幅の異なるパルス波形が得られるようにする。

(もっと読む)

パルス幅変調回路

【課題】

高速、高精度の動作を実現できるパルス幅変調回路を提供すること。

【解決手段】

本発明にかかるパルス幅変調回路では多相クロック生成回路2によって基準クロックに基づき多相クロック信号を生成する。そして、入力データと、多相クロック生成回路2によって生成された多相クロック信号とに基づいてパルス幅変調信号を生成する。ここで、多相クロック生成回路2は、位相ロックループ回路を有し、位相ロックループ回路によって生成された中間クロック信号をさらに位相補間することにより多相クロック信号を生成する。

(もっと読む)

パルス信号生成回路及びこのパルス信号生成回路を有するSRAM

【課題】

回路規模を縮小できるとともに、任意のパルス幅の出力パルス信号を生成することができるパルス信号生成回路及びこのパルス信号生成回路を有するSRAMを提供する。

【解決手段】

データを記憶する記憶回路と、この記憶回路を動作させる駆動回路と、この駆動回路を駆動させるための出力パルス信号を生成するパルス信号生成回路とを有するSRAMにおいて、パルス信号生成回路は、クロック信号が非アクティブ状態からアクティブ状態に切替わると、出力パルス信号を強制的にアクティブ状態に切替えるアクティブ切替え回路と、クロック信号がアクティブ状態から非アクティブ状態に切替わっても出力パルス信号の状態をそのまま保持する保持回路と、クロック信号の状態に関わらず、切替え信号が非アクティブ状態からアクティブ状態に切替わると、出力パルス信号を強制的に非アクティブ状態に切替える非アクティブ切替え回路とを有することとした。

(もっと読む)

周波数可変発振回路並びにそれを用いた位相同期回路及びクロック同期回路

【課題】低い電源電圧で動作し、かつ、高い周波数で発振することができる周波数可変発振回路並びにそれを用いた広い発振周波数範囲を有する位相同期回路及びクロック同期回路を提供すること。

【解決手段】pMOS及びnMOSトランジスタのゲートを相互に接続して入力端子とし、かつ、ドレインを相互に接続して出力端子とした相補型増幅回路を用いて差動増幅回路及び入出力端子を互いに交叉して接続した正帰還回路を構成し、差動増幅回路の出力端子間に正帰還回路を接続し、前記相補型増幅回路のソース電流を制御するための周波数制御信号をゲートに入力するMOSトランジスタと前記相補型増幅回路とを電源端子と接地端子の間に直列に接続して構成した遅延回路を環状に縦続接続して周波数可変発振回路を構成する。

(もっと読む)

進歩した位相等化を用いたDLL位相検出

【解決手段】同期回路(例えば、遅延ロックドループ即ちDLL)の初期化中にクロックのシフトモードを開始及び終了するシステム及び方法が開示されている。初期化の際に、DLLは、ForceSL(Force Shift Left)モード及びOn1xモード(即ち、クロックサイクル毎にレフトシフト)に入る。フィードバッククロックは、(システムクロックから順次供給される)リファレンスクロックの位相をトラックし、コース位相検出ウインドウに与えられる前に、最初にコース位相検出器内で遅延される。フィードバッククロックの2つの遅延バージョンが、リファレンスクロックでサンプリングされて、一組の位相情報信号が生成される。それら信号は、その後、アドバンスド等位相(APHEQ)信号を確立するために使用される。APHEQ信号は、PHEQ(位相等化)位相のオンセットを進め、ForceSLモード及びOn1xモードの終了に使用される。これによって、クロックジッタによる不適切なForceSLの終了、又はOn1xが終了する間におけるフィードバックパスのオーバーシューティングが防止される。不適切なForceSLの終了及びOn1xのオーバーシューティングの問題が避けられることで、DLLのロッキングタイムはより速くなる。 (もっと読む)

非準静的位相ロックループ分周回路

非準静的MOS分周回路は、差動入力信号を引き起こすアンテナコイル、アンテナ共振キャパシタ、整流器、電圧制御リング発振器、位相検出器およびループフィルタを含む、位相ロックループ構成を用いる。用いられる全てのトランジスタは、PMOS、NMOS、もしくはPMOSとNMOSの両方の、有機MOSデバイスである。電圧制御発振器は、複数の遅延ステージリング発振器を含む。位相検出器は、個々の発振器ステージ電圧をループフィルタにサンプリングするため、サンプリングスイッチとして接続されたトランジスタを含む。サンプリングトランジスタは、コイルに接続されたゲートを有する。ループフィルタは、ほぼ直流をループ増幅器に、そして電圧制御発振器の遅延制御入力に提供する。この構成は、アンテナ信号周波数と同調し、この約数である、電圧制御発振器周波数をもたらす。サンプリングトランジスタゲートは全て、コイルに接続され、それにより、無線周波数並列共振ネットワークのキャパシタンスの部分となる。トランジスタゲートはそこで、無線周波数信号のレートで、コイル電圧に対して遅延なく、効果的にスイッチする。位相検出有機トランジスタの動作は、トランジスタの非準静的挙動に基づく。非準静的動作は、トランジスタのユニティゲインバンド幅の準静的制限よりもずっと高い周波数における位相検出をもたらす。  (もっと読む)

(もっと読む)

パルス幅調整回路、パルス幅調整方法、及び半導体試験装置

与えられるパルス信号のパルス幅を調整した出力信号を出力するパルス幅調整回路であって、パルス信号を遅延させた第1遅延信号を出力する第1遅延回路と、第1遅延回路と異なる遅延量でパルス信号を遅延させた第2遅延信号を出力する第2遅延回路と、第1遅延回路における遅延量と第2遅延回路における遅延量の差分に応じたパルス幅を有する出力信号を、第1遅延信号と第2遅延信号に基づいて出力する出力部とを備えるパルス幅調整回路を提供する。 (もっと読む)

可変遅延回路

本発明に係る可変遅延回路は、直列に接続され、基準クロック信号又はデータ信号を順次遅延させる複数段の第1可変遅延素子と、複数段の第1可変遅延素子に並列に接続され、基準クロック信号を遅延させる第2可変遅延素子と、複数段の第1可変遅延素子によって遅延された基準クロック信号の位相を、第2可変遅延素子によって遅延された基準クロック信号の位相とを比較する位相比較器と、位相比較器の比較結果に基づいて、複数段の第1可変遅延素子によって遅延された基準クロック信号の位相を、第2可変遅延素子によって遅延された基準クロック信号の所定のサイクル後の位相と略等しくすべく、複数段の第1可変遅延素子のそれぞれの遅延量を制御する遅延量制御部とを備える。 (もっと読む)

クロック信号の補正に適したクロック信号入出力装置

本発明は、クロック信号入出力装置(1、101)に加えて、クロック信号補正方法に関するものである。本発明の方法では、クロック信号(clk)または該クロック信号から得られた信号を、上記装置に入力し、分周器(4、104)に伝送し、分周器(4、104)から出力された信号、または、該信号から得られた信号(clk2)を、信号積分器(6、106)に伝送し、該信号積分器(6、106)から出力されるか、または、該信号から得られた信号(I2)を、第1信号比較回路(8、108b)に伝送する。さらに、分周器(4、104)から出力された信号、または、該信号から得られた信号(clk2)を、第2信号比較回路(9、109a)に伝送し、クロック信号用の入出力装置(1)は、第1信号比較回路(8、108)から出力された、または、該信号から得られた信号(rIclk)に応じて、および、第2信号比較回路(9、109a)から出力された、または、該信号から得られた信号(rclk)に応じて、クロック出力信号(clk50)を出力するための、信号出力回路(11、111)を備えている。  (もっと読む)

(もっと読む)

遅延ロックループ位相混合回路

例えば遅延ロックループ(DLL)回路において、位相を微調整するための技術および回路構成を提供する。1つまたは複数の遅延素子を電流源の出力ノードと選択的に接続することにより、複数の位相信号を、単一の電流源から生成するようにすることができる。遅延素子は、電流源を切り替えることによって生成される信号のタイミングを変更するようにすることができる。  (もっと読む)

(もっと読む)

制御された等しい遅延時間を有する分離バッファ

分離バッファにおける遅延を制御するシステムを提供する。そのような複数の分離バッファ(501および502)は、複数のラインに単一の信号チャネル(42)を接続するために用いられ、等しい遅延を提供するように制御される。分離バッファ遅延は、電源電圧または電流を変化させることによって均一になるように制御される。遅延ロックループを形成する単一の遅延制御回路(70)は、均一な遅延を確保するために各バッファに遅延制御信号を供給する。遅延の制御は各分離バッファの出力電圧を変化させ得るので、一実施形態では、バッファは2つの直列インバータから作成される。一方は可変遅延を有し、第2のインバータは可変遅延なしで固定出力電圧スイングを提供する。必要な回路を低減するために、一実施形態では、可変電源を備えた分離バッファは、分岐の前においてチャネルに提供され、その一方で、固定遅延を有するバッファは各分岐に提供される。  (もっと読む)

(もっと読む)

半導体装置及び電圧制御発振回路

電圧制御発振回路(15)内に互いに異なる段数の独立した複数のリング発振回路を設け、セレクタ(22)により何れか1つのリング発振回路の出力を帰還クロック信号(FB)として選択的に出力することで、独立しているリング発振回路の出力が常に帰還クロック信号として出力されるようにして、動作速度が高速であってもデューティ比が崩れていない帰還クロック信号を出力でき、入力信号(DLLI)が出力されるまでの遅延時間を任意に調整できるようにする。  (もっと読む)

(もっと読む)

半導体集積回路装置

半導体集積回路装置1において、シフトレジスタSR1のフリップフロップFF64の出力とシフトレジスタSR2のフリップフロップFF65の入力との間を電気的に接離するトランジスタスイッチSWAと、入力ドライバDin2とフリップフロップFF65の入力との間を電気的に接利するトランジスタスイッチSWBを備える。このとき、シフトレジスタSR1,SR2を連結するとき、選択信号によってトランジスタスイッチSWAをONとするとともにトランジスタスイッチSWBをOFFとする。 (もっと読む)

多電源半導体装置

複数のブロック31、32により構成され、各ブロック31、32が独立したクロック回路41、42を有し、可変電源101により動作する多電源半導体装置において、クロック生成回路10から複数のブロック32に供給されるクロック信号に、可変電源101の電圧値に基づいて遅延量が変化する可変遅延回路20を設ける。このことにより、可変電源101の電源電圧を変化させた場合でも、ブロック間のクロックスキューが低減される。 (もっと読む)

クロックパルス幅調整回路

【課題】半導体集積回路の動作速度を保証すると共に、ダイナミック回路の動作時のピーク電流が単一時間に集約されることを防ぎ、EMIを抑制することを目的とする。

【解決手段】トランジスタ駆動能力測定回路333によりプロセスのばらつきによるトランジスタの駆動能力を測定し、クロックパルス変更回路444にて測定結果に基づいてクロックパルスの立ち上がりおよび立ち下りのタイミングを変更することにより、最適なタイミングでダイナミック回路251を動作させることができ、半導体集積回路の動作速度の保証を行うことができる。

(もっと読む)

可変遅延生成回路

【課題】 電流制御型発振回路4から出力されるクロック8の遅延量を細かく設定する。

【解決手段】 制御電圧1を入力し、この制御電圧1の大きさに対応した可変電流3を出力するV/Iコンバータ2と、可変電流3を入力し、この可変電流3の大きさに対応した周波数のクロック8を出力する電流制御型発振回路4と、クロック8、及び可変電流3を入力し、この可変電流3の大きさに対応した遅延をクロック8につけて出力する電流制御型遅延回路9とを備えるものとした。

(もっと読む)

DUTY補正回路

【課題】 波形歪みが補正された信号を用いて復調を行うことによりビット誤り率の低いDUTY補正回路を提供する。

【解決手段】 波形の形状を観測することで、波形歪を検出することにより歪補正を行うので、受信マンチェスタ信号のDUTY比が50%を維持できない場合でも本DUTY補正回路を使用することで、補正信号は50%近傍となり、より精度の高い再生クロックを作成することができる。また、精度の高い再生クロックと波形歪みが補正された信号を用いて復調を行うことで、ビット誤り率の低い復調が可能となる。

(もっと読む)

半導体装置

【課題】 外部クロックを用いずにディレイ部を動作することができ、極端に長いパルス幅が必要なときでも回路規模を大きくすることなく構成可能な半導体装置を提供する。

【解決手段】 ディレイパルス発生トリガ信号(DPT)を起点にして、所望のパルス幅の時間内に中間キャリー(CARRY0,1,2)信号とディレイ出力信号の終期を決定するための最終キャリー信号(CARRY END)を出力するカウンタ5と、カウンタ5からの中間キャリー信号に基づく信号とDPTに基づいてカウンタ5をカウントアップさせるためのカウントアップ信号(COUNT UP)を出力するディレイ回路4を備え、外部クロックを用いずにディレイ出力が得られるようにする。

(もっと読む)

401 - 420 / 420

[ Back to top ]