Fターム[5J001BB24]の内容

Fターム[5J001BB24]に分類される特許

21 - 40 / 64

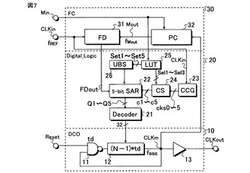

半導体集積回路

【課題】クロック信号生成部をディジタル制御するレジスタへの制御情報の格納ステップを削減すること。

【解決手段】半導体集積回路は、クロック信号CLKmを生成するディジタル制御信号生成部10、ディジタル制御部20を具備するクロック生成部を含む。クロック生成部は、位相周波数比較器31、制御レジスタ22を更に具備する。比較器31には、基準信号CLKinとフィードバック信号Moutが供給される。制御レジスタ22に比較器31の出力信号FDoutが供給され、制御レジスタ22は複数ビットのディジタル制御情報を格納する。クロック生成部は、複数のロック動作のための複数の初期設定データを予め格納する制御データ記憶回路25を更に具備する。動作選択情報Minに応答して制御データ記憶回路25から初期設定データSet1〜Set5が、制御レジスタ22の上位ビットに格納される。

(もっと読む)

位相同期発振器

【課題】PLLの位相雑音を低減すること。

【解決手段】電圧制御発振器と、該電圧制御発振器の出力信号と基準信号との位相比較を行い、該位相差に基づいて前記電圧制御発振器に与える電圧を制御する位相比較器とを備える位相同期発振器に、電圧制御発振器の出力信号に対して可変の遅延時間を与える遅延制御手段と、位相比較器で検出した位相差に応じて遅延制御部が出力信号に与える遅延時間を制御する遅延時間制御手段とを有する。

(もっと読む)

クロック信号生成装置及び方法

【課題】比較的小さな回路規模で、入力された多相クロック信号から所望の位相のクロック信号を生成する。

【解決手段】入力された多相クロック信号から所望の位相のクロック信号を生成する装置において、中間クロック生成器(11)は、多相クロック信号のいずれか一つを基準クロック信号として、基準クロック信号の複数周期を1周期とする多相中間クロック信号を生成する。第1の位相セレクタ(12)は、多相中間クロック信号のいずれか一つを選択する。第2の位相セレクタ(13)は、多相クロック信号のいずれか一つを選択する。ラッチ回路(14)は、第1の位相セレクタ(12)によって選択された中間クロック信号を、第2の位相セレクタ(13)によって選択されたクロック信号でラッチする。

(もっと読む)

パルス発生回路およびUWB通信装置

【課題】立ち上がり、立ち下りのエッジで起動されたパルス間で振幅が異なり、正負の対称性がずれる。

【解決手段】起動信号を所定量の遅延を伴って論理反転する縦続接続された複数のインバータからなるインバータ遅延回路と、出力端子を、インバータ遅延回路の出力Di,XDi−1の論理積が真のとき第一の電位に接続し、出力Di,XDi+1の論理和が偽のとき第二の電位に接続する第一のスイッチ回路と、出力端子を、出力Di,XDi+1の論理積が真のとき第一の電位に接続し、出力XDi+1,Di+2の論理和が偽のとき第二の電位に接続する第二のスイッチ回路と、第一のスイッチ回路が活性化されるとき起動信号をインバータ遅延回路の1段あたりの遅延量と同一の時間遅延させ、第二のスイッチ回路が活性化されるとき遅延させないで起動信号をインバータ遅延回路に入力する起動信号制御回路とを備える。

(もっと読む)

信号発生器、画像読取装置および画像形成装置

【課題】不要輻射強度の不具合への対策で周波数拡散を行った場合に生じる不具合を解消することができる信号発生器および画像読取装置を提供すること目的とする。

【解決手段】時間的に連続したクロック信号を発生させるクロック信号発生手段と、前記クロック信号発生手段にて発生されたクロック信号を周波数変調させて周波数拡散クロック信号を発生させる周波数拡散クロック信号発生手段を有する信号発生器において、前記周波数拡散クロック信号発生手段により生成した周波数拡散クロック信号から、周波数拡散の影響の無い固定遅延を生成し、生成したその遅延量に応じて前記周波数拡散クロック信号の位相を遅延させる信号遅延手段を備えた。

(もっと読む)

モータの速度制御システム、モータの制御回路、及びモータ

【課題】PWM周期を変動可能であり、かつ、負荷の運転状態に応じてデューティ比を設定可能な、フルロジックで形成可能PWM制御システムを提供する。

【解決手段】基本周波数信号を分周してPWM基本波を形成するPWM基本波発生手段12と、PWM基本波に基づいてPWM周期を設定するPWM周期設定手段22と、PWMの周期内のデューティ比(N/M:N≦M,Mは最大クロック数)を形成するデューティ比形成手段24と、このデューティ比を持ったPWM制御信号を負荷の駆動回路に出力するPWM制御信号出力手段と、を備えた。

(もっと読む)

信号遅延回路

【課題】回路規模が小さく消費電流が少ない信号遅延回路の提供

【解決手段】圧縮回路32は、入力信号n1を例えば14個単位で区切り、これを5ビットのデータに圧縮し、動作クロックn2の14分の1のレートで圧縮データn5を生成する。低速動作シフトレジスタ33は、圧縮回路32からの圧縮データn5を、この圧縮データn5のデータ生成レートと同じく動作レートの14分の1のレートで16段分だけ遅延させた遅延圧縮信号n6を生成する。伸張回路34は、遅延圧縮信号n6に基づいて圧縮データn5を元のデータに伸張する。

(もっと読む)

通信装置、ベースバンド信号処理装置及び受信処理方法

【課題】入力信号におけるデューティ比の制約を無くし、コストや基板面積や回路設計上の制約を取り払うことができる通信装置、ベースバンド信号処理装置及び受信処理方法を提供する。

【解決手段】VCTCXO16と、VCTCXO16からの第1クロック信号aを分周するクロック分周回路27と、クロック分周回路27から出力された分周クロック信号bが入力され、入力された分周クロック信号bを所定倍して第2クロック信号cを生成するPLL部28と、PLL部28で生成された第2クロック信号cによってベースバンド信号処理を行うベースバンド信号処理部22と、を含む。第1クロック信号aと第2クロック信号cとが同じ周波数となるように生成する。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックに応答して1ビットずつレベル遷移する複数のビットの周波数制御信号を生成する周波数制御信号生成部と、及び前記複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。また、他の発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

デューティ比制御高周波生成回路

【課題】 簡素な構成で温度変化による影響を受け難いデューティ比制御高周波生成回路を提供すること。

【解決手段】 基本駆動方形波生成回路部5と、該基本駆動方形波の前縁微分信号を生成する微分信号生成回路部9と、出力周波数の半周期に該当する期間内の信号幅を有する方形波信号を出力する方形波信号生成器10並びに制御信号に基づいて前記方形波信号の信号幅を可変制御する信号幅制御回路とを有するバイブレータ回路部15とを含むデューティ比制御高周波生成回路において、信号幅制御回路は、方形波信号生成器に含まれる第1の反転器10からの出力信号を反転して当該第1の反転器に入力させる第2の反転器11と、固定抵抗R3と固定コンデンサC1で構成された固定時定数回路部12を有し、該固定時定数回路部に入力される制御電圧信号と固定時定数回路部12が有する所定の時定数により決定される時間において、第2の反転器11からの出力の第1の反転器10への入力を遮断する。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】デューティ補正された遅延固定クロックを生成することができ、1つのDLLだけでもデューティ補正が可能で、かつ、入力されるクロック信号のデューティ比を効率的に補正して出力することができる半導体メモリ装置を提供すること。

【解決手段】遅延固定動作により遅延固定クロックを生成するDLL回路と、前記遅延固定クロックと、その遅延固定クロックの偶数倍に分周したクロックとを用いて、前記遅延固定クロックのデューティ比を補正するデューティ補正回路とを備える半導体メモリ装置を提供する。

(もっと読む)

分周クロック生成回路

【課題】クロック配線の末端においてもシステムクロックと分周クロックとの間に位相の逆転現象が発生しない分周クロック生成回路を提供する。

【解決手段】分周クロック生成回路1は、システムクロックFPHを分周した基本分周クロックPHを出力する分周器11と、クロック配線末端におけるシステムクロックFPHDの位相が基本分周クロックPHの位相に対して遅れているか進んでいるかを判定して判定信号SELを出力する位相判定回路12と、基本分周クロックPHを配線末端のシステムクロックFPHDに同期させた上で遅延させた遅延分周クロックPHTを出力する同期遅延回路13と、位相判定回路12から出力される判定信号SELが位相遅れを示すときは遅延分周クロックPHTを選択し、判定信号SELが位相進みを示すときは基本分周クロックPHを選択して、分周クロックPHSとして出力する選択回路14と、を備える。

(もっと読む)

ジッタ低減回路

【課題】本発明は、高い信号周波数においても、消費電力、回路規模、及びコストの観点から効率的に信号レベルとタイミングとを回復可能なジッタ低減回路を提供することを目的とする。

【解決手段】ジッタ低減回路は、第1の信号が伝搬する複数の区間からなる信号線と、信号線の複数の区間に対応して設けられ第2の信号を伝搬させる複数の遅延線を含み、複数の遅延線の各遅延線における第2の信号の遅延量は、複数の区間のうちの対応する1つの区間における第1の信号のレベルが第1のレベルの場合に第1の遅延量となり、当該1つの区間における第1の信号のレベルが第2のレベルの場合に第2の遅延量となるように複数の遅延線が構成されることを特徴とする。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】電源電圧が変動してもスキューやデューティ変動の生じにくい多相式のDLL回路を提供する。

【解決手段】分周信号CK1の遅延量を調整する遅延調整回路111と、分周信号CK2の遅延量を調整する遅延調整回路112と、遅延調整回路111,112の出力を合成することにより内部クロックLCLKを生成し、これを正規パス131に供給する合成回路121と、遅延調整回路111の出力を受け、これをレプリカパス132に供給するクロックドライバ122と、遅延調整回路112の出力を受けるクロックドライバ123とを備え、クロックドライバ122,123が実質的に同一の回路構成を有している。これにより、電源電圧が変動した場合であっても、その影響が各分周信号に対してほぼ均等となる。このため、電源変動によるDLL回路の機能低下を防止することが可能となる。

(もっと読む)

クロック生成装置

【課題】クロック生成装置において、リングオシレータが高温になるのを抑える。

【解決手段】クロック生成装置10は、リングオシレータ13の出力信号を割り算器19が算出した分周比で分周する第一分周器21と、第一分周器の出力信号をニ分周する第二分周器23と、リングオシレータの出力信号のパルス数を所定時間計測するカウンタ15,25と、割り算器と、比較器29とを備える。割り算器は、第一分周器からの出力信号が、所定周波数のクロック信号となるよう第一分周器に設定する分周比を演算する。一方、比較器は、カウンタのカウント値と閾値とを比較し、カウント値が閾値以上である場合、第二分周器に入力するイネーブル信号をオフにして、第二分周器の分周機能をオフし、カウント値が閾値未満である場合には、イネーブル信号をオンにして、第二分周器の分周機能をオンにする。これにより、リングオシレータが高温の時、クロック周波数を半減させる。

(もっと読む)

DLL回路

【課題】第1のクロック出力をLPFで平滑化した値と、第1のクロック信号を遅延した第2のクロック信号の位相比較を行い、位相比較器の出力結果であるUP/DN信号のエッジを1/2に分周したクロック信号の出力をLPFで平滑化した値を、オペアンプを用いた負帰還制御で調整するDLL回路を提供する。

【解決手段】第1のクロック信号PH0をLPF20で平滑化した第1の電圧値と、位相比較した出力信号のエッジを検出し、かつその検出結果を論理和出力した信号を1/2に分周した信号をLPF21で平滑化した第2の電圧値と、をオペアンプ22に入力し、このオペアンプ22の出力電圧で、第1と第2の平滑化した電圧が同じになるように、前記充/放電電流を調整する。

(もっと読む)

クロック生成回路

【課題】

要求されるデューティ比の同期クロック信号を生成できるか否かの判別が正確に行われるクロック生成回路を提供する。

【解決手段】

クロック生成回路100において、外部から入力されてきた外部クロック信号Sextclkを遅延することにより外部クロック信号Sextclkに同期した同期クロック信号Sclkを生成するDLL回路110と、DLL回路110のデューティ比劣化テスト用にパルス幅を変化させたテスト信号Stestを生成するテスト信号生成回路120と、外部クロック信号Sextclkおよびテスト信号Stestのうちの一方の信号を選択してDLL回路110に入力する選択回路130とを備えたことを特徴とする。

(もっと読む)

90度移相器

【課題】矩形波に近い波形を有し、デューティ比が50%からずれているクロック信号であっても、90度位相差を有する出力信号を生成可能な90度移相器を提供する。

【解決手段】90度移相器1は、ハイパスフィルタ(HPF)13及び分周回路10を備える。HPF13の利得傾斜特性(減衰特性)は、周波数の増加に応じて利得が増加する正の利得傾斜を有する。分周回路10は、2つのDラッチ11及び12が従属接続されたTフリップフロップを用いて構成されており、前記ハイパスフィルタによって補正された差動クロック信号を入力し、補正された差動クロック信号に対して周波数が1/2であって互いに90度の位相差を持つ4相信号を出力する。

(もっと読む)

位相シフト回路

【課題】入力信号の位相をほぼ入力信号の1周期において任意に遅延させると共に、安定した出力信号を得ることが可能な位相シフト回路を構成する。

【解決手段】D端子の最初の立上りのタイミングでローレベルの信号を出力するDFF8と、D端子の立上りのタイミングでハイレベルの信号を出力するDFF9と、DFF8またはDFF9の出力信号がハイレベルのときハイレベルの信号を出力するOR回路10と、OR回路10の出力信号に応じてオン、オフするMOSFET11と、MOSFET11がオフのとき出力信号のレベルを上昇させ、MOSFET11がオンすると出力信号のレベルを低下させるコンデンサ13と、出力信号のレベルが低下するとローレベル、出力信号のレベルが上昇するとハイレベルの信号をDFF9のR_端子に出力するためのコンパレータ3とを備える。

(もっと読む)

入力回路および該入力回路を有する半導体集積回路

【課題】定常状態になるまでに所定の時間を要する内部回路を予め動作させることで無駄な時間(ロックオン時間)の低減を図る。

【解決手段】入力する外部制御信号CLKを受け取って内部制御信号S1を出力する入力バッファ210と、前記外部制御信号が動作しているか否かを検知する制御信号検知回路220とを具備し、前記入力バッファは、該入力バッファを制御する回路251〜253を介した前記制御信号検知回路の出力により、前記外部制御信号が動作している時には前記内部制御信号を出力するように構成する。

(もっと読む)

21 - 40 / 64

[ Back to top ]