Fターム[5J022AB01]の内容

アナログ←→デジタル変換 (13,545) | D/A、局部D/A変換器の型式 (1,044) | D/A非特定 (373)

Fターム[5J022AB01]に分類される特許

1 - 20 / 373

DACの直線歪補正回路

AD変換回路及びその補正方法

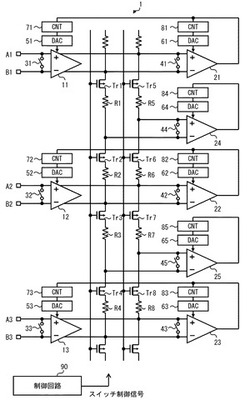

【課題】精度の高いAD変換を行うことがが可能なAD変換回路を提供すること。

【解決手段】本発明にかかるAD変換回路は、プリアンプ11,12と、コンパレータ21,22,24と、スイッチ31,41と、トランジスタTr1,Tr5と、スイッチ41をオンした場合におけるコンパレータ21の比較結果に基づいてコンパレータ21のオフセット電圧を補正する第1補正部と、スイッチ31をオンし、スイッチ41及びトランジスタTr1,Tr5をそれぞれオフした場合におけるコンパレータ21の比較結果に基づいてプリアンプ11のオフセット電圧を補正する第2補正部と、を備える。

(もっと読む)

AD変換回路及びAD変換方法

【課題】ビット判定時に比較部での比較時間が長くなることによりAD変換時間が長くなることを抑制する。

【解決手段】アナログ電圧生成部11が、受信したアナログ信号を外部クロック信号Φsに同期してサンプリングし、制御信号に基づいて第1のアナログ電圧及び第2のアナログ電圧を生成し、比較部12がクロック信号Φcに同期して第1のアナログ電圧と第2のアナログ電圧の大きさを比較し、制御部13が第1のアナログ電圧と第2のアナログ電圧の電圧差を縮小させていき、比較部12の比較結果に基づいて、外部クロック信号Φsに同期してサンプリングされたアナログ信号に応じたデジタル信号を生成し、中心電圧調整部15が、クロック信号Φcの信号遷移の回数が閾値以上になると、比較部12の入力トランジスタに流れる電流が増加するように、第1のアナログ電圧と第2のアナログ電圧の中心電圧を調整する。

(もっと読む)

結合されたディジタル対アナログコンバータおよび信号フィルタ

【課題】多様な応用、および超広帯域の応用において使用されることができるアナログローパスフィルタを提供する。

【解決手段】ディジタル信号201を処理する電子回路は、各々がディジタル信号の遅延されたレプリカを生成するように構成されている複数のディジタル遅延回路203,205,207と、各々がディジタル信号または遅延回路の1つからの遅延されたレプリカをアナログ信号へ変換するように構成されている複数のディジタル対アナログコンバータ211,213,215,217と、各々がディジタル対アナログコンバータからのアナログ信号を利得係数によって調節するように構成されていて、かつ各々が出力をもつ複数のアナログ利得回路221,223,225,227と、アナログ利得回路の出力を加算するように構成されているアナログ加算器231とを含む。

(もっと読む)

アナログデジタル変換装置及びアナログデジタル変換方法

【課題】変換対象であるアナログ信号の信号特性に応じた分解能でデジタル信号に変換でき、かつ、その際の消費電力が削減できるようにする。

【解決手段】入力信号G1の所定の特性を検出する信号特性検出部6と、信号特性検出部により検出された信号特性に基づき分解能を設定し、該分解能のアナログデジタル変換に必要な動作のみを指示する制御信号G10を生成し、出力する制御信号生成部7と、複数のレジスタ値が格納されて、レジスタ値に対応したレジスタ信号を出力する逐次比較レジスタと、レジスタ信号をアナログ信号に変換して、基準電圧信号として出力するデジタルアナログ変換器と、入力信号と基準電圧信号とを比較して比較結果信号を出力するコンパレータと、を備える。

(もっと読む)

逐次比較型AD変換器及びその制御方法

【課題】SubDACの出力端子につながる4端子コンパレータのトランジスタのゲート容量が所望の容量比となるように制御して補正し、高精度化を可能とする逐次比較型AD変換器を提供する。

【解決手段】探索範囲を設定するデジタル値DSRを受け、対応する電圧を出力するMainDAC102,103と、探索範囲を設定するための制御信号を受け、対応する電圧を出力するSubDAC101と、MainDAC102,103とSubDAC101からの電圧の比較を行う4端子コンパレータ105,107、MainDAC+(102)と、MainDAC−(103)の出力電圧を比較するコンパレータ106と、切替制御信号に基づきSubDAC101の出力A1,B1,D1,E1又はコモン電圧VCMに切り替えるセレクタ104と、セレクタ104に切替制御信号を与える逐次比較レジスタロジック108を備える。

(もっと読む)

データ処理装置、データ処理システム及び電力量計

【課題】増幅回路を用いてAD変換の分解能を拡大するAD変換技術において増幅回路のゲインに対する校正精度を向上させる。

【解決手段】目的ゲイン2n(nは正の整数)に対する前記増幅回路の実際のゲインを実測ゲインとして計測するゲインキャリブレーション処理を行い、アナログ信号を増幅回路で増幅してからAD変換回路で変換してビット拡張された変換データを取得する拡張AD変換処理において、前記増幅回路で増幅してから前記AD変換回路で変換して得られるデータに前記実測ゲインに対する前記目的ゲイン2nの比に応じた操作を施すことによってゲインに起因する誤差を相殺する。前記ゲインキャリブレーション処理では、デジタル的に既知の校正データに応ずる校正信号を目的ゲイン2n倍した信号のAD変換結果に対して、上記校正データをN倍した信号を増幅せずにAD変換して当該変換結果の1/Nの値を用いて、前記実測ゲインを求める。

(もっと読む)

半導体装置、その検査方法および送信回路

【課題】光結合部の伝送マージンを確保して復調誤りを抑制し、高精度の信号伝送を可能とする半導体装置、その検査方法および送信回路を提供する。

【解決手段】半導体装置100は、アナログディジタル変換部3と、ディジタル信号に応じたパルスパターンである伝送信号を出力するパルス幅変調部5と、固定パルスである参照信号を生成する参照信号生成部7と、を備える。そして、前記伝送信号および前記参照信号のいずれかを選択する第1の制御部13と、前記伝送信号または前記参照信号に基づく駆動電流を出力する発光素子駆動部9と、前記伝送信号または前記参照信号基づく光信号を放出する発光素子15と、を備える。さらに、前記光信号を電圧信号に変換する光受信部21と、前記電圧信号を前記伝送信号または前記参照信号に基づくディジタル信号に復調する復調部25と、を備える。

(もっと読む)

半導体集積回路装置

【課題】レベル変換回路のレイアウト面積の縮小を図る。

【解決手段】半導体集積回路装置(10)は、レベル変換回路(14)と、D/A変換回路(12)とを備える。このとき、パラレル形式のデジタル信号をシリアル形式に変換して上記レベル変換回路に供給するためのパラレル・シリアル変換回路(15)と、上記レベル変換回路の出力をパラレル形式のデジタル信号に変換して上記D/A変換回路に供給するためのシリアル・パラレル変換回路(13)とを設ける。上記レベル変換回路は、シリアル形式のデジタル信号に対応するレベル変換機能を備えていれば良く、パラレル形式のデジタル信号に対応させる場合に比べて、レベル変換回路のレイアウト面積を縮小することができる。

(もっと読む)

オーディオ信号伝送装置

【課題】 I2S信号をパルストランスを使用して絶縁すること。

【解決手段】 オーディオ信号が無音(振幅値が0V)である場合に、DATA信号のLチャンネルのデータDLiは、「00000000・・・」と「0」が続き、直流信号となってしまう。しかし、変調部2で生成される第2のLチャンネルオーディオ信号は、LRCK信号のハイレベルの期間においては「00000・・」であり、LRCK信号のローレベルの期間においては「11111・・」であるので、その結果、第2のLチャンネルオーディオ信号は交流信号と見なすことが可能となる。従って、第2のLチャンネルオーディオ信号を、パルストランス3を使用して絶縁することができる。

(もっと読む)

データ処理システム

【課題】比較的簡単な構成により分解能を向上させ回路特性の誤差の影響を縮減してDA変換を行う。

【解決手段】夫々に校正データを与えた複数個のDA変換回路(DAC1,DAC2)の出力を所定の重みをつけて前記加算回路(2)で加算し、前記加算回路の出力を前記AD変換回路でデジタル値に変換し、変換されたデジタル値に基づいて所定の重みに許容外の誤差があることを判別したときは、当該誤差の影響を縮小する方向に変換対象のデジタル信号を補正するための補正係数を取得する校正処理を制御する。変換対象のデジタル信号を高精度にアナログ信号に変換するときは、変換対象のデジタル信号を前記補正係数を用いて補正して前記複数個のDA変換回路に与え、これによるDA変換出力を前記加算回路で加算する。

(もっと読む)

荷電粒子ビーム描画装置及びDACアンプの安定化方法

【課題】帰還抵抗に対して予め当該帰還抵抗が設けられているDACアンプに対して設定される最大値の電圧を印加しその発熱状態を標準状態とすることで、出力電圧の変化が生じても電子ビームに対する影響を最小限に抑え高精度な描画処理を行うことができる荷電粒子ビーム描画装置及びDACアンプの安定化方法を提供する。

【解決手段】荷電粒子ビームBを用いて移動可能なステージ上に載置される試料にパターンを描画する描画部2と、荷電粒子ビームBの光路に沿って配置される偏向器に電圧を印加するDACアンプ34,35と、DACアンプ34,35に対する制御を行うDACアンプ制御部31jを備える制御計算機31と、から構成される制御部3と、を備え、DACアンプ制御部31jは、DACアンプ34,35に印加する電圧を当該DACアンプ34,35に対して設定される最大値で継続して印加する。

(もっと読む)

DA変換装置

【課題】より高精度でビット拡張ができるDA変換装置を提供する。

【解決手段】DA変換装置12は、2m個のnビットのDAコンバータ14と、このDAコンバータ14からの出力を加算する演算器16と、前記DAコンバータに入力するnビットの中間データを生成するデータプロセッサ12と、を備えている。データプロセッサは、各DAコンバータ14の中間データとして、入力データの上位nビットデータに、補正値を付加したデータを生成する。補正値は、その総和が、入力データの下位mビットデータが示す値に等しくなるように設定される。

(もっと読む)

演算回路、及びA/D変換器

【課題】所望の帯域幅を確保しつつ、所望の倍率を正確に得ることができる演算回路を提供する。

【解決手段】演算回路は、入力信号を入力する入力端子と、複数個のキャパシタと、増幅入力端子と出力端子とを備え、この増幅入力端子から入力される信号を増幅して前記出力端子から出力信号を出力する増幅回路とを備えている。第1スイッチ回路は、第1制御信号に基づき導通状態となり、複数のキャパシタを入力端子と第1電圧を供給する第1電圧端子との間に並列に接続する。また、第2スイッチ回路は、第2制御信号に基づき導通状態となり、複数個のキャパシタに含まれる第1のキャパシタを増幅入力端子と第2電圧を供給する第2電圧端子との間に第1の電流経路を形成するように接続すると共に、複数個のキャパシタに含まれる第2のキャパシタを増幅入力端子と前記出力端子との間に第2の電流経路を形成するように接続する。

(もっと読む)

半導体テスト装置および半導体装置の製造方法

【課題】半導体装置のテスト用電源電圧として、複雑なパターンの電源波形を短時間で、高精度に生成する。

【解決手段】マルチプレクサ16から出力された電圧変化値ΔVは加算器17により電圧設定値保持部19に格納された電圧値が加算される。この加算結果は電圧設定値保持部19に格納される。加算回路20は加算器17の加算結果に、電圧初期値格納部18の初期値データを加算する。この加算結果は、補正器21が補正情報に基づいて補正する。制御回路26は比較器24の比較結果に基づいて補正器21のデジタルデータが上限/下限電圧になったかを判定し、到達していない場合、補正器21の信号を時間情報格納部25のデータ転送時間間隔ΔTに基づいて出力する。D/A変換器12は、その信号をアナログ信号に変換し、デバイス供給電源アナログ回路13に増幅されて電源電圧VCCとして出力される。

(もっと読む)

逐次比較型ADコンバータおよびその検査方法

【課題】ADコンバータの変換時間および検査時間を削減する。

【解決手段】

本発明にかかる逐次比較型ADコンバータ10は、アナログ入力をサンプルホールドするサンプルホールド回路13と、サンプルホールド回路13から出力された電位と基準電位とを逐次比較する比較器14と、比較器14による比較結果を記憶する逐次比較レジスタ15と、逐次比較レジスタから出力された比較結果のうち上位ビットの値を記憶するSAR上位ビットレジスタ17と、逐次比較レジスタ15から出力された比較結果の下位ビットの値に基づいて、比較器14における次回以降の逐次比較を全ビットについて行うか、または下位ビットについてのみ行うかを設定するスキップフラグ設定回路18と、を備える。

(もっと読む)

フィールド機器管理システム

【課題】フィールド機器の状態を監視するに際して、フィールド機器が接続されているアナログ通信路を通じた通信の状態を確認できるようにする。

【解決手段】機器監視ユニット15は、(1)フィールド機器10におけるアナログ通信路へのアナログ出力値についてのデジタル設定値と、(2)入出力ユニット11におけるAD変換器1153のデジタル値、及び、(3)入出力ユニット11のメモリ14に記憶されたデジタル設定値の一方との組を、それぞれデジタル通信路16を通じて取得し、取得した各値に基づいて、アナログ通信路を通じた通信の状態をチェックする。

(もっと読む)

周波数変調装置

【課題】音声信号がアナログ形式で入力される場合であっても、送信周波数をずらすことなく周波数変調を行うことが可能な周波数変調装置を提供する。

【解決手段】周波数変調装置は、アナログ−デジタル変換部(ADC)、DC除去部、中心周波数加算部、振幅−周波数変換部、デジタル−アナログ変換部(DAC)及び送信周波数変換部を具備する。DC除去部は、ADCでデジタル化された信号に含まれる直流成分を除去した減算信号を出力する。中心周波数加算部は、減算信号に、所定の周波数に対応する値を加算した加算信号を出力する。振幅−周波数変換部は、加算信号が示す振幅値情報を周波数値情報に変換する。デジタル−アナログ変換部は、振幅−周波数変換部からの信号をアナログ変換し、送信周波数変換部は、アナログ変換後の信号の周波数を周波数変換し、周波数変調信号として出力する。

(もっと読む)

アナログデジタル変換器

【課題】高速のAD変換器を提供する。

【解決手段】アナログ入力信号をデジタル出力信号に変換するAD変換器であって,アナログ入力信号と参照電圧とを比較して当該比較結果に応じたデジタル出力信号の各ビットを順次出力するN段の比較ユニットと,比較ユニットが出力するデジタル出力信号の各ビットに基づいて参照電圧に対応する参照電圧生成デジタル信号を順次生成する論理回路と,参照電圧生成デジタル信号に基づいて前記参照電圧を生成するDA変換器とを有する。そして,N段の比較ユニットは,それぞれ,前段からの状態制御信号の判定状態に応答してリセット状態から判定状態になる比較器と,比較器が判定状態で比較結果を出力したときに後段の比較ユニットへの状態制御信号を判定状態にする状態制御信号生成部とを有し,トリガクロックに応答して,N段の比較ユニットの比較器が上位のビットから下位のビットまで順次比較動作を行う。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

1 - 20 / 373

[ Back to top ]