Fターム[5J022CB01]の内容

アナログ←→デジタル変換 (13,545) | 基準電圧・バイアス系 (1,329) | 基準電圧発生回路 (518)

Fターム[5J022CB01]の下位に属するFターム

分圧・レベル調整回路 (222)

Fターム[5J022CB01]に分類される特許

281 - 296 / 296

半導体装置

【課題】

供給される基準電圧に応答して、入力されるアナログ信号をAD変換してデジタルデータを出力する半導体装置において、その基準電圧が変動するときでも、その電圧変動の影響を受けることのないデジタルデータを生成する半導体装置を提供する。

【解決手段】

基準電圧を生成する基準電圧生成回路と、その基準電圧に応答して、センサから出力される出力電圧をAD変換するAD変換回路とを具備する半導体装置を構成する。そして、その基準電圧生成回路は、基準電圧に対応するセンサ用電圧を生成して、そのセンサ用電圧をセンサ用電圧出力端子を介してセンサに供給する。

(もっと読む)

受信装置

【課題】アナログ/デジタル変換器によるクリッピングの発生頻度を抑えることが可能な受信装置を提供する。

【解決手段】クリッピング検出部215は、アナログ/デジタル変換器201,202の出力信号からクリッピングの発生状況を検出し、発生頻度が高くなると、制御部203は、GCA(Gain Control Amplifier)104を制御し、アナログ/デジタル変換器201,202への入力信号の振幅を低減させる。

(もっと読む)

電流出力型駆動回路および電子機器

【課題】比較的小規模なプログラムにより多種類の点滅パターンを実現することができる電流出力型駆動回路および電子機器を提供する。

【解決手段】制御レジスタ14に格納され、論理回路13により論理演算が行われた基準電流設定データに基づいて基準電流発生回路12の可変電流源VIS−iにより可変の基準電流IREFを出力し、電流出力型DAC2−iの基準抵抗回路Rrefに発生した基準電圧Vrefに基づいて誤差増幅回路3−iにより電流出力型DAC2−iの出力電流を制御してLED1−iを駆動する。

(もっと読む)

アナログ/デジタル変換装置およびそれが用いられたスターリング冷凍システム

【課題】 精度が高いアナログ/デジタル変換を行なうことが可能なアナログ/デジタル変換装置を提供する。

【解決手段】 マイクロコンピュータ1000のRef−A/D用端子と、電源電極Vccとに接続された定電圧回路400との間にダイオードDが接続されている。これにより、定電圧回路400の出力値Vrinに比較してダイオードDの降下電圧ΔVの分だけ低い値の電圧情報(Vrin−ΔV)がRef−A/D変換回路に入力される。このダイオードDの降下電圧ΔVの値と前述の電圧情報(Vrin−ΔV)とを用いて、M−A/D変換回路において、アナログ/デジタル変換を行なう。

(もっと読む)

サンプリング回路

【課題】 アナログ電圧信号に関するサンプリング回路において、電圧をサンプリングするコンデンサの充電を、複数のサンプリング期間にて間欠的に行うと、合間のリーク電流による放電により、コンデンサの充電が平衡状態に達しない。

【解決手段】 サンプリング期間では充放電回路10が入力電圧Vinと出力電圧Voutとの差に応じた電流でコンデンサCを充放電する。電圧ストア回路18は、サンプリング期間の終了時のVoutをA/D変換した基準電圧値を保持する。次のサンプリング期間の開始に先立って、リチャージ回路12は電圧ストア回路18から基準電圧値をD/A変換した電圧とVoutとの差に応じた電流でコンデンサCを充電し、コンデンサCのサンプリング期間の合間での放電量を補い、前回のサンプリング期間の終了時の充電量を回復する。これにより、Voutが速やかに目的サンプリング電圧に近づく。

(もっと読む)

パイプライン型A/D変換器

【課題】 高精度化と高速化を維持しつつ低消費電力化の実現可能なパイプライン型A/D変換器を提供する。

【解決手段】 アナログ入力信号をリファレンス電圧に基づいてA/D変換する第1のサブA/D変換器と、該A/D変換器からの信号をリファレンス電圧に基づいてD/A変換するサブD/A変換器と、アナログ入力信号とサブD/A変換器からの信号との差分を増幅して次段のアナログ入力信号として出力する誤差増幅器を有する複数段の処理ステージ21,22,・・・を、縦続接続すると共に、最終段に第2のサブA/D変換器26を接続したパイプライン型A/D変換器において、第2段の処理ステージ22の誤差増幅器7の増幅率を後行する処理ステージ23の誤差増幅器10よりも低い第1の増幅率に設定すると共に、後行する処理ステージ及び第2のサブA/D変換器のリファレンス電圧を第1の増幅率に応じたリファレンス電圧に調整する第1の調整回路12を設ける。

(もっと読む)

基準電圧変動補償回路及び比較器

【課題】 基準電圧の変動を減少させることができる基準電圧変動補償回路を提供する。

【解決手段】 第1入力端子、第2入力端子、及び少なくとも一つの出力端子を有する差動増幅器を含む集積回路装置が開示される。第2入力端子は、時間変動入力信号を受信するように構成される。正常状態で常にオン状態であるCMOS伝送ゲートも含まれる。CMOS伝送ゲートは、基準電圧を受信する入力端子及び差動増幅器の第1入力端子に電気的に接続されている出力端子を有する。CMOS伝送ゲートは、差動増幅器の第1入力に寄生キャパシタンスを追加することによって、キックバックノイズによる基準電圧の変動を減少させる。

(もっと読む)

前段信号処理デバイス

【課題】 デジタル−アナログ変換回路に相対的バラツキがあっても、出力信号レベルにバラツキがないようにすることを目的とする。

【解決手段】 メモリ16R,16G,16Bよりの誤差信号を第2デジタルーアナログ変換回路に供給すると共にこの第2のデジタルーアナログ変換回路のリファレンス端子に第1の基準電位V1を供給し、この第2のデジタルーアナログ変換回路の出力信号をこの第1のデジタルーアナログ変換回路13R,13G,13Bのリファレンス端子に供給するようにすると共に前段信号処理デバイスに出荷検査信号を入力したときの出力信号レベルVR,VG,VBと出荷検査装置20の第2の基準電位V2とを比較し、この出力信号レベルVR,VG,VBとこの第2の基準電位V2とが一致する誤差信号をこのメモリ16R,16G,16Bに記憶するようにしたものである。

(もっと読む)

A/D変換回路を内蔵した半導体集積回路および通信用半導体集積回路

【課題】 A/D変換回路を半導体チップに内蔵させる場合に基準電圧を生成する基準電圧生成回路の出力端子に接続する安定化容量の容量値を減らし、チップに内蔵させることができ、外部端子数の増加、チップサイズの増大を回避することが可能なA/D変換回路を内蔵した半導体集積回路を提供する。

【解決手段】 ローカルA/D変換回路(15)とローカルD/A変換回路(17,18)を有するA/D変換回路を内蔵した半導体集積回路において、ローカルA/D変換回路に必要な基準電圧を生成する基準電圧生成回路(21a,21b,21c)とローカルD/A変換回路に必要な基準電圧を生成する基準電圧生成回路(22a,22b,22c)とを別個に設けるようにした。

(もっと読む)

アナログ/ディジタル変換に使用する電荷再分配による電圧基準生成の方法および装置

アナログ/ディジタル変換に使用するためのスイッチキャパシタ回路は、電荷再分布を使用することによって、基準電圧に対して入力信号を、その基準電圧を生成する必要なしにサンプリングする。スイッチキャパシタ回路は、基準電圧を生成する間の、電力の消費を不要にする。スイッチキャパシタ回路は、コンパレータおよび論理回路に接続され、この論理回路はスイッチングのための制御信号を提供する。スイッチキャパシタ回路は、いくつかの態様に応じて配設される複数のキャパシタを含む。  (もっと読む)

(もっと読む)

パルス幅変調アナログデジタル変換

アナログ信号を精度良く確実に変換するためにパルス幅変調を使用するアナログデジタル変換方法及び装置が提供される。この方法及び装置によれば、最も厳しい環境における要求を満たすアナログデジタル変換器(ADC)が実現可能である。さらに、多くの用途で求められる高精度を満たすADCが実現可能である。この方法及び装置に係るADCは、受け取ったアナログ入力をアナログ信号入力に応じたデューティサイクルのパルス幅変調信号に変換する。パルス幅変調信号はデューティサイクル機構に送られてパルス幅変調信号のデューティサイクルが決定される。決定されたデューティサイクルにより、アナログ信号に比例したデジタル値が生成される。この好適な方法及び装置により、広範囲の環境で使用可能な正確且つ高信頼性のADCが得られる。  (もっと読む)

(もっと読む)

A/D変換器の検査装置及びA/D変換器の検査方法

【課題】高精度の検査を短時間で実施する安価なA/D変換器の検査装置及び検査方法を提供する。

【解決手段】本発明のA/D変換器の検査装置は、第1のクロックでテストデータを発生する入力コード発生器と、テストデータをD/A変換し被測定A/D変換器に入力するD/A変換器と、被測定A/D変換器を駆動する、第1のクロックのn倍(nは2以上の正整数)の周波数の第2のクロックを発生する第2のクロック発生器と、被測定A/D変換器の出力データを第2のクロックで取り込み、n個の測定データの平均値を算出する平均値算出部と、第1のクロックで平均値算出部の出力データを入力し、被測定A/D変換器の良否を判断する判断部と、を有する。

(もっと読む)

通常透過的なパイプライン・ステージを有する同期パイプライン

【課題】 同期パイプライン・セグメントと、そのセグメントを含む集積回路(IC)を提供することにある。

【解決手段】 このセグメントは、入力ステージと、出力ステージと、少なくとも1つの中間ステージとを含む。各ステージに関連するプレースホルダ・ラッチは、有効ステージ・データがそのステージに入っているかどうかを示す。ローカル・クロック・バッファは、対応するステージをゲート制御するローカル・クロックを提供する。入力ステージと出力ステージは通常非透過的であり、中間ステージは通常透過的である。データ項目は、入力ステージと出力ステージとの間をローカルに非同期式に通過し、非透過的にゲート制御された中間ステージによって分離される。

(もっと読む)

範囲エラー検出をともなうアナログ・デジタル変換器

回路(200)は、マルチプレクサ(204)、アナログ・デジタル変換器(208)およびアナログ・デジタル変換器からのデジタル出力のシーケンス(DM)を、デジタル出力と対応する正常範囲のシーケンス(217)と比較し、デジタル出力の一つが正常範囲外にあるときにエラー出力(219)を供給するためのプロセッサ(216)を含む。  (もっと読む)

(もっと読む)

双対残渣パイプライン型AD変換器

双対残差パイプライン型AD変換器は、第1および第2の残差入力信号から1ビット以上のデジタルビットと、カスケード中の次のステージへ供給するための第1および第2の残差出力信号とを生成する、好ましくは平衡型である、カスケード型のスイッチドキャパシタ双対残差変換器ステージを備えている。好ましくは、第1および第2の残差入力信号は入力キャパシタを充電し、その電荷はその後に演算増幅器によって出力キャパシタへ転送される。スイッチドキャパシタアーキテクチャは演算増幅器のDCオフセット電圧の補償を可能にする。スイッチドキャパシタアーキテクチャは1.5ビット変換器ステージの実施もまた可能にする。  (もっと読む)

(もっと読む)

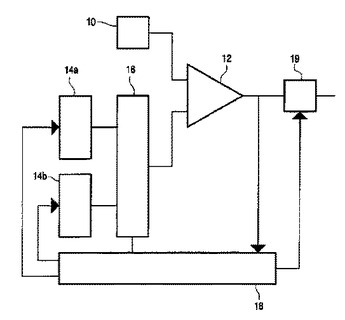

電子的センシング回路

センサ(10)は、第1の比較器入力端に結合される出力端を有する。制御回路(18)は、上方向追跡モードから、下方向相対レベル検出モード、下方向追跡モード、上方向相対レベル検出モード、そして再び上方向追跡モードに、次々に切り換わるように構成される。第1および第2のディジタル・アナログ変換回路(14a、b)は、制御回路(18)からそれぞれ第1および第2のディジタル制御値を受け取る。制御可能コンバイナ回路(16)は、第1および第2のディジタル・アナログ変換回路(14a、b)の出力端に結合された入力端と、第2の比較器入力端に結合された出力端とを有し、制御回路(18)は、コンバイナ回路(16)が、上方向および下方向追跡モードではそれぞれ第1および第2のディジタル・アナログ変換回路(14a、b)によって決まる第1および第2のコンバイナ出力信号を第2の比較器入力端に供給し、相対レベル検出モードでは第1および第2のコンバイナ出力信号の平均値に対応する第3のコンバイナ出力信号を第2の比較器入力端に供給させるために、制御可能コンバイナ回路(16)に結合された、第1の出力端を有する。制御回路(18)は比較器(12)の出力端に結合された入力端を有し、制御回路(18)は、上方向追跡モードでは、第1のディジタル・アナログ変換回路(14a)による、センシング信号の上方向変化に対する一方向性の上方向追跡を制御し、上方向追跡モードでは、第2のディジタル・アナログ変換回路(14b)による、センシング信号の下方向変化に対する一方向性の下方向追跡を制御する。  (もっと読む)

(もっと読む)

281 - 296 / 296

[ Back to top ]