Fターム[5J022CF02]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 増幅器(差動・演算) (534)

Fターム[5J022CF02]に分類される特許

81 - 100 / 534

2ステージD/Aコンバータ及びこれを用いた液晶表示装置のソースドライバ

【課題】高解像度の液晶表示装置のソースドライバに用いられる斬新なD/Aコンバータ及び液晶表示装置のソースドライバを提供する。

【解決手段】ソースドライバは2ステージD/Aコンバータを含む。この2ステージD/Aコンバータは、1ビットシリアル電荷再分配D/Aコンバータと、電圧選択手段と、ガンマ校正エキスパンディングと決定論理と、を含む。1ビットシリアル電荷再分配D/Aコンバータは、第1容量と、端末容量と、第1スイッチ回路と、第2スイッチ回路と、を含む。第1容量は容量充電節点(ノード)とロー参考電圧入力節点の間に接続される。端末容量は電荷収集節点とロー参考電圧入力節点の間に接続される。第1スイッチ回路は、容量の充電周期において、容量充電節点をロー参考電圧入力節点またはハイ参考電圧入力節点に接続する。第2スイッチ回路は、電荷の再分配周期において、容量充電節点を電荷収集節点に接続する。

(もっと読む)

2ステージD/Aコンバータ及びこれを用いた液晶表示装置のソースドライバ

【課題】高解像度の液晶表示装置のソースドライバに用いられる斬新なD/Aコンバータ及び液晶表示装置のソースドライバを提供する。

【解決手段】ソースドライバは2ステージD/Aコンバータを含む。この2ステージD/Aコンバータは、入力されたMビットのデジタルコードによってアナログ電圧を出力する。ソースドライバは、2ビットシリアル電荷再分配D/Aコンバータと、電圧選択手段と、を含む。2ビットシリアル電荷再分配D/Aコンバータは、ハイ参考(参照)電圧を受けるハイ参考電圧入力節点(ノード)及びロー参考電圧を受けるロー参考電圧入力節点を有する。電圧選択手段は、前記Mビットのデジタルコードの少なくとも一部によって前記ハイ参考電圧と前記ロー参考電圧を選択電圧に設定する。

(もっと読む)

信号処理回路及び信号処理方法

【課題】高サンプリングレートにおいて高精度でDC信号をAD変換可能な信号処理回路を提供する。

【解決手段】入力信号電圧に応じた振動幅で振動する電圧波形を生成する変調回路と、電圧波形を受け取る入力端と出力端との間を容量結合又は誘導結合するAC結合回路と、AC結合回路の出力端に現れる出力電圧をAD変換しデジタル値を出力するAD変換回路と、デジタル値に基づいて入力信号電圧のAD変換値を求める演算回路とを含む。

(もっと読む)

パイプライン型A/Dコンバータ

【課題】熱雑音および演算増幅器に要求されるオープンループゲインを大きくさせることなく、入力レンジおよびディジタル出力信号のビット数を大きくすることのできるパイプライン型A/Dコンバータを提供する。

【解決手段】サンプルホールド用のコンデンサの個数MをN分割し、さらに基準電圧をN倍することで、基準電圧を加減算するために用いることが出来るコンデンサの数を増加させて入力レンジを広げ、ディジタル出力信号のビット数を大きくする。この場合、全てのコンデンサでアナログ信号をサンプルするため、コンデンサを分割する前後で熱雑音を劣化させない。さらに、アナログ信号を増幅するための帰還素子として用いるコンデンサと、残りのコンデンサとの比はコンデンサを分割する前後で変わらないため、演算増幅器128に要求されるオープンループゲインを増加させない。

(もっと読む)

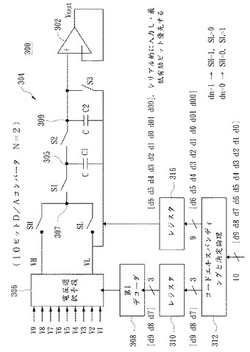

A/D変換器および信号処理回路

【課題】D/A変換機能を有するものであって、回路構成の変更を伴うことなくA/D変換およびD/A変換の分解能を変更可能なA/D変換器を提供する。

【解決手段】巡回型A/D変換器1は、外部から与えられるADC/DAC機能切替信号に応じて制御回路10がスイッチS1〜S11の切り替えを制御することにより、外部より信号入力端子3を介して入力される入力信号電圧VinをA/D変換して12ビットのA/D変換値を出力するA/D変換動作と、外部より与えられるデジタル値をD/A変換して得られるアナログ電圧Voutを信号出力端子9を介して出力するD/A変換動作とを選択的に実行可能に構成される。

(もっと読む)

受信回路

【課題】

従来のAD変換回路は動作タイミングを適切に制御できないという問題があった。

【解決手段】

入力するアナログ信号とリファレンス電圧との差分を出力する差動アンプと、リファレンス電圧が連続する差動アンプの中間電圧を補間する補間回路と、差動アンプの出力信号および補間回路の出力信号の遅延時間を可変する遅延回路と、遅延回路の出力信号を所定周波数のクロック信号に応じて二値信号に変換する判定回路と、判定回路が出力する二値信号をデジタルデータにエンコードするエンコーダ回路とを有するAD変換回路と、AD変換回路が出力するデジタル信号を等化して受信データを復号する等化復号回路と、AD変換回路の変換タイミングを変化させてAD変換回路または等化復号回路の出力信号を評価し、評価結果が予め設定した範囲内となるAD変換回路の変換タイミングを選択する調整回路とを有する。

(もっと読む)

入力モジュール

【課題】演算処理部の出力に異常レベルのノイズが重畳する状態において、その異常の要因がアナログ入力信号に重畳されたノイズによるものなのか、入力モジュールの故障によるものかを判定可能とした入力モジュールを実現する。

【解決手段】アナログ入力信号に重畳するノイズをローパスフィルタで軽減してADコンバータによりデジタル変換し、ファームウェアフィルタを備える演算処理部で処理して上位装置に出力する入力モジュールにおいて、

前記アナログ入力信号に重畳するノイズが設定された所定の閾値の範囲か否かを検出してこのノイズのレベル異常を判定する第1監視部を具備する入力ノイズ検出部と、

前記演算処理部の出力より前記アナログ信号のノイズレベルを推定演算し、これが前記所定の閾値の範囲か否かを検出してレベル異常を判定する第2監視部と、

前記第1監視部の判定出力と前記第2監視部の判定出力とを入力し、異常原因を特定して上記上位装置に出力する診断部と、

を備える。

(もっと読む)

増幅回路及びその増幅回路を含むアナログデジタル変換回路

【課題】オフセットキャンセル動作において発生する消費電力を低減可能なコンパレータを提供する。

【解決手段】差動入力信号を受ける一対のMOSトランジスタのドレインと高電位電源線に接続し、一対のMOSトランジスタのドレインに接続する差動出力ノード間の電位差を増幅し、増幅後の電位を差動出力ノードに保持する増幅部と、差動出力ノード間の電圧増幅時に、差動出力ノードにキャンセル電流を流し、増幅部による増幅動作後に、一対のMOSトランジスタのドレイン電圧に応じて差動出力ノードへのキャンセル電流の流入を遮断するキャンセル回路と、差動入力信号の一方の信号の電位を他方の信号の電位と等しく設定し、差動出力ノード間の電位差を増幅したときに、差動出力ノード間の電位が、キャンセル電流を注入する前に比較し、キャンセル電流の注入後に逆転するように、キャンセル電流を設定するコントローラと、を備える増幅回路。

(もっと読む)

パイプライン型A/Dコンバータ

【課題】レベルシフト用コンデンサ、スイッチング素子を接続することによって生じる面積の増加を抑え、チップコストを削減することのできるパイプライン型A/Dコンバータを提供すること。

【解決手段】CLS技術を用いて構成されるパイプライン型A/Dコンバータ10のある連続した2段11−n,n+1において、参照電圧との比較をエスティメートフェーズにのみ行うことでA/Dコンバータ回路のタイムシェア動作を行う。これにより、小面積でA/Dコンバータの動作を行うことができる。

(もっと読む)

パイプライン型A/Dコンバータ

【課題】レベルシフト用コンデンサ、スイッチング素子を接続することによって生じる面積の増加を抑え、チップコストを削減することのできるパイプライン型A/Dコンバータを提供すること。

【解決手段】CLS技術を用いて構成されるパイプライン型A/Dコンバータ10のある連続した2段11−n,n+1において、参照電圧との比較をレベルシフトフェーズにのみ行うことでA/Dコンバータ回路のタイムシェア動作を行う。これにより、小面積でA/Dコンバータの動作を行うことができる。

(もっと読む)

スイッチトキャパシタ回路およびパイプライン型A/Dコンバータ

【課題】CLS技術を用いて構成されるスイッチトキャパシタ回路およびパイプライン型A/Dコンバータであって、レベルシフト用コンデンサを接続することによって生じるアナログ出力電圧の急激な変化を抑え、低消費電力で動作することのできるスイッチトキャパシタ回路およびパイプライン型A/Dコンバータを提供する。

【解決手段】エスティメートフェーズからレベルシフトフェーズに移行する際、演算増幅器AMの出力をコモン電圧のレベルにリセットする。このため、演算増幅器AMの出力端子にレベルシフト用コンデンサC3を接続した際に生じるアナログ出力信号Voutの急激な変動を抑えることができる。よって、これによる消費電力の増加を抑えることができる。

(もっと読む)

A/D変換器

【課題】電圧以外の入力信号を電圧に変換した上でA/D変換することができるA/D変換器を提供する。

【解決手段】制御回路8は、初期化したコンデンサCGをオペアンプ9の入出力端子間に接続するとともにスイッチS12を開いた状態で信号電荷Sinを入力してコンデンサCGの電荷設定を行う。これにより、オペアンプ9から信号電荷Sinに応じた変換電圧が出力される。その後、コンデンサCF、CS10、CS11に変換電圧に応じた電荷を設定し、コンデンサCFをオペアンプの入出力端子間に接続した状態でA/D変換回路7の変換結果に応じてコンデンサCS10、CS11の非共通側電極を複数の基準電圧線の何れかに接続することにより各コンデンサ間で電荷再分配を行い、その後必要回数だけオペアンプ9から出力される残余電圧に応じた電荷設定と初期化それに続く電荷再分配を行う。

(もっと読む)

デジタルアナログ変換回路とデータドライバ及び表示装置

【課題】参照電圧の数の削減により面積の削減を可能とし、DNL悪化を防ぐことを可能とするデジタルアナログ変換回路、データドライバ、表示装置の提供。

【解決手段】参照電圧集合体の参照電圧を、参照電圧グループ20−1〜(zS+1)にグループ化する。デコーダ10は、参照電圧グループのそれぞれに対応して設けられ、参照電圧グループの参照電圧から、前記入力デジタル信号の第1ビットグループの値に対応する列に割当てられた参照電圧をそれぞれ選択するサブデコーダ11−1〜(zS+1)と、サブデコーダの出力を入力し、サブデコーダでそれぞれ選択された参照電圧から、前記入力デジタル信号の第2のビットグループの値に応じて、第1及び第2の電圧を選択するサブデコーダ13と、を含む。内挿回路30は前記デコーダで選択された前記第1及び第2の電圧を入力し、2つの電圧を1対1の内挿比で内挿した電圧レベルを出力する。

(もっと読む)

信号処理装置、デジタル出力マイクロホンユニット

【課題】広い温度範囲内で周囲の温度変化に対するデジタル出力の変動を安定化させる。

【解決手段】 マイクロホン(1)によって音から変換されたアナログ電気信号をデジタル電気信号にアナログ−デジタル変換して出力する信号処理装置(13)において、マイクロホン(1)から出力されたアナログ電気信号を増幅するプリアンプ(15)と、プリアンプ(15)から出力されたアナログ電気信号を基準電圧Vrefと比較してアナログ−デジタル変換するアナログ−デジタル変換器(12)と、基準電圧Vrefを生成してアナログ−デジタル変換器(12)に供給する基準電圧生成回路(14)と、を備え、基準電圧生成回路(14)は、信号処理装置(13)を構成する電気回路素子の中でその他の電気回路素子と比べてその電気的性質の温度依存性が高い素子を備え、この素子の両端子間電圧に応じた基準電圧Vrefを生成する。

(もっと読む)

デジタル/アナログ変換器(DAC)

A/D変換器

【課題】Tr.補間型比較器列を構成要素とし、プリアンプ列が出力する複数の差電圧を補間しつつAD変換するA/D変換器において、前記Tr.補間型比較器列を構成する複数個のTr.補間型比較器のオフセットをキャンセルする。

【解決手段】複数の抵抗R1〜Rmは複数の参照電圧を発生する。複数のサブ抵抗R11〜Rm4は、前記各参照電圧を更に分解する複数のサブ参照電圧を発生させる。キャリブレーション期間では、キャリブレーション対象となるTr.補間型比較器を選択すると共に、この選択されたTr.補間型比較器の閾値電圧に等しいサブ参照電圧をスイッチSW11〜SWm4により選択し、この選択したサブ参照電圧をスイッチSWAIN1、SWAIN2によりアナログ入力信号AINに代えてプリアンプ列102の各プリアンプA1〜Amに入力し、この状態でキャリブレーションを行う。

(もっと読む)

ディジタルアナログ変換器

【課題】低消費電力で信号の歪みやSNR劣化が少ないディジタルアナログ変換器を提供する。

【解決手段】シフトレジスタSREG、1ビットディジタルΔΣ信号を入力し、一対の信号を出力するスイッチ回路SW1〜SW(N)、出力された一対の信号を入力して一対の信号として出力するインピーダンス素子IMP1〜IMP(N)、出力された一対の信号の一方を入力する反転入力端子OPAa、他方を入力する非反転入力端子OPAb、1ビットディジタルΔΣ信号をディジタルアナログ変換した信号を出力する出力端子102を備える演算増幅器OPA、反転入力端子OPAaと出力端子102とに接続されるインピーダンス素子IMP0−N、非反転入力端子OPAbに一端が接続され、他端に基準電圧が与えられるインピーダンス素子IMP0−Pによりディジタルアナログ変換器を構成する。

(もっと読む)

データドライバーのデジタルアナログ変換装置及びその変換方法

【課題】本発明は、液晶表示装置用データドライバーのデジタルアナログ変換装置及びその変換方法に関するものであり、より詳細には、電流伝送路制御とトランスコンダクタンスの割合調整を通じて下位ビットに該当する情報をアナログ信号に変換するデータドライバーのデジタルアナログ変換装置及びその変換方法に関するものである。

【解決手段】本発明によるデータドライバーのデジタルアナログ変換器によれば、デルタ電流生成部と出力バッファー増幅部との間のトランスコンダクタンスの割合を調整して、電流伝送路を制御することを通じて下位ビットに該当する映像データをアナログ信号に変換させることで、データドライバーの面積を画期的に減少させることができるだけでなく、共通モード帰還回路を使わなくてデルタ電流生成部を具現することができて追加的な面積増加がないという長所がある。

(もっと読む)

ディジタルアナログ変換器

【課題】低消費電力で、素子の相対的なばらつきによって発生する信号歪みやSNR劣化が少ないディジタルアナログ変換器を提供する。

【解決手段】1ビットレジスタ103と、1ビットディジタルΔΣ信号及び、1ビットレジスタ103の出力信号を一対の入力信号とし、一対の出力信号を出力するスイッチ回路104、この一対の出力信号を入力し、ノイズを除去して第1出力信号、第2出力信号を出力する2端子対インピーダンス素子105、反転入力端子108a、非反転入力端子108b、出力端子108cを有する演算増幅器108、反転入力端子108aと出力端子108cとの間に接続されるインピーダンス素子106、非反転入力端子108bに一端が接続され、他端に基準電圧が与えられるインピーダンス素子107によってディジタルアナログ変換器を構成する。

(もっと読む)

AD変換装置および制御方法

【課題】ノイズを低減する。

【解決手段】アナログの入力信号に応じた差動の入力電圧を発生する差動増幅器と、比較データに応じた差動の比較電圧から差動の入力電圧を減算した差動の出力電圧を出力する電荷再配分型の差動DA変換器と、差動の出力電圧における、ポジ側出力電圧とネガ側出力電圧とを比較するコンパレータと、コンパレータの比較結果に基づき差動の出力電圧をほぼ0とする比較データを特定して、特定した比較データを出力データとして出力する制御部と、差動増幅器のコモン電位および差動DA変換器のコモン電位の少なくとも一方を、コンパレータのコモン電位の目標値に応じて設定する設定部と、を備えるAD変換装置を提供する。

(もっと読む)

81 - 100 / 534

[ Back to top ]