Fターム[5J022CF02]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 増幅器(差動・演算) (534)

Fターム[5J022CF02]に分類される特許

61 - 80 / 534

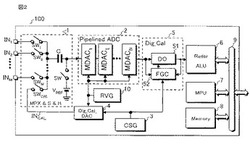

半導体集積回路およびその動作方法

【課題】車載用ミリ波レーダ装置に搭載されA/D変換器とMPUを内蔵する半導体集積回路で、内蔵A/D変換器のチップ占有面積を削減して、内蔵A/D変換器の分解能を改善する。

【解決手段】半導体集積回路で、レーダ装置の複数の受信信号は、単一のデジタル補正型A/D変換器によってA/D変換される。単一のA/D変換器のデジタル補正型A/D変換器は、受信インターフェース1のマルチプレクサから出力される複数の受信信号を順次にA/D変換するフォアグラウンドデジタル補正型A/D変換器2、3、4、5である。単一のA/D変換器は、従属接続された複数の変換器MDAC1…Nを有するパイプライン型A/D変換器2を含む。半導体集積回路は、デジタル補正のための補正用信号生成部3とデジタル補正用D/A変換器4とデジタル補正部5を具備する。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスのチャネル信号が第1、第2信号で構成される場合に第1、第2信号の差分に対応する信号の精度の高いA/D変換を実現する集積回路装置等の提供。

【解決手段】集積回路装置は、センサーデバイスからの第1信号SG1が第1期間において入力され、第1信号SG1とペアーとなってセンサーデバイスのチャネル信号を構成する第2信号SG2が第2期間において入力され、第1信号SG1と第2信号SG2の差分に対応する信号を出力する増幅回路と、増幅回路の出力信号についてのA/D変換を行うA/D変換器を含む。増幅回路は、増幅回路が有する演算増幅器のオフセット電圧をキャンセルするスイッチドキャパシター回路により構成される。

(もっと読む)

二重積分型AD変換器および積分型AD変換器

【課題】本発明によれば、クロックパルス発生器の周波数が比較的低い場合にも、自身の積分回路のコンデンサの静電容量を、ICに内蔵可能となる程度に小さくすることが可能な二重積分型AD変換器を実現することができる。

【解決手段】本発明は、測定電圧またはこの測定電圧と逆極性の標準電圧のいずれかを選択し出力するセレクタと、このセレクタの出力を積分する積分回路と、クロックパルスを発生するクロックパルス発生器とを有し、前記積分回路の積分値が予め定められた値となるまでの時間を前記クロックパルスで計測し、計測した時間に基づいてアナログデジタル変換する二重積分型AD変換器において、前記クロックパルスに基づいてこのクロックパルスよりもパルス幅の小さい微小パルスを生成する微小パルス発生回路と、前記セレクタと前記積分回路との間に設けられ、前記微小パルスを入力し、そのパルス幅に相当する期間においてのみ前記セレクタと前記積分回路とを接続するスイッチと、を備えたことを特徴とする。

(もっと読む)

スイッチトキャパシタ型回路及びそれを用いたAD変換回路

【課題】消費電力を増大させることなく、高精度な基準電圧の下で動作するスイッチトキャパシタ型回路を提供する。

【解決手段】(1)第1のスイッチトキャパシタ(スイッチ11〜13及び帰還容量Cf)とサンプリング容量Csと増幅回路100とを含むスイッチトキャパシタ型増幅回路110aと、(2)スイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給する基準電圧回路110bとを備え、基準電圧回路110bは、基準電圧Vrefを出力するバッファ回路1と、バッファ回路1の出力端子111とスイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給するための基準電圧入力端子112との間に接続された第2のスイッチトキャパシタ(スイッチ10及び容量Cc)とを有する。

(もっと読む)

デジタルアナログ変換回路及び表示ドライバ

【課題】CMOS化するスイッチ数、ゲート幅増加を抑制し、面積増加を抑制可能とする、デジタルアナログ変換器、データドライバ、表示装置を提供。

【解決手段】参照電圧集合体80は第1、第2の参照電圧群81、82を含み、デコーダ100は、mビットのデジタル信号の上位側(m−n)ビットの信号を共通に入力する第1乃至第2のサブデコーダ部10、20と、前記mビットのデジタル信号の下位側nビットの信号を共通に入力する第3乃至第4のサブデコーダ部30、40と、を備え、前記第1及び第3のサブデコーダ部10、30は第1導電型のトランジスタよりなり、前記第2及び第4のサブデコーダ部20、40は第2導電型のトランジスタよりなり、増幅回路50は入力に受けた電圧を、予め定められた重み付けで平均し、前記重み付け平均した電圧、前記mビットのデジタル信号に対応したアナログ信号として出力端子51から出力する。

(もっと読む)

DA変換回路

【課題】ラダー抵抗回路の各抵抗の抵抗値を時間的に平均化できるようして、変換特性の劣化を軽減する。

【解決手段】入力ラインが4ビット、出力ラインが6ビットで、入力ラインをシフトせず又はその並びのままでMSB方向に所定ビット数だけシフトして出力ラインに接続するシフト回路200と、シフト回路200のLSB側の4ビットにバッファ301が接続され、MSB側の2ビットにトライステートバッファ302が接続されたバッファ回路300と、バッファ回路300の出力側に接続されたR−2R型のラダー抵抗回路400と、出力端子600をと有する。シフト回路200は、出力ラインのうちの入力ラインが接続されたラインよりもLSB側のラインを“0”に設定し、且つ出力ラインのうちの入力ラインが接続されたラインよりもMSB側のラインを任意の値に設定する。バッファ回路300は、出力ラインのうちの入力ラインが接続されたラインよりもMSB側のラインに対応するトライステートバッファの出力がハイインピーダンスに設定される。

(もっと読む)

抵抗の誤差訂正を用いるコンパレータベースのバッファ

【課題】スイッチトキャパシタの負荷を有する高利得増幅器の駆動容量を高めるコンパレータベースのバッファ方法及びシステムを提供することを目的とする。

【解決手段】電流源と、コンパレータと、スイッチと、サンプリングキャパシタと、オーバーシュート訂正抵抗を含む。充電経路内の抵抗及び訂正位相を使用する訂正の解決法は、電力消費を制約し、コンポーネントを最小化する一方で、出力電圧のオーバーシュートを低減する。Spectre(登録商標)シミュレーションは、本発明の効果を確証する。

(もっと読む)

スイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システム

【課題】精度および高速性能を損なうことなくアンプシェア動作を実現可能なスイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システムを提供する。

【解決手段】複数のスイッチドキャパシタ回路210,220で共有される演算増幅器AMP11を有し、複数のスイッチドキャパシタ回路は演算増幅器の入力および出力と切り離すように複数のスイッチが制御されて複数の容量で第1のアナログ信号をサンプリングするサンプルモードと、サンプリングした容量を演算増幅器の入力および出力と選択的に接続するように複数のスイッチが制御されて、演算増幅器のサンプルモードでサンプリングした信号と第2のアナログ信号との差分を2N倍に増幅するホールドモードとが相補的に設定され、サンプルモード時に演算増幅器の入力および演算増幅器の内部における電圧が固定されていないノードを共通電位にリセットするスイッチswrを有する。

(もっと読む)

アナログ−デジタル変換器

【課題】必要な分解能を達成しながらより低い電力を達成する引き続く要望がある。従って、電力をさらに低減するのは望ましい。従って、必要な分解能を達成しながらより低電力を達成すること。

【解決手段】アナログ入力信号をデジタル出力信号に変換するようにとなっている変換器200が、アナログ入力信号を受信するためにアナログ入力端子205、該アナログ入力端子に接続した冗長符号桁(RSD)段210、デジタル部分220を含む。RSD段は、該アナログ入力端子で該アナログ入力信号を受信するように構成され、第1クロックサイクルの第1半分中該アナログ入力信号からデジタル出力でビットの第1の数を生成するように構成され、第1クロックサイクルの第2半分中該アナログ入力端子でアナログ入力信号の残留フィードバック信号を供給するように構成され、第2クロックサイクルの第1半分中該残留フィードバック信号からデジタル出力でビットの第1の数よりも少ないビットの第2の数を生成するように構成される。

(もっと読む)

入力セレクタおよび信号処理回路

【課題】さまざまな入力形式の信号に柔軟に適応可能な汎用性の高い入力セレクタを提供する。

【解決手段】第1抵抗R1〜第4抵抗R4は、それぞれの第1端子が対応する入力ポートPi1〜Pi4に接続される。第1スイッチSW1〜第4スイッチSW4はそれぞれ、対応する抵抗と第1演算増幅器10の反転入力端子の間に設けられる。第5スイッチSW5、第6スイッチSW6はそれぞれ、対応する抵抗と、第2演算増幅器12の反転入力端子の間に設けられる。第5抵抗R5および第7スイッチSW7は第1演算増幅器10の出力端子と第2演算増幅器12の反転入力端子の間に直列に設けられる。第6抵抗R6は第1演算増幅器10の出力端子と反転入力端子の間に設けられ、第7抵抗R7は第2演算増幅器12の出力端子と反転入力端子の間に設けられる。

(もっと読む)

アナログ信号に対応したディジタル信号を生成する方法

【課題】一サンプリング当たりにA/D変換時間を短縮すること可能なアナログディジタル変換器を提供することを目的とする。

【解決手段】A/D変換ステージ101でのサンプル値Rに変換操作Bを施して変換結果D3を生成しこの変換結果D3にA/D変換ステージ103でサンプリング操作Aを施す。A/D変換ステージ105でのサンプル値に変換操作Bを施して変換結果D4を生成しこの変換結果D4にA/D変換ステージ107でサンプリング操作Aを施す。A/D変換ステージ107でのサンプル値に変換操作Bを施して変換結果D5を生成しこの変換結果D5にA/D変換ステージ101でサンプリング操作Aを施す。A/D変換ステージ103でのサンプル値に変換操作Bを施して変換結果D6を生成しこの変換結果D6にA/D変換ステージ105でサンプリング操作Aを施す。

(もっと読む)

アナログディジタル変換器およびアナログ信号に対応したディジタル信号を生成する方法

【課題】一サンプリング当たりにA/D変換時間を短縮すること可能なアナログディジタル変換器を提供することを目的とする。

【解決手段】A/D変換ステージ101でのサンプル値Rに変換操作Bを施して変換結果D3を生成しこの変換結果D3にA/D変換ステージ103でサンプリング操作Aを施す。A/D変換ステージ105でのサンプル値に変換操作Bを施して変換結果D4を生成しこの変換結果D4にA/D変換ステージ107でサンプリング操作Aを施す。A/D変換ステージ107でのサンプル値に変換操作Bを施して変換結果D5を生成しこの変換結果D5にA/D変換ステージ101でサンプリング操作Aを施す。A/D変換ステージ103でのサンプル値に変換操作Bを施して変換結果D6を生成しこの変換結果D6にA/D変換ステージ105でサンプリング操作Aを施す。

(もっと読む)

A/D変換ステージおよびA/D変換ステージにおける変換誤差を示す信号を生成する方法

【課題】一サンプリング当たりにA/D変換時間を短縮すること可能なアナログディジタル変換器を提供することを目的とする。

【解決手段】A/D変換ステージ101でのサンプル値Rに変換操作Bを施して変換結果D3を生成しこの変換結果D3にA/D変換ステージ103でサンプリング操作Aを施す。A/D変換ステージ105でのサンプル値に変換操作Bを施して変換結果D4を生成しこの変換結果D4にA/D変換ステージ107でサンプリング操作Aを施す。A/D変換ステージ107でのサンプル値に変換操作Bを施して変換結果D5を生成しこの変換結果D5にA/D変換ステージ101でサンプリング操作Aを施す。A/D変換ステージ103でのサンプル値に変換操作Bを施して変換結果D6を生成しこの変換結果D6にA/D変換ステージ105でサンプリング操作Aを施す。

(もっと読む)

アナログデジタル変換用ランプ波発生器ユニット素子

【課題】傾きを段階的に増加したランプ波発生する新しいユニット素子のアプローチを提案する。

【解決手段】ランプ波発生のための方法は、基準電源を提供する段階と、加算増幅器を提供する段階と、前記基準電源と加算増幅器との間に並列に接続されたn個のスイッチトキャパシタ素子を提供する段階と、まず動作状態となった各スイッチトキャパシタ素子に電荷を充電し、次に繰り返し処理におけるタイムスロットの固定整数回の各回ごとに前記動作状態となったスイッチトキャパシタ素子の電荷総量を測定するため所定の数のスイッチトキャパシタ素子を選択的に動作させる段階とを具備しており、前記所定の数は、0からnの範囲となっている。

(もっと読む)

パイプライン・AD変換回路

【課題】入力範囲に応じて精度の異なるパイプライン・AD変換回路の実現。

【解決手段】直列に接続された複数のアナログ/デジタル変換ユニット30,37と、複数のアナログ/デジタル変換ユニットのサブ変換結果から、入力アナログ信号Vinのデジタル変換値Doutを算出するデジタル演算回路38と、を備え、各アナログ/デジタル変換ユニット30は、サブAD変換器32と、アナログ入力信号からサブAD値に応じたアナログ減算信号を減算して残差信号を発生し、残差信号を増幅して出力する増幅DA変換器39と、を備えるパイプライン・AD変換回路であって、初段のサブAD変換器32は、入力範囲-Vref,Vrefを少なくとも4個以上のサブ範囲に分割して、入力アナログ信号がいずれのサブ範囲に入るかを判定し、4個以上のサブ範囲の大きさが異なる。

(もっと読む)

D/A変換装置

【課題】超高精度を決める基本項目を、計測制御システムを用いることなく、自律的に校正できるD/A変換技術を提供する。

【解決手段】周辺回路は、D/A変換器の出力を所望のアナログ量に変換するA/A(アナログ/アナログ)変換回路と、A/A変換回路の出力を減衰する減衰回路と、標準信号源とを備えている。D/A変換器は、nビットのD/A変換を行う上位D/A変換回路、及びmビットのD/A変換を行う下位D/A変換回路を有するD/A変換基本部と、その出力信号を調整する補正用D/A変換器、及び補正用D/A変換器の出力を所望のアナログ信号に変換する回路から構成する補正部と、A/A変換回路の出力と、減衰回路の出力と、標準信号源の出力の中から2つの信号を時分割制御にて選択し、選択した2信号の差を交流増幅して大小判定する判定部と、判定部の差信号を極小にする制御部とを備えている。

(もっと読む)

A/D変換器およびそれを使用した受信装置

【課題】A/D変換器を構成するサンプル/ホールド回路、コンパレータを低消費電力化すること。

【解決手段】アナログ入力信号をクロック信号に応答してサンプルしてホールドするサンプル/ホールド回路(SHC)とその回路からのホールド出力信号の信号レベルを弁別するコンパレータ(COP)を含む。コンパレータは、サンプル/ホールド回路からのホールド出力信号を増幅するプリアンプ(AMP)、プリアンプから生成される差動出力信号をラッチするラッチ回路(LCH)、プリアンプから生成される差動出力信号のレベル差に応答してプリアンプのバイアス電流の電流値を制御するバイアス制御回路(BCC)を含む。差動出力信号のレベル差が小さい時にはバイアス制御回路はプリアンプのバイアス電流を大きな電流値に制御して、差動出力信号のレベル差が大きい時にはバイアス制御回路はプリアンプのバイアス電流を小さな電流値に制御する。

(もっと読む)

サンプルホールド回路及びA/D変換装置

【課題】本発明は、サンプルホールド回路及びA/D変換装置に係り、ホールド出力を行ううえでオペアンプの入力オフセット分の除去性能を向上させることにある。

【解決手段】ホールド出力を行うオペアンプを備えるサンプルホールド回路において、所定複数の異なるタイミングで入力電圧をサンプリングするサンプリングキャパシタと、サンプリングキャパシタでサンプリングされた各入力電圧を加減算する加減算手段と、加減算手段により各入力電圧が加減算された後、該加減算により得られる電圧に含まれるオペアンプの入力オフセット電圧分を除去するオフセット電圧除去手段と、を備え、オペアンプは、オフセット電圧除去手段によりオペアンプの入力オフセット電圧分が除去された電圧をホールドして出力する。

(もっと読む)

デジタル−アナログ変換器及びデジタル−アナログ変換装置

【課題】 簡単な回路構成で、スイッチのオン抵抗値によるアナログ出力信号の歪みやノイズの発生を防止することができるデジタル−アナログ変換器を提供する。

【解決手段】 サンプリング容量素子Ciの一方の端子と対応する入力端子Diとの接続及び切断並びにサンプリング容量素子Ciの他方の端子と第1基準電圧源B1との接続及び切断を切り替える第1のスイッチユニットSU1と、第1のスイッチユニットSU1の切り替えにおける切断及び接続に応じて、サンプリング容量素子Ciの他方の端子と演算増幅器2の反転入力端子との接続及び切断、複数のサンプリング容量素子Ciの一方の端子の相互の接続及び切断、並びに一方の端子が相互に接続されたサンプリング容量素子Ciの電圧に応じた電圧を演算増幅器2の出力端子に出力する電気経路の閉成及び開放を切り替える第2のスイッチユニットSU2と、電気経路に設けられた抵抗素子Rsとを備えている。

(もっと読む)

スイッチドキャパシタ利得段

【課題】出力電流を増やすことなくセトリング時間を短縮することが可能なスイッチドキャパシタ利得段、及び、これを用いたパイプライン型A/D変換器を提供する。

【解決手段】スイッチドキャパシタ利得段は、第1フェーズではサンプル/ホールド回路(キャパシタCf及びCs、並びに、スイッチSWa〜SWc)を用いて入力電圧Vinのサンプリングを行い、第2フェーズでは増幅器(AMP1及びAMP2)を用いてサンプリング済み入力電圧の増幅出力を行うスイッチドキャパシタ利得段において、入力電圧Vinのサンプリング動作時にのみ、前記増幅器のミラー補償を行うミラー補償部(Cm、SWg)を有する構成とする。

(もっと読む)

61 - 80 / 534

[ Back to top ]