Fターム[5J022CF02]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 増幅器(差動・演算) (534)

Fターム[5J022CF02]に分類される特許

121 - 140 / 534

パイプラインAD変換装置

【課題】カレントミラー回路の補償回路を工夫して、回路規模増を伴うことなく、nビッ

トのDA変換器や、AD変換器等の基準電流を発生できるようにすると共に、残差アンプ

の温度に対する安定度を改善できるようにする。

【解決手段】nビットAD変換出力をデジタルアナログ変換して、残差アンプU11にア

ナログ信号を出力するnビットDA変換器DA1と、この出力をデジタルアナログ変換し

て、残差アンプU12にアナログ信号を出力するnビットDA変換器DA2とに基準電流

を供給する基準電流発生部506を備え、所定の基準電流から、U11の温度ドリフトに

トラッキングした基準電流を生成するカレントミラー回路111と、この出力電流をDA

C及びADCの基準電流として仲介するカレントミラー回路124と、この基準電流から

、U12の温度ドリフトにトラッキングした基準電流を生成するカレントミラー回路13

1とを有するものである。

(もっと読む)

A/D変換方法及び装置

【課題】パルス遅延回路を用いてアナログ入力信号をA/D変換する装置において、変換式を用いることなく、入出力特性を理想特性(直線)に設定できるようにする。

【解決手段】パルス遅延回路と符号化回路とで構成されるTAD(時間A/D変換装置)を備えた装置において、オフセット電圧Voffにアナログ入力信号Vinを加えた第1電圧と、オフセット電圧Voffからアナログ入力信号Vinを減じた第2電圧(Voff−Vin)とを生成し、各電圧をTADでA/D変換し、そのA/D変換結果DT1,DT2の差をとることでA/D変換データDT0を生成する。また、この装置には、基準電圧をA/D変換したA/D変換結果を基準データとして記憶するラッチ回路を設け、A/D変換対象となるアナログ入力信号Vinの入力時には、A/D変換結果をラッチ回路に記憶された基準データにて除算することにより、温度補正する。

(もっと読む)

D−A変換回路

【課題】ビット数の増加に伴うスイッチ数の増加を抑制し、面積の増大を防止することができるD−A変換回路を提供すること。

【解決手段】本発明の一態様に係るD−A変換回路は、抵抗ストリング190、第1選択回路191、アンプ回路192、第2選択回路193、第3選択回路194を備える。抵抗ストリング190は、上限電圧、下限電圧、中間電圧を含む複数の電圧を生成する。第1選択回路191は、下位ビットに応じて、複数の電圧のうちの中間電圧以下の第1電圧を選択して出力する。第2選択回路193は、上位ビットに応じて、複数の電圧のうちの中間電圧以上の電圧又は低位電源電圧のいずれかを選択して第2電圧を出力する。第3選択回路194は、上位ビットに応じて、下限電圧又は低位電源電圧を選択して第3電圧を出力する。アンプ回路192は、第1電圧と第2電圧とを加算し、第3電圧を減算して、出力電圧を出力する。

(もっと読む)

D/Aコンバータおよびその動作テスト方法

【課題】

本発明は、高精度な電圧計が不要であり、1chのD/Aコンバータであってもテスト時間の短縮が可能なD/Aコンバータを提供することを目的とする。

【解決手段】

開示のD/Aコンバータの一形態は、入力されたデジタルコード信号をD/A変換して出力するD/Aコンバータであって、直列に接続された複数の抵抗によって入力電圧を複数の分圧比で分圧し、前記デジタルコード信号に応じてオン/オフ制御される複数のスイッチを介して、各分圧電圧のうち1つの電圧をアナログ信号として出力するD/A変換回路部を備え、前記D/A変換回路部は、前記入力電圧として入力されるテスト信号に対応する前記アナログ信号を出力すると共に、該テスト信号が入力される際の前記デジタルコード信号を出力することを特徴とする。

(もっと読む)

AD変換回路

【課題】低入力容量を維持しながら、誤判定の発生を低減したAD変換回路の実現。

【解決手段】入力信号の電圧Vinp,Vinnと、電圧値が順番に異なる複数の基準電圧VrpN,VrnNとのそれぞれの差電圧を増幅し、複数の基準電圧の電圧値の順番に対応した順番を有する複数の初段増幅器と、複数の初段増幅器の隣接する2個の初段増幅器54N,54(N+2)の出力の差電圧を増幅する1個以上の2段目増幅器56(N+1)と、複数の初段増幅器および1個以上の2段目増幅器の出力から、入力信号の電圧の複数の基準電圧に対するレベルを示す値を演算するエンコーダ53と、を備える。

(もっと読む)

半導体集積回路および液晶駆動回路

【課題】ラインバッファ、第一切替え器、DA変換器、第二切替え器、及び、増幅器を直列に構成したチャンネルを多数備える回路において、いずれかのチャンネルの異常DA変換器を、冗長用のDA変換器50により救済する。

【解決手段】いずれかのDA変換器が異常と判定されたときは、第一切替え器及び第二切替え器により、その異常と判定されたDA変換器から冗長用のDA変換器50側にDA変換器の接続を所定チャンネル分、例えば1チャンネル分シフトさせ、異常DA変換器を回避することができるようにした。

(もっと読む)

出力回路、信号線駆動回路および表示装置、並びに電子機器

【課題】差動対数を削減でき、回路構成の増大、消費電流の増加を防止することができ、素子サイズ(レイアウト面積)の削減を図ることが可能な出力回路、信号線駆動回路および表示装置、並びにそれを用いた電子機器を提供する。

【解決手段】差動対段210,220は、ソース同士が接続された2つのトランジスタにより形成された差動対トランジスタと、差動対トランジスタに接続された電流源と、を含み、2つのトランジスタのうちの一方のトランジスタのドレインが出力端子として他の差動対の一方のトランジスタのドレインと接続され、一方のトランジスタのゲートに2つの基準電圧のうちの一方の基準電圧が供給され、他方のトランジスタのゲートに出力電圧が帰還され、能動負荷切り替え部230は、制御信号CTLに応じて、(2n−1)個の能動負荷を、n個の差動対段に対して重み付けして選択的に割り付けて分圧動作を行わせる。

(もっと読む)

差動チョッパ型コンパレータ及びそれを備えたA/D変換回路

【課題】従来の差動チョッパ型コンパレータは、精度の高い比較結果を出力することができないという問題があった。

【解決手段】本発明にかかる差動チョッパ型コンパレータは、入力信号電圧Vinと参照電圧Vrefとを比較する。そして、容量C1と、容量C2と、差動増幅回路5を有する差動増幅部102とを備える。容量C1の一端に、入力信号電圧Vinと参照電圧Vrefのいずれか一方が第1のスイッチ部100を介して印加され、容量C2の一端に、固定電圧Vfixが第2のスイッチ部101を介して印加される。差動増幅回路5の非反転入力端子または反転入力端子の一方が容量C1の他端に、非反転入力端子または反転入力端子の他方が容量C2の他端に、それぞれ接続される。容量C1の一端から見た第1のスイッチ部100側のインピーダンスと、容量C2の一端から見た第2のスイッチ部101側のインピーダンスとが実質的に同一である。

(もっと読む)

容量アレイ回路、およびアナログデジタル変換器

【課題】柔軟性の高い、コモンモード電圧の補償方法を実現したい。

【解決手段】複数の正側の入力容量(Cs1p、Cs2p、・・・)は、複数の差動入力信号の、正側の複数の入力信号をそれぞれ並列に受ける。正側の調整容量Cxpは、コモンモード電圧を調整するための正側の電圧を受ける。複数の正側の入力容量(Cs1p、Cs2p、・・・)および正側の調整容量Cxpのそれぞれの出力端子が一つに結合される。複数の負側の入力容量(Cs1m、Cs2m、・・・)は、複数の差動入力信号の、負側の複数の入力信号をそれぞれ並列に受ける。負側の調整容量Cxmは、コモンモード電圧を調整するための負側の電圧を受ける。複数の負側の入力容量(Cs1m、Cs2m、・・・)および負側の調整容量Cxmのそれぞれの出力端子が一つに結合される。

(もっと読む)

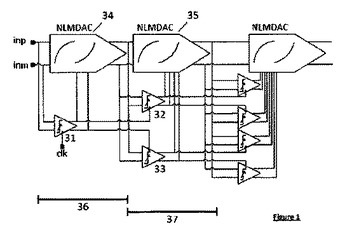

インターリーブ型パイプライン型バイナリーサーチA/D変換器

本発明は、入力信号を所定の複数の閾値のうちの少なくとも異なる2つと比較するための調整可能な上記複数の閾値を有する複数の比較手段と、複数の増幅回路とを備えたアナログ入力信号をデジタル信号に変換するためのパイプライン型アナログからデジタルへの変換器(ADC)であって、上記複数の比較手段は階層的ツリー構造を形成するように設けられ、上記階層的ツリー構造は複数の階層的レベルを有し、上記階層的レベルのうちの少なくとも1つが上記複数の増幅回路のうちの少なくとも1つの増幅回路と関連し、上記少なくとも1つの増幅回路は次の階層的レベルにおいて少なくとも1つの比較手段の入力を生成し、上記複数の階層的レベルは先行する階層的レベルの非線形歪みが除去されるように、前の階層的レベルの出力に従って上記調整可能な閾値を設定するための手段を備えたパイプライン型ADCに関する。  (もっと読む)

(もっと読む)

電圧出力装置

【課題】複数の出力部を並列接続して出力電流を増加させる構成の電圧出力装置では、各出力部の出力電流を均一化するために、出力側に抵抗を挿入しなければならない。このため、この抵抗によって電力損失が増加し、また発熱が発生するという課題があった。また、急激な負荷変動に対応するために出力側に抵抗を挿入することがあるが、この抵抗によって電力損失や発熱が発生するという課題があった。本発明はこのような課題を解決することを目的にする。

【解決手段】各出力部内に出力電流を検出する電流検出部を設け、この電流検出部の出力と入力信号を加算して、電流が増加すると出力電圧が低下するようにした。また、全出力部内の電流検出部の出力信号を加算し、この加算信号を各出力部の入力信号供給するアンプに帰還するようにした。電流検出部に用いる抵抗は抵抗値が小さいものを用いることができるので、電力損失や発熱を増加させることなく出力電流を均一化でき、かつ負荷変動に対処する出力抵抗を模擬できる。

(もっと読む)

アナログデジタル変換装置

【課題】アナログ信号を精度よく高分解能でデジタル信号に変換するアナログデジタル変換装置を提供する。

【解決手段】アナログデジタル変換装置が、アナログ入力信号Vinに応じてパルス信号を遅延させる複数の遅延ユニット1が接続されたパルス遅延回路101と電圧VCKに応じて基準クロックCK0を遅延させ、一定間隔の位相に遅延させた複数のサンプリングクロックCKを出力するクロック発生回路201と、サンプリングクロックCKに同期してパルス信号の位置を検出し、数値データを出力する複数のパルス位置数値化部103と、クロック発生回路201の遅延ユニットにおける遅延時間が遅延ユニット1の遅延時間をパルス位置数値化部103の個数で除算した値と等しくなる電圧VCKを生成する昇圧回路202と、全ての数値データを加算し、加算結果を出力する加算部104と、を備える。

(もっと読む)

スイッチ損失を改善するための回路アーキテクチャを有するデジタル/アナログ変換器

【課題】従来の電圧モードDACよりも、線形性が改善され、スイッチエリアの全体が小さく、そして寄生電気抵抗に鈍感なデジタル/アナログ変換器(DAC)を提供する。

【解決手段】デジタル/アナログ変換器(DAC)は、それぞれハイ基準電圧またはロー基準電圧のそれぞれに結合された第1入力をそれぞれ有するオペアンプ対を具備する。前記DACは、複数のスイッチ制御されるセルを具備し、それぞれ、抵抗器および2つのフォース/センススイッチ対を具備する。それぞれのセル内において、4つの全てのスイッチは、抵抗器と結合されている。第1フォーススイッチは、第1オペアンプの出力と結合されるとともに、結合されているセンススイッチは、第1オペアンプの反転入力に結合されている。第2フォーススイッチは、第2オペアンプの出力に結合されるとともに、結合されているセンススイッチは、第2オペアンプの反転入力に結合されている。

(もっと読む)

逐次比較型AD変換回路

【課題】逐次比較型AD変換回路において、見かけ上の変換速度を低下させることなく、比較回路でノイズを低減してAD変換精度を向上させる。

【解決手段】結合容量を介して縦続接続され複数の増幅段を備え入力アナログ電圧と比較電圧の大小を判定する比較回路と、該比較回路の判定結果を順次取り込んで保持するレジスタと、該レジスタの値を電圧に変換し前記比較電圧を生成するローカルDA変換回路とを備えた逐次比較型AD変換回路において、前記比較回路(11)の増幅段の出力端子に接続された負荷容量調整手段(16)と、負荷容量調整手段の容量値を変更する信号を生成する制御回路(15)とを設け、上位ビットを変換する際には負荷容量調整手段の容量値を小さくさせ、下位ビットを変換する際には前記負荷容量調整手段の容量値を大きくさせるようにした。

(もっと読む)

スイッチトキャパシタ回路及びそれを有するパイプライン型AD変換回路

【課題】

キャパシタの容量値の相対誤差の影響を抑えた変換回路と,それを有するパイプライン型AD変換回路を提供する。

【解決手段】

単位変換回路は,第1期間において,差動入力の差電圧が第1のキャパシタCSFに印加され,第2期間において,アンプAMPの入出力間に第1のキャパシタCSFが接続され,差動入力に応じた参照電圧とアンプ入力との間に第2のキャパシタCRが接続される。キャパシタ間に相対誤差が存在していても,AD変換誤差を抑制することができる。

(もっと読む)

並列補間型A/D変換器及びディジタル等化装置

【課題】分解能を上げることによる回路面積及び消費電力の増大を抑えた並列補間型A/D変換器を提供する。

【解決手段】m+1個(mは正の整数)の参照電圧VR1〜VRm+1(ただし、VR1<VR2・・・<VRm<VRm+1)を生成する参照電圧生成回路111と、参照電圧VR1〜VRm+1の各々と入力信号電圧との電圧差を増幅するm+1個の差動増幅器A1〜Am+1を有する差動増幅器列112と、各差動増幅器からそれぞれ生成される出力電圧セットを受け取る複数個の比較回路を含む動作回路113とを設ける。ここで、より重要な情報を含むアナログ信号成分を精度良く変換できるよう特定の範囲では回路ばらつき耐性を高め、重要でない情報成分を変換する範囲は回路ばらつき耐性を低くするように、参照電圧をVRk(kは2≦k≦m+1の整数)とするとき、参照電圧VRkのk値に応じて比較回路の個数を異ならせる。

(もっと読む)

全差動型スイッチトキャパシタフィルタ回路およびA/Dコンバーター

【課題】入力インピーダンスが高く、ノイズや歪みの少ない出力信号を得ることのできる全差動型スイッチトキャパシタフィルタ回路およびA/Dコンバーターを提供する。

【解決手段】クロック生成回路11bから出力されるクロック信号φの1周期あたりでオペアンプAMP2がサンプリングキャパシタC1a,C2aに充電する電荷量(トランスファーフェーズにおけるサンプリングキャパシタC1a,C2aから積分キャパシタC1b,C2bに転送する電荷量)を変化させないと共に、1周期あたりの充電回数を1/2(1回)にすることで、SCF回路11aの入力インピーダンスを2倍にする。

(もっと読む)

DA変換回路

【課題】出力電圧のリニアリティの調整精度を低下させることなく、オペアンプを用いた増幅回路の入力抵抗値、帰還抵抗値を低減して雑音に対する耐性を向上させることができるDA変換回路を提供する。

【解決手段】DA変換回路は、オペアンプと、オペアンプの出力端子とグランドとの間に直列に接続された、複数の第1の抵抗素子と入力抵抗からなる抵抗ラダーと、一方の端子が対応する第1の抵抗素子の一方の端子と接続され、他方の端子が対応する第1の抵抗素子の他方の端子と第2の抵抗素子を介して接続された少なくとも1つのスイッチと、各々のスイッチのオン/オフを切り替える制御信号を出力するコントロール回路とを備える。オペアンプの一方の入力端子が基準電圧に接続され、他方の入力端子が入力抵抗のグランドに接続された端子とは逆の端子に接続され、オペアンプから制御信号の状態に対応した定電圧が出力される。

(もっと読む)

データ処理装置及びデータ処理システム

【課題】被測定電圧をAD変換する場合に増幅回路で増幅して変換したときと増幅回路を用いずにダイレクト変換したときとで、変換データに連続性を確保する。

【解決手段】DA変換回路、増幅回路、AD変換回路を用いてAD変換動作を制御する制御回路(2)は、前記DA変換回路から出力したアナログ信号を直接及び期待ゲインを2n(nは正の整数)とする前記増幅回路で増幅してAD変換回路で変換した結果から前記増幅回路のゲインとオフセットを演算し、ビット精度を高くすべき被計測アナログ信号に対しては前記増幅回路で増幅してAD変換回路で変換し、変換結果から前記オフセットを減算し、減算結果に、前記演算で得られたゲインに対する前記期待ゲインの比率を乗算してゲインの誤差を相殺し、誤差が相殺されたデータに基づいて、異なるビット精度のデータ間の連続性を保証するようにビット拡張された変換データを取得する処理を行なう。

(もっと読む)

補間型A/D変換器

【課題】増幅動作の際の消費電力を低減し、かつ、増幅器のゲインを調整することができる補間型A/D変換器を得ること。

【解決手段】本発明にかかる補間型A/D変換器は、基準電圧発生回路101、アナログ信号入力回路102、複数のプリアンプAMPを有するプリアンプ群103及び複数の抵抗器104aを有する補間回路104を少なくとも備える。プリアンプ群103には、基準電圧発生回路101から基準電圧Vrが、アナログ信号入力回路からアナログ信号AINが入力される。補間回路104は、プリアンプ群103の出力信号を補間した補間信号を出力する。プリアンプAMPは、アナログ信号AINと基準電圧Vrとの差電圧ΔVが規定値よりも小さい場合には差電圧ΔVを増幅し、大きい場合には電流を遮断する。複数の抵抗器104aは、隣接するプリアンプAMP間に直列に接続される。

(もっと読む)

121 - 140 / 534

[ Back to top ]